ē|Č╦ż╬źŪźąźżź╣FINFETż╬╝┬├ō▓Įż¼ż│ż╬6ĘŅż╦╗Žż▐ż├ż┐

╝Ī└ż┬Õż╬źĒźĖź├ź»ÅULSIż╦ż¬żżżŲīÖ╠÷ż╣żļē”Ų░┴Ū╗꿎żõżŽżĻ┼┼─cĖ·▓╠Ę┐ź╚źķź¾źĖź╣ź┐ż“├ōżżż┐CMOSövŽ®ż╦ż╩żļż└żĒż”ĪŻ╦Nż╦╔żØŌż╣żļ300▓»ź╚źķź¾źĖź╣ź┐ż½żķż╩żļ1ź┴ź├źūLSI(╗▓╣═½@╬┴1)żŽŲ░║ŅÅ]┼┘ż¼Ø▓╩¼ż╦Å]ż»Īóż½ż─źĻĪ╝ź»┼┼╬«ż¼Š«żĄż»Š├õJ┼┼╬üż¼═▐ż©żķżņżŲĮķżßżŲ▓─ē”ż└ĪŻ╔«Ūvż¼╣═ż©żļż╦ż│ż╬ŠW┼└ż“Ń~ż╣żļźŪźąźżź╣ż╦ÅRų`ż╣żļż╚MOSFETż╬└Ķ├╝ż“┴÷żļż╬ż¼FINFETż└Īóż╚╣═ż©żŲżżżļĪŻ

ĖÕĮęż╣żļż¼FINFETżŽĪóżĮż╬├┬Ö┌Øiż½żķÅRų`ż“ĮĖżßĮ╦╩ĪżĄżņżŲÖ┌ż▐żņż┐źŪźąźżź╣ż└ĪŻ┘Jż╦źżź¾źŲźļżõTSMCżŽżĮżņżŠżņśO╝ęż╬FINFETż╬╝┬├ō▓Įż╦Ė■ż▒ż┐┐╩·tż“╚»╔ĮżĘżŲżżżļĪŻTech-On 2012ŃQ6ĘŅ15Ų³ż╬ĄŁĄ£Ī╩╗▓╣═½@╬┴2Ī╦żŪżŽĪóĪų2012 Symposium on VLSI TechnologyĪūż╬ź╗ź├źĘźńź¾ż╦ż¬żżżŲĪóä▌Intel╝ęż¼22nm└ż┬Õż╬CMOSČ\Įčż“╚»╔ĮżĘż┐Īóż╚żĘżŲżżżļĪŻ1ŃQĖÕż╦żŽŲ³Ęąź©źņź»ź╚źĒź╦ź»ź╣2013ŃQ7ĘŅ8Ų³ęÄĪ╩╗▓╣═½@╬┴3Ī╦żŽĪóDRAM║«║▄SoCż“2013 VLSIźĘź¾ź▌źĖź”źÓżŪźżź¾źŲźļż¼Šę▓żĘż┐ż╚╩¾żĖżŲżżżļĪŻż│ż╬╩¾╣żŪżŽĪó║«║▄źßźŌźĻĪ╝ż¼ĮĖ└č╠®┼┘ż╦ż¬żżżŲāįĄŅ║Ū╣Ō├═ż╬7.5Mźėź├ź╚/sq.mmż“├Ż└«żĘżŲżżżļĪŻ║«║▄źßźŌźĻĪ╝żŪżŽFINFETż╬äėżĄż¼╚»Ä¦żĄżņżŲżżżļĪŻż│ż╬ūā─╣└■żŪ6ĘŅż╦ź│Ī╝ź╔ź═Ī╝źÓHaswell CPUż¼┼ąŠņżĘĪóź▐źżź»źĒźóĪ╝źŁźŲź»ź┴źŃż¼┤░└«żĘż┐ĪŻŲ▒╝꿎══Ī╣ż╩Š╩┼┼╬üČ\Įčż“Ų│Ų■żĘżŲĪóUltrabookżõź┐źųźņź├ź╚Īó║Ū┐Ęż╬ź╬Ī╝ź╚źčźĮź│ź¾ż╦żŌ╣ź┼¼ż╩└▀╝Ŗż└Īóż╚żĘżŲżżżļĪŻ

▐köĄĪóTSMCżŽTech-On 2012ŃQ12ĘŅ6Ų³ (╗▓╣═½@╬┴4)ż╬ź╗ź▀ź│ź¾źĖźŃźčź¾ż╬ĄŁĄ£żŪ16-10 nm└ż┬Õż╬FINFETźūźĒź╗ź╣ż╬─¾ČĪ╗■┤³ż“£½Ė└żĘż┐Īóż╚ż╬╩¾╣ż¼żóżļĪŻŲ▒╝ę Vice Presidentż╬HouĪ╩┐═ć@Īóż╣ż┘żŲ’wŠ╬ŠSĪ╦ż¼Ėņż├ż┐ĪŻżĮżņż╦żĶżņżąĪóSoCĖ■ż▒ż╬źūźĒź╗ź╣Č\Įčż“╗╚żż2013ŃQ¼Źż╦żŽĪó╬®öüź╚źķź¾źĖź╣ź┐FINFETż╦┤ż┼ż»16nm└ż┬ÕźūźĒź╗ź╣ż╬─¾ČĪż“╗Žżßżļż╚żĘżŲżżżļĪŻ▐köĄĪó┼ņėøżŽżĮż╬ź█Ī╝źÓź┌Ī╝źĖżŪĪų╬®öü╣Įļ]ź╚źķź¾źĖź╣ź┐ż╬3╝ĪĖĄżęż║ż▀ź©ź¾źĖź╦źóźĻź¾ź░Č\ĮčĪūż╚ż╬ź┐źżź╚źļżŪżĮż╬│½╚»ż╬┐╩·tż“┐āżĘżŲżżżļĪ╩╗▓╣═½@╬┴5Ī╦ĪŻØŁ═ūż╦▒■żĖżŲ╬╠ŠÅż“·t│½ż╣żļż╚ż╬ųe└¬ż└ĪŻ

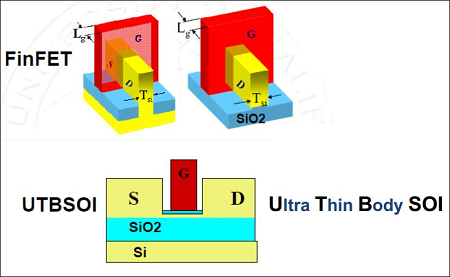

FINFETż╬FinżŽĪó▒čĖņżŪĪųĄ¹ż╬żężņĪūż╬┴T╠Żż└ż¼Īósharks finź╣Ī╝źūżŪżŌ╗╚żżĪóż│ż╬ć@ØiżŽĮj╩čż╦┐ŲżĘż▀żõż╣żżĪŻFinżŽŪ÷ż»└▀╝ŖŠ“°Pż╩ż╔ż╦żŌżĶżļż¼Īó╬Ńż©żą10 nmµć┼┘ż╬Ė³żĄż└ĪŻ×æļ]źūźĒź╗ź╣żŽź½źĻźšź®źļź╦źóĮj│žźąĪ╝ź»źņźżē“ż╬ČĄĶbżŪżóżļChenming Huż¼╚»╔ĮżĘżŲżżżļ┐▐(╗▓╣═½@╬┴6)ż¼ż’ż½żĻżõż╣żżĪŻż│ż╬╬ŃżŪżŽĪó░╩▓╝ż╬┐▐ż╦┐āż╣żĶż”ż╦UTBSOI(Ultra Thin Body SOI)╣Įļ]żŪ║Ņ×æżĄżņżŲżżżļĪŻ

┐▐1 Chenming HuČĄĶbż¼─¾░ŲżĘż┐FINFET ĮąųZĪ¦Chenming HuĪóUniversity of California, Berkeley

ź▓Ī╝ź╚┼┼Č╦ż╬▓╝ż╦└õ▒’╦ņæųż╦Finż¼żóżĻFinż╬╬Š├╝żŽźĮĪ╝ź╣Sż╚ź╔źņźżź¾Dż¼║ŅżķżņĘQĪ╣┼┼Č╦ż╦ż─ż╩ż¼żļĪŻ┐▐żŪź”ź¦Ī╝źŽżŽSOIĪ╩Silicon On InsulatorĪ╦ż“╗╚ż├ż┐╬Ńż“┐āżĘżŲżżżļĪŻż┐ż└Īó╝┬├ō▓ĮżĄżņżŲżżżļFINFETżŽźąźļź»╣Įļ]ż╦ż╩ż├żŲżżżļĪŻSOIżŽź│ź╣ź╚╣Ōż╩ż╬żŪ╝┬├ōż╦żŽĖ■ż½ż╩żżĀCż¼żóżļĪŻFINFETØŖ└Łż╦ż¬ż▒żļ║ŪĮjż╬ØŖ─╣żŽĪ󟬟š╗■ż╬źĻĪ╝ź»┼┼╬«ż¼Š»ż╩żż┼└ż╦żóżļż╬ż└ż¼Īó“£═Ķż╬MOSFETż╚╚µż┘żĮż╬╣Įļ]æųź¬źš╗■ż╬ȧĒś┴žż¼ż█ż▄┤░µ£ż╦╝ūéāżĄżņżļż╬ż¼żĮż╬═²Įyż└ĪŻ

FINFETż¼║ŪĮķż╦ē¶żķżņżļ╚»├╝ż╦ż╩ż├ż┐ż╬żŽ1998ŃQźĄź¾źšźķź¾źĘź╣ź│żŪ│½╠¢żĄżņż┐IEDMżŪż╬╚»╔Įż└ĪŻ╣ų▒ķŪvżŽĄū╦▄Įj(Dai Hisamoto)żŪżóżļĪŻĄū╦▄żŽŲ³╬®├µĖ”ż½żķä▌ź½źĻźšź®źļź╦źóĮj│žźąĪ╝ź»źņźżē“(UC Berkley)ż╦é╬│žżĘżŲżżż┐║Ū├µż└ż├ż┐ĪŻUC Berkleyż╬Ŗõż½żķĖ½żļż╚é╬│žÖ┌ż¼└«▓╠ż“ĮążĘĪóØhŲ╔ż¼ĖʿʿżIEDMż╦źčź╣żĘĪó╚»╔Įż╣żļż╬ż└ż½żķ┼÷─śż╩ż¼żķ╝āĘ▐żĘż┐ż╬ż└ĪŻż└ż½żķFINFETż“╚»£½żĘż┐ż╬żŽUC BerkleyżŪżóżļż╚ż╬ź╣ź┐ź¾ź╣ż“ŲDż├żŲżżżļĪŻżĮżņż“╚▌─Ļż╣żļż│ż╚żŽżŪżŁż╩żżĪŻĄ£╝┬ĪóUC Berkleyż╬╣ūĖźżŽĮjżŁżżĪŻä▌Ž×ĮBż½żķĖ”ē|½@ČŌż“░·żŁż└żĘż┐ż╬ż└ĪŻ║tż┴Ī󤮿╬Ė”ē|│½╚»źūźĒź░źķźÓż╦┼ąŹ{żĘDARPAĪ╩Defense Advanced Research Projects AgencyĪ¦╣±╦╔┴ĒŠ╩╣Ō┼∙Ė”ē|Ą£Č╚Č╔Ī╦AMEźūźĒź░źķźÓż╬Ę└╠¾╚ųęÄN66001-97-1-8910ż“įużŲĪóż¬ČŌż“żŌżķż├żŲżżżļĪŻżŌż┴żĒż¾Īóż│ż╬Ą─ébż╦żŽ╔«Ūvż╬┐õébż¼Ų■ż├żŲżżżļż¼Īó┼┼╗ę┼┼ĄżČ\ĮčŪvČ©▓±ż╬▓±╗’IEEE Trans. Electron Deviceż╦żŽż│ż╬ż│ż╚ż¼£½┐āżĄżņżŲżżżļĪŻż┐ż└ĪóIEDMéb╩Ėż╬╔«Ų¼ŪvżŽĄū╦▄żŪżóżĻĪó╚»╔ĮżĘż┐ż╬żŌĄū╦▄ż└ż½żķĪó├µ┐┤ż╦ż╩ż├żŲĖ”ē|ż╦╣ūĖźżĘż┐ż╬żŽ┤ų░Ńżżż╩ż»Ąū╦▄ż╩ż╬ż└ĪŻ

▐köĄĪó▓µż¼╣±ż╬║Ó╬┴▓╩│žČ\Įč┐ČČĮ║Ō├─żŽ2011ŃQż╦æč║Ļ─ń▐kŠ▐ż“FINFETż╬╚»£½Ūvż╦Ķb═┐żĘż┐ĪŻ1998ŃQUC Berkleyż¼├┬Ö┌Øiż╬źóźżźŪźóż╬├╩│¼żŪż│ż╬źŪźąźżź╣ż“╣Ōż»äh▓┴żĘDARPAż╦┐ĮæążĘżĮż╬ܦ▐qż“£pż▒żŲIEDMżŪ╚»╔ĮżĘFINFETż╬├Ž░╠ż“╔įŲ░ż╬żŌż╬ż╦żĘż┐ż╬ż╚╚µż┘żŲĪóżżż½ż╦żŌęÆżżĪŻä▌╣±ż╚Ų³╦▄ż╚ż╬╝┬╬üż╬║╣żŽż│ż¾ż╩Ę┴żŪĖĮżņż┐ĪŻ

SRAMż╦ż¬żżżŲżŽ┼ņėøĪóIBMĪóAMDżŽ2008ŃQż╚żõżõĖ┼żżŠ╩¾ż└ż¼ĪóźšźŻź¾Ę┴ėXż╬╬®öü╣Įļ]┼┼─cĖ·▓╠ź╚źķź¾źĖź╣ź┐ż“├ōżżż┐└ż─c║ŪŠ«ż╬SRAMź╗źļż“│½╚»żĘĪóŲ░║Ņż“│╬Ū¦żĘż┐ż╚╚»╔ĮżĘżŲżżżļ(╗▓╣═½@╬┴7)ĪŻż│ż╬Šņ╣ńżŽĪóź╗źļż╦ż¬żżżŲźėź├ź╚źŪĪ╝ź┐Ų╔ż▀Į±żŁż╬ż┐żßż╬ź╣źżź├ź┴ż╚żĘżŲFINFETż¼╗╚ż’żņżļź▒Ī╝ź╣żŪżóżĻĪóFINFETżŽ┼÷─śDRAMżõźšźķź├źĘźÕźßźŌźĻĪ╝żŪżŌ╗╚ż©żļż╬ż└ż╚╗ūż’żņżļĪŻ

└Ķż╬╩¾╣żŪżŌ£½żķż½ż╦ż╩ż├ż┐ż¼ĪóFINFETż╬╝┬├ō▓Įż╦żŽ┴Ļ┼÷ż╬╗■┤ųż¼ĘąāįżĘżŲżżżļĪŻĄū╦▄ż¼║ŪĮķż╦╚»╔ĮżĘżŲż½żķ║Żż▐żŪ15ŃQż╬ĘŅŲ³ż¼ż┐ż├ż┐ĪŻż╩ż╝ż└żĒż”ż½Ī®╔«Ūvż¼╣═ż©żļż╦║ŪĮķżŽź”ź¦Ī╝źŽż¼SOIżŪżóżļż┐żßĪóź│ź╣ź╚╣Ōż╦ż╩żķżČżļż“įuż╩ż½ż├ż┐ĪŻżĮżņĖ╬ż╦FINFET╬╠ŠÅ╝┬├ō▓ĮżŽź’ź¾ź┴ź├źūæųż╦┼ļ║▄ż╣żļź╚źķź¾źĖź╣ź┐┐¶ż╦ż¬żżżŲĪóżŌż”▐k├╩ż╬╚¶╠÷ż¼ØŁ═ūż└ż├ż┐ż¼ĪóSOIż“╗╚ż’ż╩żżźąźļź»╣Įļ]żŪż╬źūźĒź╗ź╣│½╚»ż╦śŗż╦╗■┤ųż¼ØŁ═ūż└ż├ż┐ż╬żŪżŽż╩żżż½ż╚╣═ż©żŲżżżļĪŻ

╗▓╣═½@╬┴

1Īź300▓»ź╚źķź¾źĖź╣ź┐ż½żķż╩żļ1ź┴ź├źūLSIżŽ╦Nż╦╔żØŌĪ╩2013/08/15Ī╦

2.ĪĪ[VLSI] Intel╝ęż¼22nm└ż┬ÕFinFETČ\Įčż“╚»╔ĮĪóĮj└¬ż╬─░╣ųŪvż¼ĮĖż▐żļĪóTech-OnĪ╩2012/06/15Ī╦

3.ĪĪIntelż¼22nm└ż┬Õż╬DRAM║«║▄SoCČ\Įčż“╚õŽ¬ĪóŲ³Ęąź©źņź»ź╚źĒź╦ź»ź╣Īó2013ŃQ7ĘŅ8Ų³ęÄĪóp.39

4.ĪĪ[ź╗ź▀ź│ź¾2012]ĪĪTSMCż¼16~10nm└ż┬Õż╬FinFETźūźĒź╗ź╣żõ3╝ĪĖĄČ\Įčż╬─¾ČĪ╗■┤³ż“£½Ė└ĪóTech-OnĪ╩2012/12/06Ī╦

5.ĪĪ╬®öü╣Įļ]ź╚źķź¾źĖź╣ź┐ż╬3╝ĪĖĄżęż║ż▀ź©ź¾źĖź╦źóźĻź¾ź░Č\Įč

6. ĪĪFinFET and other New Transistor Technologies

7. ┼ņėø/IBM/AMDĪó└ż─c║ŪŠ«ż╬╬®öü╣Įļ]ź╚źķź¾źĖź╣ź┐SRAMź╗źļż“│½╚»