Īųź└źųźļźčź┐Ī╝ź╦ź¾ź░ż¼Č╩ŪvĪūż“Ž¬─ĶżĘż┐FinFETČ\Įčż╬SPIźšź®Ī╝źķźÓ

ź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ╝ń╠¢ż╬SPIźšź®Ī╝źķźÓĪų3╝ĪĖĄźūźĒź╗ź╣ż╬╩╔ż╚źĮźĻźÕĪ╝źĘźńź¾Īūż¼1ĘŅ30Ų³Īó┼ņ»BĖµ├Ńź╬┐ÕżŪ│½╠¢żĄżņż┐ĪŻż│ż│żŪżŽĪó16/14nm╗■┬Õż½żķ╦▄│╩┼¬ż╦Ų│Ų■żĄżņżļFinFETżõĪóNANDźšźķź├źĘźÕż╬żĶż”ż╩āeĘ┐źßźŌźĻż╚żżż├ż┐źūźĒź╗ź╣ż╬3╝ĪĖĄ▓Įż“║╬żĻæųż▓ż┐ĪŻ2014ŃQ12ĘŅż╬IEDMżŪżŌFinFETż¼ĮjżŁż╩ź╚źįź├ź»ź╣ż“žéżßż┐żĶż”ż└ĪŻ

┐▐1ĪĪFinFETż╬║Ū┐ĘŲ░Ė■ż“Įęż┘żļ┼ņ»BĮj│žĪĪ╩┐╦▄Įė╬rČĄĶb

║ŪĮķż╬╣ų▒ķżŪżŽĪó┼ņ»BĮj│žÖ┌ŠÅČ\ĮčĖ”ē|ĮĻż╬╩┐╦▄Įė╬rČĄĶbĪ╩┐▐1Ī╦ż¼FinFETż╬║Ū┐ĘŲ░Ė■ż╚IEDMż╦ż¬ż▒żļFinFETČ\Įčż╦ż─żżżŲĮęż┘ż┐ĪŻTSMCż╬16nmźąźļź»ĪóIntelż╬16nmźąźļź»ĪóIBMż╬14nmSOIż╬żĮżņżŠżņż“Šę▓żĘż┐ĪŻTSMCżŽź╚źķź¾źĖź╣ź┐éāĀC└^┐┐ż“Ė½ż╗żŲżżż╩żżæųż╦Īó└Łē”ż¼Ė■æųżĘż┐ż│ż╚ż“Įęż┘ż┐ż╚żżż”ĪŻIntelż╬FinFETżŽż│żņż▐żŪ╚∙║┘▓ĮżŪVthż╬źąźķż─żŁż¼ĮjżŁż»ż╩żļöĄĖ■ż└ż├ż┐ż¼ĪóFinFETż╦ż╣żļż╚Īó22nmżŪźąźķż─żŁż¼žōŠ»żĘĪó14nmżŽżĄżķż╦žōŠ»żĘĪŻ90nmźūźņĪ╝ź╩źąźļź»ż╦ŖZż┼żżżŲżżżļ(┐▐2)ĪŻżŌż┴żĒż¾Īóź▓Ī╝ź╚─Š▓╝żŽź╬ź¾ź╔Ī╝źūż╦żĶż├żŲ╔įĮŃرż╬▒Ųūxż╦żĶżļżążķż─żŁż“═▐ż©ż┐╣Įļ]żŪżóżļĪŻIBMżŽSOIż╬FinFETż“╗╚żżĪóżĘż½żŌVthż╬─┤┼D├ōż╦╗┼Ą£┤ž┐¶ż╬░█ż╩żļ2¹|╬Óż╬źßź┐źļż“╗╚ż├ż┐╬Ńż“┐āżĘż┐ĪŻSOIż╬FinFETżŽFinż¼źąźļź»żĶżĻżŌ─Ńżżż┐żßĪ󟔟¦Ī╝źŽź│ź╣ź╚żŽ╣Ōż»żŲżŌĪóź╚źķź¾źĖź╣ź┐Ę┴└«ź│ź╣ź╚żŽżÓżĘżĒ▓╝ż¼żļż╚Ė½żŲżżżļĪŻ

┐▐2ĪĪIntelż╬16nmźąźļź»FinFETČ\Į迎źąźķż─żŁż¼žōŠ»żĘżŲżżżļĪĪĮąųZĪ¦IEDM 2014ĪĪ╣ų▒ķ╚ųęÄ3.7

źšźĪź”ź¾ź╔źĻż╬UMCżŽżŌż┴żĒż¾Īó16nmFinFETż╬│½╚»ż“┐╩żßżŲżżżļż¼ĪóŲ▒╝ęż╬FinFETČ\Į迎IBMż╚Č”Ų▒│½╚»żĘżŲżŁż┐żŌż╬ĪŻŲ▒╝ęCorporate Developmentż╬VPżŪżóżļJ.J. WuĢ■żŽĪó╣Ō└Łē”ż╩16nm FinFETż└ż▒żŪżŽż╩ż»Īó─Ńź│ź╣ź╚FinFETżŌ│½╚»żĘżŲż¬żĻĪóżĮżņżķż“╗╚żż╩¼ż▒żļż╚Įęż┘ż┐(╔Į1)ĪŻ─Ńź│ź╣ź╚FinFETżŽź│ź╣ź╚ż╬╣Ōżżź└źųźļźčź┐Ī╝ź╦ź¾ź░ż“╗╚ż’ż╩żżöĄ╝░ż╬FinFETżŪżóżĻĪóźŪźČźżź¾ź╬Ī╝ź╔żŪżŽ28nmż╦┴Ļ┼÷ż╣żļż╚żĘżŲżżżļĪŻ

╔Į1ĪĪUMCż╬─¾░Ųż╣żļ─Ńź│ź╣ź╚FinFETż╚16nm FinFETż╬ź▀ź├ź»ź╣

UMCż╬źūźņź╝ź¾żŪżŌĮęż┘żŲżżż┐żĶż”ż╦Īóźóź╣ź┌ź»ź╚╚µż╬╣ŌżżFinFETČ\Įčż╬╩Ōé╬ż▐żĻż╬»éżßŠ}żŽż╔ż”żõżķĪóź└źųźļźčź┐Ī╝ź╦ź¾ź░ż╬żĶż”ż└ĪŻżĮżņż“╬ó¤²ż▒żļż½ż╬żĶż”ż╦Īó┼ņ»Bź©źņź»ź╚źĒź¾ż╬SPEź▐Ī╝ź▒źŲźŻź¾ź░ÄźźūźĒź╗ź╣│½╚»╦▄ŗż╬┴ß└Ņ┐“Ģ■żŽĪóFin FETČ\Įčż╦Ė┬żķż║Īó28nmĪó20nmĪó14nmż╚╚∙║┘▓ĮżĄżņżŲżŌĮĖ└čövŽ®ŲŌż╬ź╚źķź¾źĖź╣ź┐├▒öüż╬ź│ź╣ź╚żŽ▓╝ż¼żķż╩ż»ż╩ż├żŲżżżļż╚Įęż┘ż┐ĪŻżĮż╬═²ĮyżŽĪóź└źųźļźčź┐Ī╝ź╦ź¾ź░ż╦żĶż├żŲ╩Ōé╬ż▐żĻż¼▓╝ż¼żļż½żķżŪżóżļĪŻ28nmż¼ź└źųźļźčź┐Ī╝ź¾ż“╗╚ż’ż╩ż»żŲ║čżÓ║ŪĖÕż╬źĻźĮź░źķźšźŻź╬Ī╝ź╔ż╚ż╩żļĪŻ14nm╗■┬ÕżŪżŽFinż╬źčź┐Ī╝ź¾╩°żņż╬╠õ¼öżŌ¤²żŁż▐ż╚ż”ĪŻ

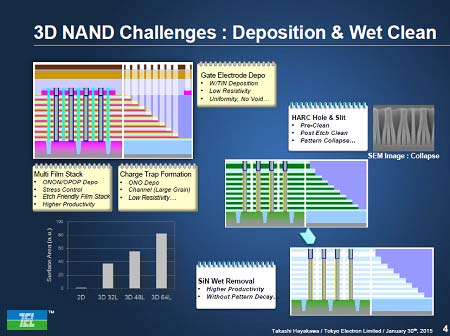

DRAMżõNANDźšźķź├źĘźÕż╬żĶż”ż╩źßźŌźĻżŌźóź╣ź┌ź»ź╚╚µż¼50Ī┴80ż╚Č╦żßżŲźĘźŃĪ╝źūż╩Ę┴ėXż╬źįźķĪ╝╣Įļ]ż¼ØŁ═ūż╦ż╩żļĪŻ3╝ĪĖĄNANDźšźķź├źĘźÕżŪżŽĪóźąźļź»ŲŌż╦Ę┴└«żĄżņż┐┐¶Ø▓ż╬┴žż╚ź│ź¾ź┐ź»ź╚ż“ż╚żļż┐żßż╦Ī󊻿Ę║’ż├żŲżŽŠņĮĻż“Š»żĘż║żķż╣Īóż╚żżż”║ŅČ╚ż“Ę½żĻ╩ųż╣ż│ż╚ż╦ż╩żļ(┐▐3)ĪŻ╣®µćż¼╗\ż©żļ╩¼ż└ż▒3D-NANDźšźķź├źĘźÕ╣Įļ]żŽ40%µć┼┘ź│ź╣ź╚źóź├źūż╦ż╩żļż╚żżż”ĪŻź│ź╣ź╚ż╦Ė½╣ńż”żĶż”ż╦ż╣żļż┐żßż╦3źėź├ź╚/ź╗źļ╣Įļ]ż¼╝ń╬«ż╦ż╩żļżĶż”ż└ĪŻ┴ĒżĖżŲĪóżżż½ż╦ŖWż»║Ņżļż½ż¼║ŪĮjż╬▓▌¼öż╚ż╩żļĪŻ

┐▐3ĪĪ3╝ĪĖĄNANDźšźķź├źĘźÕż╬ź│ź¾ź┐ź»ź╚Ę┴└«żŽ╣®µć┐¶ż¼¾HżżĪĪĮąųZĪ¦┼ņ»Bź©źņź»ź╚źĒź¾

źļź═źĄź╣ź©źņź»ź╚źĒź╦ź»ź╣żŽIEDM 2014żŪ16nmFinFETČ\Įčż╦żĶżļSRAM╗Ņ║Ņż“╚»╔ĮżĘż┐ĪŻSRAMżŽ├▒ż╩żļźßźŌźĻżõźŁźŃź├źĘźÕż└ż▒żŪżŽż╩ż»ĪóźūźĒź╗ź├źĄż╬źņźĖź╣ź┐żõźąź├źšźĪźßźŌźĻż╦żĶż»╗╚ż”ż┐żßĪóSRAMż“äh▓┴TEGż╚żĘżŲ╗Ņ║Ņż╣żļ┴T╠ŻżŽĮjżŁżżĪŻŲ▒╝꿎Īóź½Ī╝ź©źņź»ź╚źĒź╦ź»ź╣╩¼╠ŅżŪ2020ŃQż“ų`╗žżĘż┐Īų┼²╣ńź│ź├ź»źįź├ź╚Īūż╚żżż”ź│ź¾ź╗źūź╚ż“╚»╔ĮżĘżŲżżżļĪŻ║Żövż╬16nmFinFETźūźĒź╗ź╣ż╦żĶżļ256Kźėź├ź╚SRAMżŽźšźĪź”ź¾ź╔źĻż╬TSMCż¼×æļ]żĘż┐żŌż╬ż└ż¼Īóż│ż╬SRAMż“ĮĖ└čżĘż┐źĘź╣źŲźÓLSIżŽ2020ŃQż╦Š╚ØŹż“╣ńż’ż╗ż┐żŌż╬ĪŻ45nmż╬ŗī1└ż┬ÕĪó28nmż╬ŗī2└ż┬ÕĪóżĮżĘżŲ16nmFinFETźūźĒź╗ź╣ż╬ŗī3└ż┬Õż╬źĘź╣źŲźÓLSIż╚żĘżŲ└Łē”ż“æųż▓żŲżżż»ĪŻśOŲ░┘Zż╬┼²╣ńź│ź├ź»źįź├ź╚żŪżŽĪó▓ĶćĄŪ¦╝▒żõ▓ĶćĄĮĶ═²ż╩ż╔ż“źĻźóźļź┐źżźÓżŪ╣įż”ØŁ═ūż¼żóżļż┐żßĪó└Łē”Ė■æųżžż╬═ūĄßżŽäėżżĪŻż│ż╬ż┐żßźßźŌźĻ═Ų╬╠ż╬╗\Įjż╚ĪóĮĶ═²Å]┼┘ż╬Ė■æųż¼CPUż“Å]ż»ż╣żļĪŻ

║Żöv6ź╚źķź¾źĖź╣ź┐╣Į└«ż╬Fin FET SRAMź╗źļżŪżŽĪó╔ķ▓┘ź╚źķź¾źĖź╣ź┐ĪóŅ~Ų░ź╚źķź¾źĖź╣ź┐Īóźčź╣ź╚źķź¾źĖź╣ź┐Ų▒╗╬ż╬┼┼╬«╚µżŽ1×┤1ż╦ż╩ż├żŲżĘż▐ż”ĪŻ1×┤1ż└ż╚Į±╣■ż▀ż╦ż»ż»ż╩żļż┐żßĪóFinż╬┐¶ż“╗\żõż╣ż│ż╚żŪ┼┼╬«╚µż“ĮjżŁż»żĘż┐(┐▐4)ĪŻ▓├ż©żŲĪóĮ±żŁ╣■ż▀╗■ż╦żŽźąźżźóź╣ż“æųż▓żŲźčźļź╣╔²ż“╣Łż▓żļż┐żßż╬źóźĘź╣ź╚övŽ®ż“└▀ż▒ż┐ĪŻż│ż╬±T▓╠Īóź▐Ī╝źĖź¾ż¼╣Ōż»ż╩żĻĪó╣ŌÅ]▓ĮżŪżŁżļżĶż”ż╦ż╩ż├ż┐ż╚żĘżŲżżżļĪŻ

┐▐4ĪĪFinFETż└ż╚SRAMź╗źļż╬ź╚źķź¾źĖź╣ź┐ż╬┼┼╬«╚µż╦żĶżĻĮ±╣■ż▀ż¼║żžMż╦ż╩żļĪĪĮąųZĪ¦źļź═źĄź╣ź©źņź»ź╚źĒź╦ź»ź╣

FinFETČ\Į迎ź╚źķź¾źĖź╣ź┐Ų▒╗╬ż╬š{▀`ż¼ŖZżżźĒĪ╝ź½źļżŪżŽĪóźąźķż─żŁż¼žōżļż¼Īó1ź┴ź├źūæųżŪ▀`żņż┐ź╚źķź¾źĖź╣ź┐Ų▒╗╬żŽĮjżŁż»źąźķż─ż»ż╚żĘżŲżżżļĪŻ

FinFETż╬żĶż”ż╩3╝ĪĖĄźūźĒź╗ź╣żŽĪó×æļ]ż└ż▒żŪżŽż╩ż»└▀╝ŖæųżŌ▓▌¼öż¼¾HżżĪŻEDAź─Ī╝źļżŌ▓■╬╔ż“┌ģżķżņżŲżżżļĪŻØŖż╦ź└źųźļźčź┐Ī╝ź╦ź¾ź░żõFinFETż╬Ę┴ėXżõżĮżņż╦┤ż┼ż»°BŃ^ż╚═Ų╬╠ż╬├ĻĮąż¼žMżĘżżĪŻż│ż╬ż┐żßĪóź└źųźļźčź┐Ī╝ź╦ź¾ź░ż╚FinFETĖ■ż▒ż╬ź─Ī╝źļż¼’Lż½ż╗ż╩żżĪŻMentor GraphicsżŽĪóśO╝ęż╬ر═²ĖĪŠ┌ź─Ī╝źļCalibreż“▓■╬╔żĘżŲĪóFinFETż╦Ė■ż▒ż┐źčź┐Ī╝ź¾ż╬╔²żõ┤ų│ųż╬źļĪ╝źļź┴ź¦ź├ź»ż“▓─ē”ż╦ż╣żļźŌźŪźļż“│½╚»żĘżŲżżżļĪŻ

FinFETČ\Į迎Īó└▀╝Ŗż½żķ×æļ]źūźĒź╗ź╣Īó×æļ]äóÅøż╩ż╔╔²╣Łżż╩¼╠Ņż╦Ą┌żųźŲź»ź╬źĒźĖĪ╝żŪżóżļĪŻż│ż╬ź╗ź▀ź╩Ī╝żŽĪóż│ż╬ż│ż╚ż“║ŲŪ¦╝▒żĄż╗żļ╣Į└«ż“║╬ż├ż┐ĪŻ