ź╩ź╬źżź¾źūźĻź¾ź╚ż╬╬╠ŠÅ▓ĮżŽ22nm░╩æTż╬NANDźšźķź├źĘźÕĪóźŽĪ╝ź╔źŪźŻź╣ź»ż½żķ

Mark Melliar-SmithĢ■(hu©¼)Īóä▌(sh©¼)Molecular Imprints╝ęCEO

2001ŃQĪóä▌(sh©¼)╣±źŲźŁźĄź╣䔟¬Ī╝ź╣ź┴ź¾żŪ┴ŽČ╚żĘż┐Molecular Imprints╝ęż¼Īó22nm░╩æTż╬źĻźĮź░źķźšźŻČ\ĮčżŪżóżļź╩ź╬źżź¾źūźĻź¾ź╚äóÅøż“│½╚»Īóż▐ż└╗Ņ║Ņ├ōżŪżóżļż¼Įj(lu©░)Š}┐¶╝ęż╦Ū╝Ų■żĘż┐ĪŻ22nmż╚ż╩żļż╚“£═Ķż╬ūā─╣Č\Įčż╬ź└źųźļźčź┐Ī╝ź╦ź¾ź░ĪóżóżļżżżŽEUVĪ╩13.5nmż╬«Ćø](m©”i)āS─╣Ī╦źĻźĮź░źķźšźŻż¼Ńt▌öż╦æųż¼ż├żŲżżżļĪŻź└źųźļźčź┐Ī╝ź╦ź¾ź░żŽź╣źļĪ╝źūź├ź╚ż¼╚Š╩¼ĪóEUVżŽĖ„Ė╗Īóź▐ź╣ź»ż╩ż╔╠ż▓“»éż╬╠õ¼öż“žQż©żŲżżżļĪŻź╩ź╬źżź¾źūźĻź¾ź╚żŽ│õżĻ╣■żßżļż½ĪŻ═ĶŲ³żĘż┐Molecular Imprints╝ęCEOż╬Mark Melliar-SmithĢ■(hu©¼)ż╦▒MōQż“╩╣żżż┐ĪŻ

QĪ╩ź╗ź▀ź│ź¾ź▌Ī╝ź┐źļįćĮĖ─╣ĪĪģ╚┼─Ę·Ų¾Ī╦Ī¦║Żöv═ĶŲ³żĘż┐ų`┼¬ż╚Īóź╩ź╬źżź¾źūźĻź¾ź╚Č\Įčż╬ĖĮėX(ju©”)ż“ČĄż©żŲż»ż└żĄżżĪŻ

AĪ╩Molecular Imprints╝ęCEOż╬Mark Melliar-SmithĢ■(hu©¼)Ī╦Ī¦╗Ņ║Ņ├ōż╬äóÅøż“║ŪŖZżŪżŽSEMATECHż╦Ū╝Ų■żĘĪóżĮż╬Øiż╦┼ņėøż╦żŌŪ╝Ų■żĘż▐żĘż┐ĪŻ┼ņėøżŽ2008ŃQ2ĘŅż╦╣įż’żņż┐SPIE Advanced Lithography 2008żŪ22nmż╬źčź┐Ī╝ź¾ż“Ę┴└«żĘż┐ż│ż╚ż“╚»╔ĮżĘżŲżżż▐ż╣ĪŻ║Żövż╬═ĶŲ³żŽĪóŲ³╦▄ż╦äŅ(l©¼)║▀┼¬ż╩Ė▄Ąęż¼żżżļż½żķżŪż╣ĪŻĖÕż█ż╔Įęż┘ż▐ż╣ż¼Īó┼ņėø░╩│░żŪżŌäŅ(l©¼)║▀Ė▄ĄężŽźŽĪ╝ź╔źŪźŻź╣ź»äóÅøż“║Ņż├żŲżżżļŲ³╬®żõ╔┘╗╬─╠ż╩ż╔żŪż╣ĪŻ

żŪżŁżļż└ż▒SiźūźĒź╗ź╣ż╦▐pż├ż┐Č\Įčż“ŠW(w©Żng)├ō

QĪ¦ź╩ź╬źżź¾źūźĻź¾ź╚ż╬źóźżźŪźóżŽ┐¶ŃQØiż½żķżóżĻż▐ż╣ż¼Īóż╩ż½ż╩ż½Ė½─╠żĘż¼╬®ż┴ż▐ż╗ż¾ĪŻż│żņż▐żŪż╬źóźżźŪźóż╚╚µż┘ż┐ØŖ─╣żŽ▓┐żŪż╣ż½Ī®

AĪ¦ż│żņż▐żŪżŽż▀ż¾ż╩Ų╚śOż╬żõżĻöĄ(sh©┤)żŪĪóź╩ź╬źżź¾źūźĻź¾ź╚Č\Įčż“żõżĒż”ż╚żĘżŲżŁż▐żĘż┐ĪŻżĘż½żĘ┼÷╝꿎żŪżŁżļż└ż▒╚ŠŲ│öüźūźĒź╗ź╣ż╚Ė▀┤╣└Łż“╩▌ż─öĄ(sh©┤)╦ĪżŪż│ż╬Č\Įčż“│╬╬®żĘżĶż”ż╚żĘżŲżżż▐ż╣ĪŻż│ż│ż¼Įj(lu©░)żŁż╩░ŃżżżŪż╣ĪŻ

║ŅżĻöĄ(sh©┤)żŽØÖ(r©┤n)Š’ż╦į~├▒żŪż╣ĪŻż▐ż║Ų®£½ż╩ź¼źķź╣ź▐ź╣ź»ż╦▒·õüż╬źčź┐Ī╝ź¾ż“ķWżŁż▐ż╣ĪŻż│ż╬ź¼źķź╣żŽ╚ŠŲ│öüż╬źšź®ź╚ź▐ź╣ź»ż╚Ų▒żĖ║Ó╬┴żŪ╣Į└«żĄżņż▐ż╣ż¼Īó▒·õüż╬źčź┐Ī╝ź¾ż“ź©ź├ź┴ź¾ź░żŪ║Ņżļż│ż╚ż└ż▒ż¼░█ż╩żĻż▐ż╣ĪŻż│ż╬▒·õüźčź┐Ī╝ź¾ż“║Ņżļż╬żŽĪóĮj(lu©░)Ų³╦▄░§║■żõõü╚Ū░§║■ĪóHOYAż╩ż╔ź▐ź╣ź»źßĪ╝ź½Ī╝żŪż╣ĪŻż│żņżŽ─╠Š’ż╬┼┼╗ęźėĪ╝źÓŽ¬Ė„żŪ║ŅżĻż▐ż╣ĪŻ

ż│ż╬żóż╚GDSźšź®Ī╝ź▐ź├ź╚ż╦ØŹĄ“żĘż┐╚ŠŲ│öüövŽ®źčź┐Ī╝ź¾ż“źĘźĻź│ź¾ź”ź¦Ī╝źŽæųż╦Ę┴└«żĘż▐ż╣ĪŻźżź¾ź»źĖź¦ź├ź╚Č\Įčż“╗╚żżķ]ėX(ju©”)ż╬Ė„╣┼▓Į█`╗ķż“ż│ż╬övŽ®źčź┐Ī╝ź¾ż╦▐pż├żŲż┐żķżĘżŲżżżŁż▐ż╣ĪŻźżź¾ź»źĖź¦ź├ź╚żŽ1000żŌż╬ź╬ź║źļż½żķ▐k└Ųż╦ķ]ėX(ju©”)█`╗ķż“┼ŪĮążĘż▐ż╣ĪŻż│ż│żŪżŽŠ’ča(b©│)żŪ║ŅČ╚żŪżŁż▐ż╣ĪŻżĮż╬ĖÕĪóŲ®£½ż╩ź¼źķź╣ż╬æųĪ╩▒·õüźčź┐Ī╝ź¾ż╬ż╩żżĀCĪ╦ż½żķi└■ż╬╚Ø│░└■ż“Š╚╝o(j©¼)żĘĪó█`╗ķż“╣┼▓ĮżĄż╗ż▐ż╣ĪŻ█`╗ķż╬╣┼▓ĮżŽźšź®ź╚źņźĖź╣ź╚ż╚µ£ż»Ų▒żĖżŪż╣ĪŻ

ź¼źķź╣ż╬Įj(lu©░)żŁżĄżŽĪóź╣źŲź├źčż╬źšźŻĪ╝źļź╔źĄźżź║ż╚Ų▒żĖ26mmĪ▀33mmżŪż╣ż╬żŪĪ󟔟¦Ī╝źŽµ£ĀCż╦┼Žż├żŲż│ż╬║ŅČ╚ż“ź╣źŲź├źū&źĻźįĪ╝ź╚öĄ(sh©┤)╝░żŪĘ½żĻ╩ųżĘż▐ż╣ĪŻź╣źŲź├źčż╚Ų▒żĖżõżĻöĄ(sh©┤)żŪż╣ż¼ĪóĮj(lu©░)żŁż╩źņź¾ź║żŌ═ūżĻż▐ż╗ż¾żĘĪó┐┐ȧżŌ═ūżĻż▐ż╗ż¾ĪŻźņĪ╝źČĪ╝Ė„Ė╗żŌ▓Į│ž╗\╔²źņźĖź╣ź╚żŌ═ūżĻż▐ż╗ż¾ĪŻ

Įą═Ķæųż¼ż├ż┐źčź┐Ī╝ź¾żŽźšź®ź╚źņźĖź╣ź╚ż╚Ų▒══Īó2:1ż╬źóź╣ź┌ź»ź╚╚µż“Ęeż┴ż▐ż╣ĪŻż│ż╬żóż╚“£═Ķż╬╚ŠŲ│öüźūźĒź╗ź╣ż╚Ų▒══ż╦ź©ź├ź┴ź¾ź░żĘĪóĮĻ╦Šż╬źčź┐Ī╝ź¾ż“ķWżŁż▐ż╣ĪŻ

ż│ż╬Č\Įčż“╗╚ż├żŲ5nmCMOSź╚źķź¾źĖź╣ź┐ż╬Ų░║Ņż“│╬Ū¦żĘż▐żĘż┐ĪŻCMOSźūźĒź╗ź╣ż╚Ų▒żĖżĶż”ż╦ź╚źķź¾źĖź╣ź┐ż“║ŅżĻĪóŲ░║Ņż“│╬Ū¦żŪżŁż┐ż╚żżż”ż│ż╚żŽĪó╚ŠŲ│öüźūźĒź╗ź╣ż╬╚∙║┘▓ĮżŽŠ»ż╩ż»ż╚żŌ5nmż▐żŪżŽ▓─ē”ż└ż╚żżż”ż│ż╚żŪż╣ĪŻ

22nm░╩æTż╬NANDźšźķź├źĘźÕż╚źŽĪ╝ź╔źŪźŻź╣ź»▌xŠņż╦╗▓Ų■

QĪ¦┴└ż”▌xŠņżŽż╔ż│żŪż╣ż½Ī®

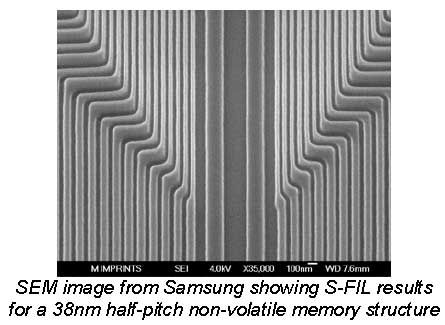

AĪ¦┼÷╝꿎Ė„źĻźĮź░źķźšźŻżõEUVźĻźĮź░źķźšźŻż╦ü÷ż’żļ▓─ē”└Łż“ĄßżßżŲź╩ź╬źżź¾źūźĻź¾ź╚Č\Įčż“│½╚»żĘżŲżżż▐ż╣ĪŻ┴└ż”▌xŠņżŽ╚ŠŲ│öüźßźŌźĻĪ╝ż╚źŽĪ╝ź╔źŪźŻź╣ź»żŪż╣ĪŻ╚ŠŲ│öüżŽ╚∙║┘▓Įż“┐õ┐╩ż╣żļNANDźšźķź├źĘźÕżõDRAMż╩ż╔ż╬źßźŌźĻĪ╝żŪż╣ĪŻźĄźÓź╣ź¾żŽĪóźŽĪ╝źšźįź├ź┴38nmż╬źšźķź├źĘźÕźßźŌźĻĪ╝╣Įļ]ż╦╗╚ż├żŲż▀ż┐╝┬┘x└^┐┐ż“╚»╔ĮżĘżŲż¬żĻĪó─Š│čż╦Č╩ż¼żļŪ█└■źčź┐Ī╝ź¾żŪżŌź│Ī╝ź╩Ī╝ŗżŪż╬╠õ¼öż¼µ£ż»żóżĻż▐ż╗ż¾ĪŻāS─╣ż“╗╚ż’ż╩żżż┐żßĪóOPCĪ╩Ė„ŖZ└▄▌ö┘ć(l©żi)Ī╦ż“╗╚ż’ż╩ż»żŲ║čż▀ż▐ż╣ĪŻ

ż▐ż┐ĪóźŽĪ╝ź╔źŪźŻź╣ź»żŽż│żņż▐żŪż╬źčź┐Ī╝ź¾ż╩żĘż½żķ╩Ż┐¶ż╬źėź├ź╚ż“źčź┐Ī╝ź╦ź¾ź░ż╣żļöĄ(sh©┤)Ė■żžż╚╩čż’żĻż▐ż╣ĪŻ║ŪŖZżŽ╣Ō╠®┼┘▓Įż╬ż┐żßÄņ(k©┤)─Š╝¦ĄżöĄ(sh©┤)╝░ż“║╬├ōżĘżŲż¬żĻĪ󿥿ķż╦╣Ō╠®┼┘▓Įż╣żļż┐żßż╦źėź├ź╚ż╬źčź┐Ī╝ź╦ź¾ź░ż╦ź╩ź╬źżź¾źūźĻź¾ź╚ż“╗╚żżż▐ż╣ĪŻŲ³╦▄żŪżŽŲ³╬®ź░źĒĪ╝źąźļź╣ź╚źņĪ╝źĖźĘź╣źŲźÓź║żõæčĘ┴╔┘╗╬─╠ż╩ż╔ż¼źŽĪ╝ź╔ź╔źķźżźųż“║Ņż├żŲż¬żĻĪóżĮżņż╦×┤▒■żĘż┐źŪźŻź╣ź»żŌ×æ║ŅżĘżŲżżż▐ż╣ĪŻźŽĪ╝ź╔źŪźŻź╣ź»żŽ1ŃQ┤ųż╦10▓»ĮŚÖ┌ŠÅżĘżŲżżżļĄĮj(lu©░)ż╩▌xŠņżŪż╣ĪŻż│żņż▐żŪ┼÷╝꿎HDD├ōż╬ź╩ź╬źżź¾źūźĻź¾ź╚äóÅøż“10±ś£pÅRżĘĪóżĮż╬ż”ż┴6±śż“Įą▓┘żĘż▐żĘż┐ĪŻ

QĪ¦CMOS LSIż╬│½╚»ż╦┤žżĘżŲĪóEUVżõĖ„źĻźĮź░źķźšźŻż╚╚µż┘żŲŃ~ŠW(w©Żng)ż╩ØŖ─╣żŽ▓┐żŪż╣ż½Ī®

AĪ¦ż│ż╬Č\ĮčĪóS-FILĪ╩Step and Flash Imprint LithographyĪ╦żŽ10nm░╩▓╝ż╬źŪźąźżź╣żŪżŌ║Ņ×æ▓─ē”żŪż╣ĪŻ╝┬║▌Īó5nmż╬CMOSź╚źķź¾źĖź╣ź┐ż“ż│ż╬Č\ĮčżŪ║ŅżĻĪóŲ░║Ņż“│╬Ū¦żĘż┐ż╚żżż”╚»╔Įż¼żóżĻż▐żĘż┐ĪŻż▐ż┐Īó┘J┘Tż╬CMOSźūźĒź╗ź╣żŪżĮż╬ż▐ż▐×æļ]żŪżŁĪó193nmźĻźĮź░źķźšźŻż╚ź▀ź├ź»ź╣Ī§ź▐ź├ź┴Č\ĮčżŪCMOSLSIż“?y©żn)æļ]żŪżŁż▐ż╣ĪŻĖ„╣┼▓Į█`╗ķż“╗╚żżż▐ż╣ż╬żŪŽ¬Ė„ż¼ØŁ═ūżŪż╣ż¼Īóź└źųźļźčź┐Ī╝ź╦ź¾ź░Č\Įčż╚żŽ░Ńżż1övŽ¬Ė„żŪż╣ż▀ż▐ż╣ż╬żŪĪóį~├▒żŪCoOĪ╩ź│ź╣ź╚ź¬źųź¬Ī╝ź╩Ī╝źĘź├źūĪ©▒┐┼Š╔nŲ»ź│ź╣ź╚Ī╦ż¼ŖWżżż╚żżż”ØŖ─╣ż¼żóżĻż▐ż╣ĪŻ

ż▐ż┐ĪóĖ„ż╬āS─╣ż“╗╚żżż▐ż╗ż¾ż╬żŪĪóźŪźČźżź¾źļĪ╝źļż╦żŽ┤žĘĖż╩ż»▓├╣®żŪżŁż▐ż╣ĪŻżĄżķż╦Īó┘J┘Tż╬Ė„źĻźĮź░źķźšźŻż╬źżź¾źšźķĪ╩ź▐ź╣ź»żõźņźĖź╣ź╚ĪóĖ„Ė╗Ī╦ż“żĮż╬ż▐ż▐ŠW(w©Żng)├ōżŪżŁż▐ż╣ĪŻ

45nmźūźĒź╗ź╣ż“1ż╚żĘżŲĪó22nmźūźĒź╗ź╣ż╬CoOż“ź╩ź╬źżź¾źūźĻź¾ź╚Č\Įčż╚EUVĪóź└źųźļźčź┐Ī╝ź╦ź¾ź░żŪ1źņźżźõĪ╝┼÷ż┐żĻż╬źĻźĮź│ź╣ź╚ż“╚µ│ėżĘż┐╬Ńż¼żóżĻż▐ż╣ĪŻ22nmż╦ż╩żļż╚ź└źųźļźčź┐Ī╝ź╦ź¾ź░żŽ3Ū▄ż╦ż╩żĻĪóEUVżŽ2.2Ū▄ż╦ż╩żĻż▐ż╣ĪŻEUVżŽ1±ś100▓»▀ģż╦ż╩żļż╚ż╬═Į▒RżŌżóżĻż▐ż╣ĪŻź╩ź╬źżź¾źūźĻź¾ź╚ż└ż╚źĘź¾ź░źļźŌźĖźÕĪ╝źļżŪżŌ1.4Ū▄µć┼┘Īóź╣źļĪ╝źūź├ź╚ż“æųż▓żļż┐żßźĻźĮź┴źŃź¾źąż“╩Ż┐¶±śĮĖżßż┐ź»źķź╣ź┐ź─Ī╝źļż╦ż╣żļż╚1.2Ū▄µć┼┘ż╦żĘż½æųż¼żĻż▐ż╗ż¾ĪŻ

QĪ¦ź╩ź╬źżź¾źūźĻź¾ź╚Č\ĮčżŪ╚∙║┘źčź┐Ī╝ź¾ż“║Ņż├ż┐╬ŃżŽżóżĻż▐ż╣ż½Ī®

AĪ¦╝┬║▌ż╦ż│ż╬äóÅøż“╗╚żżż▐żĘżŲĪó┼ņėøżŽ║ŪŠ«Øó╦Ī18nmż╬ź╩ź╬źżź¾źūźĻź¾ź╚źčź┐Ī╝ź¾ż“ķWżżż┐ż│ż╚ż“2008ŃQ2ĘŅż╦│½╠¢(h©żo)żĄżņż┐SPIE Advanced Lithography 2008żŪ╚»╔ĮżĘżŲżżż▐ż╣ĪŻźĄźÓź╣ź¾żŽĪó38nmż╬NANDźšźķź├źĘźÕźßźŌźĻĪ╝ż╦┼¼├ōżĘĪóŪ█└■ż“90┼┘└▐żĻČ╩ż▓ż┐źčź┐Ī╝ź¾ż¼żŁżņżżż╦Ę┴└«żĄżņżŲżżżļ└^┐┐ż“┐ā(j©®)żĘżŲżżż▐ż╣ĪŻIBMżŌź╣ź╚źņĪ╝źĖ├ōż╬╔įĦ╚»└ŁźßźŌźĻĪ╝├ōFINFETż“║Ņ×æżĘżŲżżż▐ż╣ĪŻż│ż│żŪżŽ20nmż╚30nmż╬FINFETż“ArFż¬żĶżėKrFźņĪ╝źČĪ╝źĻźĮź░źķźšźŻż╚ż╬ź▀ź├ź»ź╣Ī§ź▐ź├ź┴öĄ(sh©┤)╝░ż“ŠW(w©Żng)├ōżĘżŲżżż▐ż╣ĪŻ

źŽĪ╝ź╔źŪźŻź╣ź»ż╬źčź┐Ī╝ź╦ź¾ź░żŽź╣źŲź├źūĪ§źĻźįĪ╝ź╚żŪżŽż╩ż»Īó▐k│ńŽ¬Ė„żŪż╣ż¼ż│ż╬öĄ(sh©┤)╝░żŪżŌźŽĪ╝źšźįź├ź┴24nmż╬─Š└■źčź┐Ī╝ź¾ĪóźŽĪ╝źšźįź├ź┴28nmż╬ź╔ź├ź╚źčź┐Ī╝ź¾ż“ķWżżż┐╬Ńż¼żóżĻż▐ż╣ĪŻ

QĪ¦źčź┐Ī╝ź¾ż“║Ņżļż┐żßż╬Ų®£½ż╩ź¼źķź╣ź▐ź╣ź»żŽ▓┐övĪóĘ½żĻ╩ųżĘ╗╚ż©ż▐ż╣ż½Ī®

AĪ¦ź▐ź╣ź»żŽ═Ž═╗źĘźĻź½×æżŪż╣ĪŻż│żņżŽ┐ÕŠĮż╚ż¬ż╩żĖż»żķżżŠµ╔ūżŪż╣ż½żķĪó├C╠ūż╣żļż│ż╚żŽż█ż╚ż¾ż╔ż╩ż»Īó┐¶╝å╦³öv╗╚ż©ż▐ż╣ĪŻż┐ż└żĘĪó┐¶╗hövż╦▐k┼┘ź»źĻĪ╝ź╦ź¾ź░żŽØŁ═ūżŪż╣ĪŻ

QĪ¦║ŻĖÕż╬źĒĪ╝ź╔ź▐ź├źūż╦ż─żżżŲČĄż©żŲż»ż└żĄżżĪŻ

AĪ¦║ŪŖZĪóź¬Ī╝źļźąź╦Ī╝Ī╩ź╦źÕĪ╝źĶĪ╝ź»ä”Ī╦ż╬SEMATECHż╦Ū╝Ų■żĘż▐żĘż┐ĪŻ║ŻĪó32nm░╩▓╝ż╬źŪźąźżź╣│½╚»ż╦Ė■ż▒300mmź”ź¦Ī╝źŽ×┤▒■äóÅøżŪżóżļImprio 300ż╬£pÅRż“╗ŽżßżŲżżż▐ż╣ĪŻż│żņżŽż▐ż└╗Ņ║Ņ├ōż╬äóÅøżŪź╣źļĪ╝źūź├ź╚żŽ4ĮŚ/╗■ż╚ż▐ż└Š»ż╩żżżŪż╣ż¼Īó2009ŃQż╦żŽ20nmż▐żŪż╬źūźĒź╗ź╣│½╚»ż╦Ė■ż▒Imprio 3xxż“Ų│Ų■żĘż▐ż╣ĪŻ2010ŃQż╦żŽ║ŪĮķż╬╬╠ŠÅ×┤▒■ż╚żĘżŲ15nmźūźĒź╗ź╣×┤▒■ĄĪżŪź╣źļĪ╝źūź├ź╚ż“20ĮŚ/╗■ż╦æųż▓ż┐HVMż“Įąż╣═Į─ĻżŪż╣ĪŻ2011ŃQż╬ĖÕ╚Šż╦żŽ║ŪŠ«Øó╦Ī7nmĪóź╣źļĪ╝źūź├ź╚80ĮŚ/╗■ż╬4źžź├ź╔öĄ(sh©┤)╝░ż╬ź»źķź╣ź┐ź─Ī╝źļHVM ź»źķź╣ź┐ż“ĮążĘżŲżżż»═Į─ĻżŪż╣ĪŻ

żĄżķż╦Įø(j©®ng)═ĶżŽźŽĪ╝ź╔źŪźŻź╣ź»░╩│░ż╦żŌźšź®ź╚±TŠĮĖ■ż▒ż╦Ė„ż“╩─żĖ╣■żßżļLEDżõĪ󟔟Żźļź╣ż╚Ų▒żĖźĄźżź║ż╬DNAż“┬¬ż©żļż┐żßż╬źąźżź¬źŲź»ź╬źĒźĖ├ō²ŗż╩ż╔ż╦żŌ▒■├ōżŪżŁżļż╚Ė½żŲżżż▐ż╣ĪŻ