╚ŠŲ│öüźūźĒź╗ź├źĄźßĪ╝ź½Ī╝ż¼ĮĖ±TżĘż┐╗š┴÷(IoT/ź╗źŁźÕźĻźŲźŻįć)

╗š┴÷ż╦┬Õ╔Į┼¬ż╩źūźĒź╗ź├źĄźßĪ╝ź½Ī╝ż╬źżź┘ź¾ź╚ż¼¶öĪ╣│½ż½żņż┐ĪŻĖÕ╚ŠżŪżŽĪóIoTż╬╠ż═Ķż“QualcommĪóArmĪóżĮżĘżŲ╠Ą╬┴ż╬CPUź│źóĪóRISC-Vż╬Ų░żŁż“Šę▓ż╣żļĪŻQualcommżŽIoTż╬╠ż═Ķż“├▒ż╩żļź│ź═ź»źŲźŻźėźŲźŻż½żķĖŁżĄż╚ź╗źŁźÕźĻźŲźŻżŌ▓├ż’żļż╚żĘĪóArmżŽź╗źŁźÕźóźšźņĪ╝źÓź’Ī╝ź»ż“Šę▓żĘż┐ĪŻ╠Ą╬┴ż╬CPUź│źóRISC-Vż╬ź─Ī╝źļżŌ┬Ężżż─ż─żóżļĪŻ

┐▐1ĪĪQualcomm╝ęIoTŗ╠ń×æēäź▐ź═źĖźßź¾ź╚├┤┼÷SVPż╬Raj TalluriĢ■

QualcommżŽĪóIoTŗ╠ń×æēäź▐ź═źĖźßź¾ź╚├┤┼÷ż╬VPżŪżóżļRaj TalluriĢ■Ī╩┐▐1Ī╦ż¼5G╗■┬Õż╬IoTż╦ż─żżżŲĖņżĻĪó║ŻĖÕż╬IoTż╦żŽĖŁżĄż¼▓├ż’żļż│ż╚żŪź»źķź”ź╔ż╦═Ļżļż└ż▒żŪżŽż╩ż»Īóź©ź├źĖżŌĖŁż»ż╣żļż│ż╚ż╦żĶżĻĪ󟻟ķź”ź╔ż“ź╣ź╚źņĪ╝źĖż╚żĘżŲŠW├ōżĘĪóź©ź├źĖżŪ▒ķōQż“ż╣żļżĶż”ż╦ż╩żļż╚ż▀żŲżżżļĪŻżĮżņżŽ╝Ī└ż┬Õż╬źŌźąźżźļ─╠┐«Č\Įč5Gż╚żŌ┤žĘĖż╣żļĪŻ5GżŪżŽ┐«ęÄż╬ęÆūā(źņźżźŲź¾źĘ)ż“1ms░╩ŲŌż╦═▐ż©żļźĻźóźļź┐źżźÓ└Łē”żŌ═ūĄß╗┼══ż╬▐kż─żŪżóżļĪŻ5G╗■┬Õż╬IoTźĘź╣źŲźÓż╦żŽźņźżźŲź¾źĘż“═▐ż©żļż┐żßż╦ź©ź├źĖżŪ▒ķōQżĘĖŁż»ż╣żļż╚żżż”ż╬żŪżóżļĪŻżĄżķż╦ź╗źŁźÕźĻźŲźŻż╬│╬╩▌żŌżóżļĪŻ

ź©ź├źĖż╬IoT├╝¼Źż¼ĖŁż»ż╩żļż│ż╚ż“ź¬ź¾źŪźąźżź╣źżź¾źŲźĻźĖź¦ź¾ź╣ż╚Ō}żėĪóź╣ź▐Ī╝ź╚ź█Ī╝źÓż“żŽżĖżßż╚ż╣żļ░cÖ┌IoTż½żķ╣®Č╚├ōIoTĪóź═ź├ź╚ź’Ī╝źŁź¾ź░Īóź│ź¾źįźÕĪ╝źŲźŻź¾ź░Ī󟻟ļź▐żžż╚żĄż▐żČż▐ż╩Č╚─cżžż╚╣Łż¼żļż╚żĘżŲĪ󟻟ļź▐żõź╣ź▐Ī╝ź╚ź█Ī╝źÓżŪż╬ŠW├ōźĘĪ╝ź¾ż“Šę▓żĘż┐ĪŻ╬Ńż©żąź»źļź▐żŪżŽĪóź╔źķźżźąĪ╝Ė─┐═ż┤ż╚ż╬└▀─Ļż“╣įżżĪóź╔źķźżźąĪ╝ż¼×®żķż╩żżżĶż”ż╦Š’ż╦źŌź╦ź┐Ī╝żĘżŲż¬ż»ĪóśOć·▒┐┼Šż╬ē”╬üż“╣ŌżßżļĪóż╩ż╔ż╬ĄĪē”ż“Ęeż┐ż╗żļż│ż╚ż¼żŪżŁżļĪŻ

ź╣ź▐Ī╝ź╚ź█Ī╝źÓżŪżŽż╣żŪż╦AIź╣źįĪ╝ź½Ī╝Ī╩ä▌╣±żŪżŽźŪźĖź┐źļźóźĘź╣ź┐ź¾ź╚ż╚Ō}żążņżŲżżżļĪ╦ż¼┼ąŠņżĘżŲżŁżŲżżżļż¼Ī󿥿ķż╦▓╗╠mŪ¦╝▒Īó┤ķŪ¦╝▒ĪóśO─śĖ└ĖņĮĶ═²Īó▓╗ż“ĖĪĮążĘżŲ╣įŲ░źčź┐Ī╝ź¾ż“└ĶŲ╔ż▀ż╣żļź│ź¾źŲź»ź╣ź╚źóź”ź¦źóź═ź╣ż╩ż╔┐ʿʿżĄĪē”ż“ź©ź├źĖŖõżŪ▓├ż©żļż│ż╚żŪĪóźĻźóźļź┐źżźÓ▒■┼·ż¼▓─ē”ż╦ż╩żļĪŻAIź╣źįĪ╝ź½Ī╝ż└ż▒żŪżŽż╩ż»Ī󟔟¦źóźķźųźļźŪźąźżź╣żõź╣ź▐Ī╝ź╚źšź®ź¾ż╩ż╔┬Šż╬IoTż╚ż╬ŽóĘ╚ż¼▓─ē”ż╦ż╩żļż╚═Į„[ż╣żļĪŻ

┐▐2ĪĪIoTż╬ź╗źŁźÕźĻźŲźŻżŌź╣ź▐ź█żŪ╗╚ż├żŲżŁż┐Č\Įčż“örżĻ╣■żÓĪĪĮąųZĪ¦Qualcomm

ź╗źŁźÕźĻźŲźŻż╦┤žżĘżŲżŌĪóÅŚŲ░╗■ż╬ź╗źŁźÕźóźųĪ╝ź╚ż“żŽżĖżßż╚żĘżŲĪóź╗źŁźÕźĻźŲźŻż“ż½ż╩żĻ│╬╩▌żĘż┐┤─ČŁż“║Ņżļż╚ż╣żļ(┐▐2)ĪŻźŪĪ╝ź┐ż“░┼ęÄ▓ĮżĘĪó▓“Ų╔ż╣żļż┐żßż╬ź½ź«ż╦żŌ░┼ęÄż“ż½ż▒Īóź╣ź▐ź█żŪ╣įż├żŲżŁż┐ź╗źŁźÕźóż╩Š}├╩żŽż╣ż┘żŲörżĻ╣■żÓż╚żĘżŲżżżļĪŻ

ż│ż”żżż├ż┐Įø═Ķż╬IoTż╦┤žżĘżŲżŌSnapdragonżŪźŪźąźżź╣ż“┬Ęż©żŲżżż»ĪŻź¬ź¾źŪźąźżź╣źżź¾źŲźĻźĖź¦ź¾ź╣ż“╝┬ĖĮż╣żļż┐żßż╦ØŁ═ūż╩źžźŲźĒźĖź╦źóź╣ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Ī╩CPUżõGPUĪóDSPĪóISĪóźŪźĖź┐źļźŌźŪźÓż╩ż╔ĘQ¹|ĘQ══ż╬źūźĒź╗ź├źĄż“ĮĖ└čżĘż┐SoCĪ╦Č\Įčż╬└Łē”żõĖ·╬©ż“æųż▓żŲżżż»ĪŻ

ArmżŽź╗źŁźÕźĻźŲźŻż╦╗ž┐╦

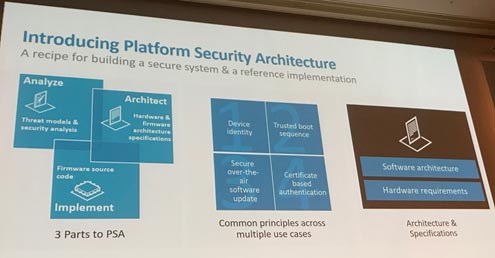

Qualcommż╬SoCż╦╗╚ż’żņżļCPUź│źóżŽArm Cortex AźĘźĻĪ╝ź║ż¼¾HżżĪŻArmżŽ└@├ōż╬ź│źóż╬ź╗źŁźÕźĻźŲźŻż“│╬╩▌ż╣żļż┐żßż╦Īó┐ʿʿżź╗źŁźÕźĻźŲźŻż╬╗┼┴╚ż▀ż╚ż╩żļĪųPSAĪ╩Platform Security ArchitectureĪ╦Īūż“╚»╔ĮżĘż┐ĪŻIoTż╬żĶż”ż╦µ£żŲż╬żŌż╬ż¼ź»źķź”ź╔ż╦ż─ż╩ż¼żļżĶż”ż╦ż╩żļż╚Ī󟥟żźąĪ╝ŲłĘŌż╦×┤ż╣żļź╗źŁźÕźĻźŲźŻż“│╬╩▌ż╣żļż│ż╚ż¼ź▐ź╣ź╚ż╦ż╩żļĪŻPSAżŽArmż¼─¾Š¦żĘż┐IoTĖ■ż▒ż╬ź╗źŁźÕźóż╩źūźķź├ź╚źšź®Ī╝źÓ╗┼══żŪĪ󟻟ķź”ź╔Č╚─cżõ┼┼╗ęĄĪ▀_Īó╚ŠŲ│öüż╩ż╔ż╬Č╚─cżŪܦĘeżĄżņżŲżżżļż╚żżż”ĪŻ

ArmżŽż│żņż▐żŪĪóź╗źŁźÕźóż╩ŗ▓░(ź│ź¾źŲź╩)ż╚ź╗źŁźÕźóżŪżŽż╩żżŗ▓░ż“╩¼ż▒żļTrustZoneż“10ŃQ░╩æųØiż╦╚»╔ĮżĘż┐żóż╚ĪóCryptoIslandżõĪóCryptoCellż╩ż╔ż╬ź╗źŁźÕźĻźŲźŻIPż“2015ŃQ░╩æTż╦╚»╔ĮżĘżŲżżż┐ĪŻCryptoIslandżŽĪó▒ķōQź©ź¾źĖź¾żõ░┼ęÄĄĪē”Īó░┼ęÄĖ░ż╩ż╔ż╬┤╔═²ż╚ĪóICź½Ī╝ź╔źņź┘źļż╬ź╗źŁźÕźĻźŲźŻż“1ź┴ź├źūæųż╦╝┬ĖĮż╣żļų`┼¬ż╬IPżŪĪóCryptoCellżŽźŽĪ╝ź╔ź”ź©źóźóź»ź╗źķźņĪ╝ź┐żõźŽĪ╝ź╔ż╬Roots-of-TrustöUĖµĪ╩░┼ęÄ▓ĮĮĶ═²ż╬▐kż─Ī╦ż╚Īóšl╔┘ż╩ź╗źŁźÕźĻźŲźŻźĮźšź╚ź”ź©źóżõź─Ī╝źļż“┴╚ż▀╣ńż’ż╗ż┐żŌż╬ĪŻ║ŻĖÕĪóIoTż¼1├¹Ė─ż─ż╩ż¼żļżĶż”ż╩└ż─cż“Ė½┐°ż©żļż╚Ī󟬟ūźĘźńź¾┼¬ż╦ź╗źŁźÕźĻźŲźŻIPż“źĻźĻĪ╝ź╣żĘżŲżżż»ż│ż╚żŪżŽżŌżŽżõ×┤▒■żŪżŁż╩ż»ż╩żļż╚ArmżŽ╣═ż©ż┐ĪŻ

żĮż│żŪ1├¹Ė─ż╬IoTż“ż─ż╩ż▓żŲżŌ×┤▒■żŪżŁżļżĶż”ż╩┐ʿʿż╗┼┴╚ż▀ż╚żĘżŲĪóPSAż“╚»╔ĮżĘż┐Ī╩┐▐3Ī╦ĪŻż│ż│żŪżŽĪóźąźĻźÕĪ╝ź┴ź¦Ī╝ź¾µ£öüż╦┼Žżļź╗źŁźÕźĻźŲźŻżõĪó║ŪŠ«ż╬ĮjżŁżĄżŪ─Ńź│ź╣ź╚ż╬źŪźąźżź╣ż╦żŌ╣Łż▓żķżņżļż│ż╚ĪóźŪźąźżź╣ż╬ź╗źŁźÕźóż╩└▄¶öż╚┤╔═²Īóż╦┤žżĘżŲ┤╦▄┼¬ż╦Ė½─ŠżĘż┐ĪŻżĮż╬±T▓╠ĪóŠ«Ę┐ż╦ż╩ż├żŲżŌIoT└▄¶öż╬ź╗źŁźÕźĻźŲźŻż“│╬╩▌żŪżŁżļČ”─╠źšźņĪ╝źÓź’Ī╝ź»ĪóČ╚─cźĻĪ╝ź└Ī╝ż½żķż╬╣Łżżź©ź│źĘź╣źŲźÓż╬źĄź▌Ī╝ź╚ĪóTrusted Firmware-Mż╚Ō}żųź¬Ī╝źūź¾źĮĪ╝ź╣ż╬źĻźšźĪźņź¾ź╣źšźĪĪ╝źÓź”ź¦źóĪóż╬įÆż─ż“┤╦▄ĄĪē”ż╚ż╣żļĪŻż▐ż┐Īóź╗źŁźÕźóż╩źĘź╣źŲźÓż“╣Į├█ż╣żļż”ż©żŪż╬┐ʿʿżźĘźĻź│ź¾IPż╚żĘżŲĪó╩¼▀`żĄżņżļArm CryptoIsland-300ż╚ź╗źŁźÕźóż╩źŪźąź├ź░ź┴źŃź¾ź═źļż“─╠ż╣Arm SDC-600żŌ╚»╔ĮżĘżŲżżżļĪŻ

┐▐3ĪĪPSAż╬┤╦▄3źčĪ╝ź─

PSAż╬┤╦▄źčĪ╝ź─żŽ3ż─żóżĻĪóżĮżņżŠżņ╩¼└ŽĪó╣Į├█Īó╝┬äóż½żķż╩żļĪŻ╩¼└ŽżŪżŽČ╝░ęż╚ż╩żļźŌźŪźļż“╣Į├█żĘź╗źŁźÕźĻźŲźŻż╦╩¼└Žż“╣įż”ĪŻ╣Į├█(źóĪ╝źŁźŲź»ź╚)żŪżŽĪóźŽĪ╝ź╔ź”ź©źóż╚źšźĪĪ╝źÓź”ź©źóż╬źóĪ╝źŁźŲź»ź┴źŃż╬╗┼══ż“─ĻżßżļĪŻ╝┬äó(źżź¾źūźĻźßź¾ź╚)żŪżŽĪóźšźĪĪ╝źÓź”ź©źóż╬źĮĪ╝ź╣ź│Ī╝ź╔ż¼─¾ČĪżĄżņżļĪŻżĄż▐żČż▐ż╩ŠW├ōźĘĪ╝ź¾ż╦×┤żĘżŲČ”─╠ż╬ĖČ═²żŽĪóźŪźąźżź╣ż╬ID(Ų▒─Ļ)żõĪó┐«═Ļż╬ż¬ż▒żļźųĪ╝ź╚źĘĪ╝ź▒ź¾ź╣Īóź╗źŁźÕźóż╩╠Ą└■─╠┐«ż╦żĶżļźĮźšź╚ź”ź©źóż╬śŗ┐ĘĪó3Ūv┤ųż╦żĶżļŪ¦Š┌ż└ż╚żĘżŲżżżļĪŻ

Trusted Firmware-Mż╬ØŖ─╣żŽĪóPSA╗┼══ż╦ØŹżĖżļArmŪ¦Š┌ż╬źšźĪĪ╝źÓź”ź©źóżŪżóżļż│ż╚Īó┴ßżż║╬├ōż¼żŪżŁżļżĶż”ż╩ź¬Ī╝źūź¾źĮĪ╝ź╣ż╩źķźżź╗ź¾ź╣Īó╠Ą╬┴żŪŲ■Š}▓─ē”ż╩źĻźšźĪźņź¾ź╣ż╬╝┬äóż╩ż╔żŪżóżĻĪó┼÷Įķż╬ų`║Yż“Armv8-Mź┘Ī╝ź╣ż╬SoCż╦żĘżŲżżżļĪŻ┴╚ż▀╣■ż▀ÅUż╬Arm Mbed OSżŽĪóż╣ż┘żŲż╬Cortex-MźŪźąźżź╣ż╦×┤żĘżŲPSA╝┬äóż“─¾ČĪż╣żļĪŻ

RISC-VżŽISAż“║YØŹ▓Įż╣żļż│ż╚ż¼┴└żż

źķźżź╗ź¾ź╣╬┴╠Ą╬┴ż╬CPUź│źóżŪżóżļRISC-V(źĻź╣ź»źšźĪźżźųż╚╚»▓╗)ż╬ĖĮėXż“┼┴ż©żļŲ³╦▄żŪĮķżßżŲż╬▓±Ą─ĪųRISC-V Day 2017 TokyoĪūż¼12ĘŅ18Ų³ż╦│½╠¢żĄżņż┐ĪŻż│żņż▐żŪĪóCPUź│źóż╬źķźżź╗ź¾ź╣╬┴ČŌżŽ╣Ōżżż╚żżż”╠mż“ź▐źżź│ź¾żõSoCż╬Š«æä╠Žż╩│½╚»┤ļČ╚ż½żķ╩╣ż½żņż┐ĪŻż│ż╬ż┐żßĪóArmż╚ż╬×┤Ń^║÷ĪóżóżļżżżŽ╠Ą╬┴ż╬OSżŪżóżļLinuxż╬CPUź│źó╚Ūż╚żżż”░╠Åøż┼ż▒żŪRISC-Vż“Ė½żļĖ■żŁż¼¾Hż½ż├ż┐ĪŻ

┐▐4ĪĪUCźąĪ╝ź»źņźżż╬Krste AsanovicČĄĶb

ż╚ż│żĒż¼ĪóRISC-VźóĪ╝źŁźŲź»ź┴źŃż“╣═░ŲżĘż┐ä▌UCBĪ╩ź½źĻźšź®źļź╦źóĮj│žźąĪ╝ź»źņźżē“Ī╦ż╬Krste AsanovicČĄĶb(┐▐4)żŽĪó╣═░ŲżĘż┐┴T▒Iż“Īó║ŪŖZż╬SoCż¼CPUżõGPUĪóDSPĪóISPż╩ż╔żĄż▐żČż▐ż╩źūźĒź╗ź├źĄź│źóż“ĮĖ└čż╣żļżĶż”ż╦ż╩żĻĪó░█ż╩żļISAĪ╩╠┐╬ßź╗ź├ź╚źóĪ╝źŁźŲź»ź┴źŃĪ╦ż“╗╚ż”żĶż”ż╦ż╩ż├ż┐ż┐żßż└ż╚└Ō£½żĘżŲżżżļĪŻż│żņż▐żŪArmźóĪ╝źŁźŲź»ź┴źŃżŌIntelż╬X86źóĪ╝źŁźŲź»ź┴źŃżŌżĮżņżŠżņ░█ż╩żĻĪóČ”─╠ż╬ISAżŽ┘T║▀żĘż╩ż½ż├ż┐ĪŻ

RISC-VżŪżŽĪó╩Ż╗©ż╩SoCż╦żŽ├▒ĮŃżŪČ”─╠ż╦╗╚ż©żļISAżŪ┼²▐kżĘżĶż”Īóż╚żżż”╚»„[ż¼┤╦▄ż╦żóżļĪŻż▐ż║CPUż╬ISAż“į~├▒ż╦żĘżŲGPUżõDSPż╦żŌ╗╚ż©żļżĶż”ż╦Č”─╠▓ĮżĘżĶż”ż╚żĘżŲżżżļĪŻż│żņż▐żŪż╬ISAżĶżĻżŌż║ż├ż╚Š«żĄż»Īóź▐źżź»źĒźóĪ╝źŁźŲź»ź┴źŃżõźŲź»ź╬źĒźĖĪ╝ż╦░═┘Tż╣żļØŖ─╣ż“└▀ż▒ż╩żżĪŻżĘż½żŌ│╚─źżŪżŁżļżżż»ż─ż½ż╬║YØŹ╗┼══ż“├ō┴Tż╣żļĪŻ┤╦▄ISAżõ│╚─ź║YØŹżŽ╔w─ĻżĄżņĪó╝{▓├żõź¬źūźĘźńź¾żŽ├ō┴TżĘż╩żżĪŻ

AsanovicČĄĶbż¼ĘŪż▓żļRISC-Vż╬ØŖ─╣żŽ4ż─żóżļĪ©

1)UCźąĪ╝ź»źņźżż¼│½╚»żĘż┐Īó╣Ōēää®Ī”źķźżź╗ź¾ź╣źšźĻĪ╝Ī”źĒźżźõźĻźŲźŻźšźĻĪ╝ż╬RISC ISA╗┼══

2)ØÖ▒─ŠW├─öüż╬RISC-V┤ČŌż╦żĶż├żŲ║YØŹ▓Įż¼░▌ĘeżĄżņżļ

3)ź▐źżź│ź¾ż½żķź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐ż▐żŪµ£żŲż╬ź│ź¾źįźÕĪ╝ź┐ż╦Ė■ż»

4)┐¶Ī╣ż╬Ų╚śOżŪź¬Ī╝źūź¾źĮĪ╝ź╣ż╬ź│źóż¼żóżļ

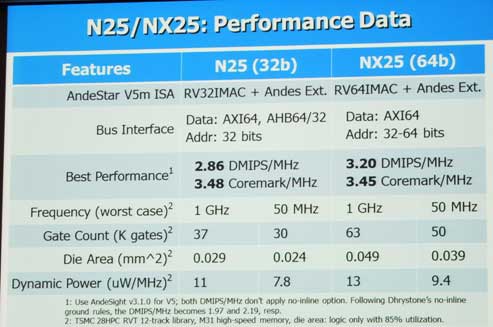

┐▐5ĪĪAndesż╬64źėź├ź╚CPUź│źóż╬└Łē”

RISC-Vź│źóż“╗╚ż├ż┐SoCżŽż╣żŪż╦3╝ęż¼╗Ņ║ŅżĘżŲżżżļĪŻ├µżŪżŌSiFiveĪ╩źĄźżźšźĪźżźųż╚╚»▓╗Ī╦żŽ2016ŃQ11ĘŅż╦ĪųFE310ĪūSoCż“─¾ČĪż╣żļż╚Č”ż╦Īó╠┐╬ßź╗ź├ź╚źĘź▀źÕźņĪ╝ź┐Ī”ź©ź▀źÕźņĪ╝ź┐żõEclipseź┘Ī╝ź╣ż╬│½╚»┤─ČŁĪóźĻźšźĪźņź¾ź╣źŪźČźżź¾ź▄Ī╝ź╔ż╩ż╔ż“─¾ČĪż╣żļĪŻ2005ŃQż╦┴Ž╬®żĄżņż┐±śŽčż╬Andes Technologyż╬NX25ź┴ź├źūżŽ64źėź├ź╚źóĪ╝źŁźŲź»ź┴źŃż╩ż¼żķĪóTSMCż╬28nmźūźĒź╗ź╣żŪ1GHz╝■āS┐¶żŪŲ░║Ņż╣żļ63kź▓Ī╝ź╚ż╬SoCżŪĪóżĮż╬ź┴ź├źūĀC└迎0.049mm2żĘż½ż╩żż(┐▐5)ĪŻź└źżź╩ź▀ź├ź»┼┼╬üżŽ13”╠W/MHzż╚Š«żĄżżĪŻ1GHzżŪ13mWż╦┴Ļ┼÷ż╣żļĪŻ

ż▐ż┐ĪóAsanovicČĄĶbż¼CTOż“ē»żßżļEsperanto Technologies╝꿎Īó7nmźūźĒź╗ź╣ż“╗╚ż├ż┐╣Ō└Łē”64źėź├ź╚RISCź┴ź├źūż“│½╚»├µż└ż╚żĘżŲżżżļĪŻEsperantożŽĪóż½ż─żŲTransmeta╝ęż“└▀╬®żĘŲ³╦▄żŪżŌż╩żĖż▀┐╝żżDave DitzelĢ■ż¼CEOż“ē»żßżŲżżżļĪŻ