B2B╗žĖ■ż¼£½│╬ż╦ż╩ż├ż┐CEATEC 2018 (2)Ī┴2╝ęż½żķAIż╬IPź│źó

CEATECżŪżŽAIź┴ź├źūż¼2¹|╬Ó┼ąŠņżĘż┐ĪŻżĮżņżŌź©ź├źĖżŪ╗╚ż’żņżļ┐õéb└ņ├ōż╬AIĖ■ż▒ż╬IPź│źóżŪżóżļĪŻä▌Lattice Semiconductorż╚▒čImagination Technologiesż¼żĮżņżŠżņź©ź├źĖ├ō²ŗż╦ØŖ▓ĮżĘż┐AI▒ķōQ├ōż╬IPź│źóż“╚»╔ĮżĘż┐ĪŻ

Lattice SemiconductorżŽĪó5ĘŅż╦╚»╔ĮżĘż┐IPź│źóSensAIźšźĪź▀źĻż“│╚─źżĘĪó2¹|╬Óż╬IPź│źóż“┬Ęż©ż┐ĪŻImagination TechnologiesżŌĪó└Łē”ż╚Š├õJ┼┼╬üż╬źąźķź¾ź╣ż╬ż╚żņż┐IPż╚Īó└Łē”═ź└Ķż╬IPż╬2¹|╬Óż“│½╚»żĘżŲżżżļĪŻLatticeż¼Š«Ę┐ż╬FPGAż╬ŲŌŗż╦ĮĖ└čż╣żļ└ņ├ōIPż╦×┤żĘżŲĪóImaginationż╬IPżŽźķźżź╗ź¾ź╣▓─ē”żŪĪó▐k╚╠▌xŠņż╦Ė■ż▒ż┐źķźżź╗ź¾ź╣▓─ē”ż╩IPżŪżóżļĪŻ

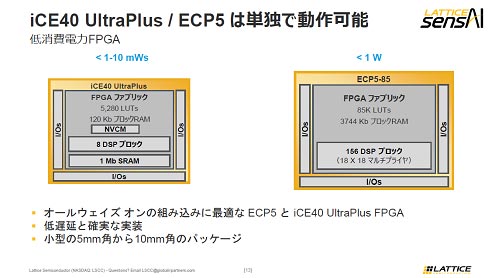

┐▐1ĪĪLatticeż¼╚»Ūõż╣żļCNNĖ■ż▒IPź│źóż“ŲŌē┼żĘż┐FPGAĪ©iCE40 UltraPlusż╚ECP-5

ĮąųZĪ¦Lattice Semiconductor

Š«Ę┐FPGAźßĪ╝ź½Ī╝ż╬Latticeż╬IPź│źóżŽ2¹|╬ÓżóżļĪ╩┐▐1Ī╦ĪŻ16źėź├ź╚ż╬CNNĪ╩øQż▀╣■ż▀ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»Ī╦ż╚1źėź├ź╚ż╬╬╠╗ę▓Įż╦×┤▒■żĘż┐Īó└Łē”ż╚Š├õJ┼┼╬üż╬źąźķź¾ź╣ż“┴└ż├ż┐CNNŠ«Ę┐źóź»ź╗źķźņĪ╝ź┐IPż╚Īó5ĘŅż╦╚»╔ĮżĘż┐EPC5 FPGAĖ■ż▒IPż╦DRAMż╬┬ė░Ķ╔²ż“16źėź├ź╚ż½żķ32źėź├ź╚ż╦╣Łż▓ż┐CNNźóź»ź╗źķźņĪ╝ź┐IPĪóżŪżóżļĪŻ└Łē”ż╦┤žżĘżŲżŽ£½żķż½ż╦żĘżŲżżż╩żżż¼ĪóDSPźųźĒź├ź»ż“8Ė─┤▐żÓØiŪvż╬IPż╬Š├õJ┼┼╬üżŽ1~10mWĪó156Ė─ż╬DSPźųźĒź├ź»ż“┤▐żÓĖÕŪvż╬żĮżņżŽ1W░╩▓╝ż╚ż╩ż├żŲżżżļĪŻ

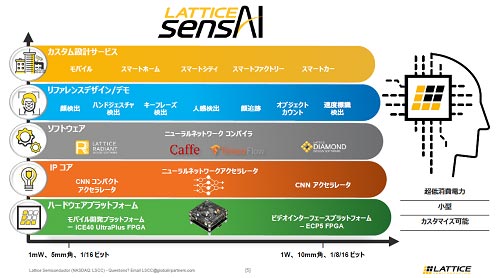

SensAIżŽIPź│źóż└ż▒żŪżŽż╩ż»ĪóźŽĪ╝ź╔ź”ź©źóż╚źĮźšź╚ź”ź©źóż╬│½╚»ź─Ī╝źļż“żĮżņżŠżņ─¾ČĪżĘżŲżżżļĪ╩┐▐2Ī╦ĪŻ│žØ{ż╣żļź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»ż╬źšźņĪ╝źÓź’Ī╝ź»ż╚żĘżŲż│żņż▐żŪżŽCaffeżĘż½×┤▒■żŪżŁż╩ż½ż├ż┐ż¼Īó║ŻövżŽTensorFlowż╦żŌ×┤▒■żŪżŁżļżĶż”ż╦ż╩ż├ż┐ĪŻź»źķź”ź╔żŪ│žØ{żĄżņżŲżżżļźšźņĪ╝źÓź’Ī╝ź»ż“LSIż╦═Ņż╚ż╣Šņ╣ńż╦żŽź│ź¾źčźżźķż╦żĶż├żŲĪóCaffeżóżļżżżŽTensorFlowż╬źšź®Ī╝ź▐ź├ź╚ż“LSIż╬└▀╝Ŗż╬RTLż╦╩č┤╣ż╣żļØŁ═ūż¼żóżļĪŻLatticeż¼─¾ČĪż╣żļźĮźšź╚ź”ź©źó│½╚»ź─Ī╝źļżŪżŽź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»ź│ź¾źčźżźķż“×óż©żŲż¬żĻĪóźµĪ╝źČĪ╝żŽRTLż╦╩č┤╣żĄżņż┐źŪĪ╝ź┐ż“╗╚ż”ż│ż╚ż¼żŪżŁżļĪŻLatticeżŽż│żņżķż╬ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»IPż“FPGAż╦ĮĖ└čżĘż┐Ę┴żŪĪóFPGAźŪźąźżź╣ż╚żĘżŲ╚╬Ūõż╣żļĪŻ

┐▐2ĪĪźĮźšź╚ź”ź©źóż╚źŽĪ╝ź╔ź”ź©źóż╬│½╚»źŁź├ź╚ż“─¾ČĪĪĪĮąųZĪ¦Lattice Semiconductor

IPź┘ź¾ź└Ī╝żŪżóżļImaginationżŽĪóżŌż┴żĒż¾źķźżź╗ź¾ź╣▓─ē”ż╩IPź│źóżŪĪó└Łē”żŽ╣ŌżżĪŻŠ├õJ┼┼╬üż╬Š«żĄż╩AX2145ż╬└Łē”żŽ1.0 TOPs (Tera Operations Per Second)żŌżóżĻż╩ż¼żķź┴ź├źūĀC└迎1mm2żĘż½ż╩żżż╚żżż”ĪŻ└Łē”═ź└Ķż╬AX2185żŽ║ŪĮj4.1 TOPsżŪGPUż“╬┐ż░└Łē”ż└ż╚żĘżŲżżżļĪŻAlexNetĪ╩└čŽ┬▒ķōQöv┐¶ż¼14.5▓»övĪ╦ż╬┐õéb└Łē”ż“╚µ│ėżĘż┐±T▓╠Īó“£═Ķż╬GPUż╚╚µż┘3.5Ū▄ż╬└Łē”ż¼żóż├ż┐ż╚żĘżŲżżżļĪŻź┴ź├źūĀC└迎2mm2ż╦ż╩żļż╚żżż”ĪŻ

├µ╣±ż╬▓┌░┘▓╩Č\╗▒▓╝ż╬HiSiliconżŌ┐õébAIż“│½╚»żĘżŲżżżļż¼Īó╚ÓżķżŽAppleż╬iPhone X/XPlusż╬źóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄA11ż╬2Ū▄ż╬└Łē”ż└ż╚Įęż┘żŲżżżļżķżĘżżĪŻImaginationż╦żĶżņżąĪóAX2145żŪżĄż©HiSilicon╩┬ż▀ż╬└Łē”żŪżóżĻĪó2185ż╚ż╩żļż╚ż│ż╬4Ū▄ż╬└Łē”ż“Ęeż─ż│ż╚ż╦ż╩żļĪŻ

╗▓╣═½@╬┴

1. B2B╗žĖ■ż¼£½│╬ż╦ż╩ż├ż┐CEATEC 2018 (1) (2018/10/17)

2. B2B╗žĖ■ż¼£½│╬ż╦ż╩ż├ż┐CEATEC 2018(3)Ī┴IoT/ź»źļź▐/Ę“╣»▌xŠņż╦Š╚ØŹ (2018/10/24)