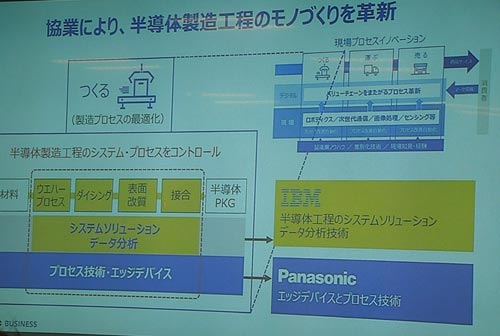

źūźķź║ź▐ź└źżźĘź¾ź░╣®µć░╩æTżŪźčź╩źĮź╦ź├ź»ż╚IBMż¼Č©Č╚

źčź╩źĮź╦ź├ź»ź│ź═ź»źŲźŻź├ź╔źĮźĻźÕĪ╝źĘźńź¾ź║Ī╩CNSĪ╦╝ęż╚Ų³╦▄IBMżŽĪó╚ŠŲ│öüĖÕ╣®µćż╬╩¼╠ŅżŪ─¾Ę╚żĘż┐Ī╩┐▐1Ī╦ĪŻż│żņżŽĪóźčź╩źĮź╦ź├ź»ż╬Ęeż─ĖÕ╣®µćż╬źūźķź║ź▐ź└źżźĘź¾ź░äóÅøż╚źūźķź║ź▐ź»źĻĪ╝ź╩äóÅøż╦IBMż╬FDCĪ╩Ė╬ŠŃ═Įē¶┤╔═²Ī╦źĮźšź╚ź”ź©źóż“┴╚ż▀╣■ż¾ż└äóÅøźĘź╣źŲźÓż╬│½╚»ż“ų`╗žż╣żŌż╬ĪŻ

┐▐1ĪĪČ©Č╚ż╣żļźčź╩źĮź╦ź├ź»(īÜ2ć@)ż╚Ų³╦▄IBM(║Ė2ć@)ĪĪĮąųZĪ¦źčź╩źĮź╦ź├ź»

źčź╩źĮź╦ź├ź»żŽĪóAEC/APC Symposiumż╩ż╔żŪż│żņż▐żŪ╚»╔Įż¼żóż├ż┐żĶż”ż╦ĪóźūźĒź╗ź╣äóÅøż╬źŪĪ╝ź┐ż“╝²ĮĖĪ”┤╔═²Ī”╩¼└ŽżĘżŲźšźŻĪ╝ź╔źąź├ź»ż¬żĶżėźšźŻĪ╝ź╔źšź®ź’Ī╝ź╔┼¬ż╦öUĖµż╣żļż│ż╚żŪ╩Ōé╬ż▐żĻĖ■æųĪóÖ┌ŠÅ└ŁĖ■æųż╦ż─ż╩ż▓żŲżŁż┐ĪŻźčź╩źĮź╦ź├ź»CNSżŽĪóż│żņż½żķż╬3D-ICżõFOWLPĪ╩Fan Out Wafer Level PackagingĪ╦ż╩ż╔ż╬Øi╣®µćż╚ĖÕ╣®µćż╬├µ┤ų╣®µćżŪżŽźūźĒź╗ź╣ż╬ź╬ź”źŽź”ż“Ö┌ż½żĘż┐äóÅøż╬źšźŻĪ╝ź╔źšź®ź’Ī╝ź╔öUĖµżõĖ╬ŠŃ═Įē¶ż╩ż╔ż¼Ąßżßżķżņżļż╚╚ĮéāżĘż┐ĪŻ

╚ŠŲ│öü×æļ]ż╬źŪĪ╝ź┐╩¼└ŽżŪżŽIBMżŽż│żņż▐żŪźūźĒź╗ź╣╣®µćżŪż╬╝┬└ėż¼żóżĻĪóØŖż╦MESĪ╩Manufacturing Execution System: ×æļ]╝┬╣įźĘź╣źŲźÓĪ╦źĮźšź╚ź”ź©źóżŪżŽ▌xŠņźĘź¦źóżŽ50%żŌÉ█ż├żŲżżżļż╚żżż”ĪŻIBM╦▄╝꿎╚ŠŲ│öüźūźĒź╗ź╣╣®µćż╬APCĪ╩Advanced Process ControlĪ╦żõFDCĪ╩Fault Detection and ClassificationĪ╦ż╩ż╔ż╬źŪĪ╝ź┐▓“└ŽźĘź╣źŲźÓżŪżŌ│░╚╬╝┬└ėż¼šl╔┘ż└ĪŻ

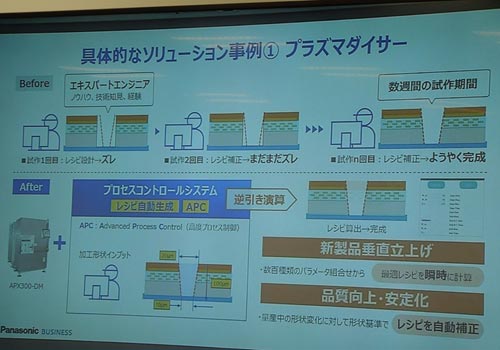

źčź╩źĮź╦ź├ź»ż¼įu┴Tż╚ż╣żļĖÕ╣®µćäóÅø(┐▐2)żŪżŌĪó3D-ICżõFOWLPż╩ż╔ż╬źčź├ź▒Ī╝źĖź¾ź░╣®µćżŽź”ź¦Ī╝źŽżĮż╬żŌż╬ż“▓├╣®ż╣żļż┐żßĪóØi╣®µćżŪ╝┬└ėż╬żóżļIBMż╚┴╚ż¾ż└ĪŻIBMżŽĪóAIź┴ź├źūż“żŽżĖżßż╚ż╣żļźŽźżź©ź¾ź╔ź┴ź├źūż╬╗Ņ║Ņż¼żŪżŁżļżĶż”ż╦×æļ]Č\Įčż╬Š}ż“┤╦żßżŲżŽżżż╩żżĪŻż┐ż└Īó╬╠ŠÅ╣®ŠņżŽGlobalFoundriesż╦£½ż▒┼ŽżĘĪó╬╠ŠÅČ\Įčż“Š}╩³żĘżŲżżżļĪŻ

┐▐2ĪĪ║Żövż╬─¾Ę╚żŪżŽ┤░└«żĘż┐ź”ź¦Ī╝źŽż“ź┴ź├źūż╦└┌żĻ╩¼ż▒żļĖÕ╣®µćżŪ┼¼├ōż╣żļĪĪĮąųZĪ¦źčź╩źĮź╦ź├ź»

źčź╩źĮź╦ź├ź»ż¼×æļ]ż╣żļźūźķź║ź▐ź└źżźĘź¾ź░äóÅøżŪżŽĪóź┴ź├źū┤ų│ų20µmżŪĖ³żĄ100µmż╬ź”ź¦Ī╝źŽż“ź└źżźĘź¾ź░ż╣żļż¼Ī󟔟¦Ī╝źŽæųż╬ź┴ź├źū┤ų│ų20µmżŪź”ź¦Ī╝źŽż╬öfĪ╩╬óĀCĪ╦żŪżŽ10µmż╚┤ų│ųż“ø]Į╠ż╣żļżĶż”ż╩źŲĪ╝źčĪ╝Ę┴ėXż¼╦Šż▐żĘżżż╚żĄżņżŲżżżļ(┐▐3)ĪŻż│ż╬ż┐żßż╦ź└źżźĘź¾ź░ż╣żļź┴ź├źūéāĀCżŽÄņ─Šż╦└┌żļż╬żŪżŽż╩ż»Īó’łŖAż¼ż─ż»żĶż”ż╦źūźķź║ź▐ź©ź├ź┴ź¾ź░ż╬Š“°Pż“öUĖµż╣żļĪŻż│żņż▐żŪżŽź©ź¾źĖź╦źóż¼źŲĪ╝źčĪ╝ż“ż─ż▒żļż╬ż╦╗Ņ╣įēžĖĒż“Ę½żĻ╩ųżĘż╩ż¼żķĪóżĮż╬Š“°Pż“»éżßżŲżŁż┐ż¼Īóż│żņż½żķżŽźūźĒź╗ź╣Š“°PżŪźņźĘźįż“ōQĮążĘżŲź½ź├ź╚żĘżŲżżż»ĪŻż│ż╬ż┐żßż╦żŽĪó┐¶╝å¹|╬Óż╬źčźķźßĪ╝ź┐ż╬┴╚ż▀╣ńż’ż╗ż½żķ║Ū┼¼ż╩źņźĘźįż“Įų╗■ż╦ōQĮążĘżŲżżż»ĪŻż│ż╬ōQĮąż“╣įż”ż┐żßż╬╩¼└Žź─Ī╝źļż“IBMż¼Š}²Xż▒żŲżżż»ĪŻ

┐▐3ĪĪźūźķź║ź▐ź└źżźĘź¾ź░żŪź┴ź├źū┤ų│ų10µmżŪź┴ź├źūż“╩¼▀`ż╣żļĪĪĮąųZĪ¦źčź╩źĮź╦ź├ź»

ż▐ż┐Īóźūźķź║ź▐ź»źĻĪ╝ź╩żŪżŽĪóźūźķź║ź▐╩³┼┼ż¼╔įŖW─Ļż╦ż╩żĻ░█Š’╩³┼┼ż¼╚»Ö┌ż╣żļżĶż”ż╦ż╩żļż╚Īó×æē俎╔į╬╔ēäż╦ż╩żļĪŻ┘抒ż╚░█Š’ż╬źŪĪ╝ź┐ż“Įj╬╠ż╦ŲDż├żŲż¬ż▒żąĖÕżŪ╩¼└Žż╦╗╚ż©żļĪŻäóÅøż╬ėX▌åż“ź╣ź│źóż╦żĘżŲźŪĪ╝ź┐╩¼└ŽżŪżŁżļżĶż”ż╩Ę┴ż╦żĘżŲż¬ż»ĪŻźŪĪ╝ź┐ż¼╩¼└ŽżŪżŁżļż╚ĪóäóÅøż¼ż╔ż╬żĶż”ż╩ėX▌åż╦ż╩żļż╚Ė╬ŠŃż╦╗Ļżļż╬ż½ż“ē¶żļż┐żßż╦ĪóźŪĪ╝ź┐źčź┐Ī╝ź¾ż“│žØ{żĘżŲż¬ż»ż╚ĪóĖ╬ŠŃ═Įē¶ż╦ż─ż╩ż¼żļĪŻźŪĪ╝ź┐ż“╩¼└Žż╣żļż╬ż¼IBMż╬╠“│õż└ĪŻ

„[─ĻĖ▄ĄężŽOSATżõĖÕ╣®µćż“Ęeż─╚ŠŲ│öüźßĪ╝ź½Ī╝ż└ĪŻäóÅøźßĪ╝ź½Ī╝ż╚żĘżŲźčź╩źĮź╦ź├ź»żŽĪóäóÅøż“╚╬ŪõżĘżŲż¬Į¬żżżŪżŽż╩ż»ĪóźĄĪ╝źėź╣ż“┤▐żßż┐źėźĖź═ź╣źŌźŪźļż“╣═ż©żŲżżż»ĪŻ▐k─Ļż╬│½╚»ż╬┐╩╩Ōż¼Ė½ż©ż┐żķĪó─╣┤³┼¬ż╦Ė▄Ąęż╚ż╬┤žĘĖż“╩▌ż─źėźĖź═ź╣żžż─ż╩ż▓żŲżżżŁż┐żżż╚źčź╩źĮź╦ź├ź»CNS╝ę╝ę─╣ż╬╚§Ė²£S╣įĢ■(┐▐1ż╬īÜż½żķ2╚ųų`)żŽĮęż┘żŲżżżļĪŻ