╚ŠŲ│öüż╬┐╩▓ĮĪ©╚∙║┘▓Įż½żķĀC└čź╣ź▒Ī╝źĻź¾ź░ĪóźžźŲźĒĮĖ└čĪóżĮż╬└ĶSi 4.0ż╚żŽ?

Si 1.0ż“ż│żņż▐żŪż╬╚∙║┘▓Įż╚ż╣żļż╚ĪóSi 2.0żŽTSMCż¼┐õżĘ┐╩żßżļĀC└čź╣ź▒Ī╝źĻź¾ź░ĪóżĮżĘżŲĪóSi 3.0żŽźžźŲźĒźūźĒź╗ź├źĄż╬ĮĖ└čČ\Įčż╚ż╩żĻĪóSi 4.0żŽźżź¾źŲźĻźĖź¦ź¾ź╣ż¼▓├ż’żļĪŻ±śŽč╚ŠŲ│öüż╬ébĄęĪóNicky LuĢ■ż¼Ė½żļ╠ż═Ķż╬╚ŠŲ│öüżŽĪóż│żņż▐żŪż╬┴Ē╣ńČ\Įčż“Ę¾ż═×óż©źżź¾źŲźĻźĖź¦ź¾ź╣ż“µ£ĀCż╦▓ĪżĘĮąż╣Si 4.0ż╚ż╩żļĪŻż│żņżŽØiĘŅ¼Źż╦»B┼į╣®Ę▌┴Ī░▌Įj│žżŪ╣įż’żņż┐KIT/Symetrix International SymposiumżŪ£½żķż½ż╦żĘż┐żŌż╬ĪŻ

┐▐1ĪĪEtron ▓±─╣Ę¾CEOż╬Nicky LuĢ■

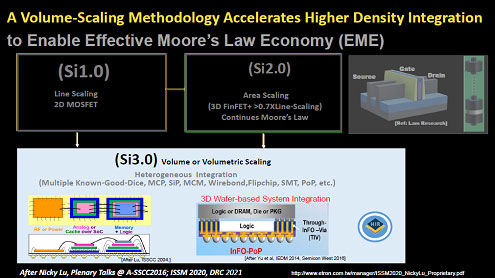

ØŖÖzźßźŌźĻż╬źšźĪźųźņź╣╚ŠŲ│öüEtronż╬CEOżŪżóżļLuĢ■żŽĪóż│żņż▐żŪżŌTSMCż╚Č©╬üżĘż╩ż¼żķ│½╚»ż“┐╩żßżŲżŁż┐ĪŻVLSIżŽGSIĪ╩Gaga Scale IntegrationĪ╦ż½żķTSIĪ╩Tera Scale IntegrationĪ╦ż╦2022ŃQż½żķ┐╩▓ĮżĘ╗Žżßż┐Īóż╚LuĢ■żŽĖņżĻĪóźĘźĻź│ź¾Č\Įčż╬źĒĪ╝ź╔ź▐ź├źūż“Si 1.0ż½żķSi 4.0ż▐żŪż“┐āżĘż┐ĪŻ

Si 1.0żŽźÓĪ╝źóż╬╦Īō¦żõźŪź╩Ī╝ź╔ż╬╦Īō¦ż╦żĶżļ╚∙║┘▓ĮżŪż╬╣ŌĮĖ└č▓Įż“╔Įż╣ĪŻ╚∙║┘▓ĮżŽżóż»ż▐żŪżŌŪ█└■└■╔²żõŪ█└■┤ų│ųż╬ź╣ź▒Ī╝źĻź¾ź░żŪĪó║ŪŠ«└■╔²ż¼ĮjżŁż╩┴T╠Żż“Ęeż├żŲżżż┐ĪŻżĮżņż¼║ŪŖZĪó7nmźļĪ╝źļż╬└▀╝Ŗż╚żżż├żŲżŌź┴ź├źūæųż╬ż╔ż│ż╦żŌ7nmż╚żżż”źĄźżź║żŽż╩żżĪŻTSMCż╬7nmźūźĒź╗ź╣ź╬Ī╝ź╔żŽIntelż╬10nmź╬Ī╝ź╔ż╦┼∙żĘżżż╚żżż’żņżŲżżżļż│ż╚żŽż╔ż”żżż”ż│ż╚ż╩ż╬ż½Īó╔«ŪvżŽżĘżążķż»═²▓“żŪżŁż╩ż½ż├ż┐ĪŻLuĢ■żŽżĮżņż“ź║źąźĻĪóTSMCżŽ╚∙║┘▓Įż½żķĀC└čź╣ź▒Ī╝źĻź¾ź░ż╦╩čż©ż┐Īóż│żņż¼Si 2.0ż└Īóż╚Įęż┘żŲżżżļĪŻ

ĀC└čź╣ź▒Ī╝źĻź¾ź░żŽĪóFinFETż╬żĶż”ż╩3╝ĪĖĄź╚źķź¾źĖź╣ź┐ż¼ĮĖ└čövŽ®ż╦╗╚ż’żņżļżĶż”ż╦ż╩ż├żŲż½żķ╗Žż▐ż├ż┐ĪŻFin FETżŽŲ³╬®×æ║ŅĮĻż╬╚»£½żŪżóżļż│ż╚ż“LuĢ■żŽ’w┴Tż“╔ĮżĘżŲĮęż┘żŲżżżļĪŻFinFETżŽĪó╩┐ĀCż╬ź╚źķź¾źĖź╣ź┐ż“źąźļź»ż╬źĘźĻź│ź¾ż½żķ▓ŻöĄĖ■ż╦äėöU┼¬ż╦Į╠╣■żßż┐żĶż”ż╩Ę┴ż“żĘżŲżżżļż┐żßĪóź╚źķź¾źĖź╣ź┐ż╬╩┐ĀCėXż╬ĀC└čż“Š«żĄż»żŪżŁżļĪŻź╚źķź¾źĖź╣ź┐ż╚Ų▒══ż╦Ū█└■żŌA┼└ż╚B┼└ż“╩┐ĀCæųżŪ└■ż“±Tżųż╬żŪżŽż╩ż»ĪóA┼└ż╚B┼└ż“żŌż├ż╚ŖZż┼ż▒żŲĪó¾H┴žŪ█└■ż“╗╚żż╬®öü┼¬ż╦±Tżųż│ż╚żŪĪóŪ█└■╔²ż“žōżķż╣ż│ż╚ż╩ż»╩┐ĀCæųż╬Ū█└■ōļ░Ķż“Š«żĄż»ż╣żļż│ż╚ż¼żŪżŁżļĪŻż│ż”żżż├ż┐║ŅČ╚ż¼ĀC└čź╣ź▒Ī╝źĻź¾ź░żŪżóżļĪŻŪ█└■╔²ż¼║ŪżŌČ╣żżĮĻżŪżŌ15nmØiĖÕżŪż╚ż╔ż▐ż├żŲżżżļż╬żŽĪó╩┐ĀCæųż╬ĀC└čż“Š«żĄż»żĘżŲżżżļż½żķż└ĪŻż│żņżķż╬Š▄║┘żŽĪó28Ų³ż╦│½╠¢ż╣żļź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ▓±µ^Ė┬─ĻFree WebinarĪųTSMCĖ”ē|ĪūżŪŠę▓ż╣żļĪŻ

LuĢ■ż¼Si 3.0ż╚Ō}żųż╬żŽĪ󿥿▐żČż▐ż╩░█ż╩żļź┴ź├źūż“Ų▒▐k┤łæųż╦ĮĖ└čż╣żļźžźŲźĒźżź¾źŲź░źņĪ╝źĘźńź¾żŪżóżļĪ╩┐▐2Ī╦ĪŻż│żņżŽ3╝ĪĖĄż╦ź╣ź┐ź├ź»ż╣żļżĶż”ż╩3D-ICż“┤▐żÓĪóöü└čź╣ź▒Ī╝źĻź¾ź░ż└ż╚─Ļ▒IżĘżŲżżżļĪŻ

┐▐2ĪĪSi 3.0żŽźžźŲźĒĮĖ└č▓Įż╬╗■┬Õż╦ż╩żļĪĪĮąųZĪ¦Etron Nicky LuĢ■

TSMCżŽż│żņż▐żŪżŌInFOĪ╩Integrated Fan-OutĪ╦-PoPĪ╩Package on PackageĪ╦ż╚Ō}żążņżļźšźĪź¾źóź”ź╚Ī”ź”ź¦Ī╝źŽźņź┘źļźčź├ź▒Ī╝źĖż╚DRAMźčź├ź▒Ī╝źĖż“┼ļ║▄ż╣żļ3╝ĪĖĄźčź├ź▒Ī╝źĖČ\Įčż“│½╚»żĘżŲżŁż┐ĪŻźĒźĖź├ź»ź┴ź├źūż“║ŲŪ█└■┴žż╬╠“│õż“▓╠ż┐ż╣źżź¾ź┐Ī╝ź▌Ī╝źČż“▓żĘżŲ│░ŗ├╝╗ężžż╚ż─ż╩ż▓żļźčź├ź▒Ī╝źĖæųż╦DRAMźčź├ź▒Ī╝źĖż“żĮż╬æųż╦┼ļ║▄ż╣żļĪŻ

żĮżņżķż╬źŌź╬źĻźĘź├ź»ż╩╚∙║┘ź╬Ī╝ź╔ż╬ź┴ź├źūżõĪóźžźŲźĒĮĖ└čĪ╩HIĪ╦ż╩ż╔ż╬Č\Įčż“┐╩▓ĮżĄż╗ż┐Č\Įčż“╗╚ż├żŲ┐═┤ųż╦ŖZżżē¶ē”Ī╩IntelligenceĪ╦ż“×óż©ż┐Siź┴ź├źūż“Si 4.0ż╚─Ļ▒IżĘżŲżżżļĪŻż│żņżķżŽĪóAIĪ▀IoTĪ▀HIĪ▀ICĪ▀╚ŠŲ│öüż╚żĘżŲ╔ĮĖĮżĘżŲżżżļĪ╩┐▐3Ī╦ĪŻ

┐▐3ĪĪSi 4.0żŽ┴Ē╣ńČ\Įčż╬źżź¾źŲźĻźĖź¦ź¾ź╚ż╩ICźŽĪ╝ź╔ź”ź©źóż╚ż╩żļĪĪĮąųZĪ¦Etron Nicky LuĢ■

┐═┤ųż╬Ų¼╦Nż“╠ŽżĘż┐AIżõź│ź¾źįźÕĪ╝źŲźŻź¾ź░ĪóźßźŌźĻż╚Īó┐└Ęąż╬┴Ļ┼÷ż╣żļ─╠┐«źżź¾ź┐Ī╝źšź¦źżź╣Ī╩USB4.0żõSerDesż╩ż╔Ī╦Īóų`ż╚żżż”£å│ąź╗ź¾źĄż½żķż╬Š╩¾ż“Ū¦╝▒żĘĮĶ═²ż╣żļźėźĖźńź¾ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Ī╩VR/AR▓ĶćĄÖ┌└«Ī╦Īóź╗źŁźÕźĻźŲźŻĪ╩źūźķźżźąźĘĪ╝ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Ī╦ż╩ż╔ż“īÖ├ōż╣żļĪŻ¾Hż»ż╬╝ę▓±╠õ¼öż“▓“»éż╣żļżĶż”ż╩źĮźĻźÕĪ╝źĘźńź¾ż“─¾ČĪż╣żļĪŻż│ż╬║óż╦żŽ╚ŠŲ│öüżŽźĄźųźĘź╣źŲźÓż╚ż╩ż├żŲż¬żĻĪóźĮźšź╚ź”ź©źóż“┤▐żßż┐źĘź╣źŲźÓż“╝┬╣įż╣żļźŽĪ╝ź╔ź”ź©źóż╦ż╩ż├żŲżżżļĪŻ2020ŃQ┬Õż½żķ2035ŃQż┤żĒż▐żŪSi 4.0ż╬╗■┬ÕżŽ¶öż»ż╚LuĢ■żŽĖ½żŲżżżļĪŻ