źūźĻź¾ź╚┤łż╚╚ŠŲ│öüż¼└▄ŖZĪó└Ķ├╝źčź├ź▒Ī╝źĖż╦ÅR╬üż╣żļģ╬═█HD

źūźĻź¾ź╚övŽ®┤łż╬źĮźļź└Ī╝źņźĖź╣ź╚ż╬║ŪĮjŠ}żŪżóżļģ╬═█ź█Ī╝źļźŪźŻź¾ź░ź╣ż¼╚ŠŲ│öü╩¼╠Ņż╦╗▓Ų■ż╣żļĪŻżĮżņżŌ└Ķ├╝źčź├ź▒Ī╝źĖż╬źżź¾ź┐Ī╝ź▌Ī╝źČČ\Įčżžż╬▒■├ōż“┴└ż├ż┐źĮźļź└Ī╝źņźĖź╣ź╚ż╚ż╩żļĪŻźĮźļź└Ī╝źņźĖź╣ź╚żŽźūźĻź¾ź╚┤łæųż╬£u┐¦żĘż┐█`╗ķżŪĪó╚ŠŲ│öüż╩ż╔ż╬ŗēäż“└▄¶öż╣żļČŌō’┼┼Č╦░╩│░ż╬µ£żŲż“╩▌ĖŅż╣żļż╚żżż”╠“│õż“Ęeż─ĪŻ

ģ╬═█źżź¾źŁ×æļ]ż¼Ęeż┴│¶▓±╝ężŪżóżļģ╬═█ź█Ī╝źļźŪźŻź¾ź░ź╣Ī╩HDĪ╦ż╚ż╩ż├ż┐ż╬żŽ2010ŃQĪŻ░╩═ĶĪó╣±ŲŌżŪ6╝ęż“Ń~ż╣żļż█ż½ĪóķL│░╦Ī┐═ż“9╝ęĘeż├żŲżżżļĪŻĄ£Č╚ż╬├µ│╦żŽĪóźĮźļź└Ī╝źņźĖź╣ź╚żŪ║ŪĮjŠ}ż└ż¼ĪóAppleż╬iPhoneż╦║╬├ōżĄżņż┐ż│ż╚żŪĮjżŁż»└«─╣żĘż┐ĪŻźūźĻź¾ź╚┤łČ╚─cżŪżŽŃ~ć@ż╩ÅBż└ż¼ĪóAppleż╬CEOż└ż├ż┐Ė╬Steve JobsĢ■ż¼źūźĻź¾ź╚┤łæųż╦żŽ▌üżż╩▌ĖŅ╦ņż╦ż│ż└ż’żĻĪó▌üżżźĮźļź└Ī╝źņźĖź╣ź╚ż“│½╚»żŪżŁż┐ģ╬═█źżź¾źŁż╬×æēäż“├ōżżż┐ż│ż╚ż¼║ŪŖZż╬└«─╣ż╬ĖČ┼└ż╚ż╩ż├żŲżżżļĪŻ

źĮźļź└Ī╝źņźĖź╣ź╚ż╚Ė└ż©żąĪó╚ŠŲ│öüČ╚─cż╬öĄż╦żŽźšź®ź╚źņźĖź╣ź╚ż“źżźßĪ╝źĖżĘżŲżĘż▐ż”ż¼Īóźšź®ź╚źņźĖź╣ź╚ż╚ż╬║ŪĮjż╬░ŃżżżŽĪóźčź┐Ī╝ź╦ź¾ź░żĘż┐ĖÕżŌźņźĖź╣ź╚ż“Į³ĄŅż╗ż║ż╦╗─ż╣ż│ż╚ĪŻ╗─ż├ż┐źĮźļź└Ī╝źņźĖź╣ź╚ż¼╩▌ĖŅ╦ņż╚ż╩żļĪŻż▐ż┐ĪóźĮźļź└Ī╝źņźĖź╣ź╚ż“╣┼▓ĮżĄż╗ż┐ĖÕĪ󟎟¾ź└ż╬═ßŌÅż╦┐╗ż▒żŲżŌ┼┼Č╦ČŌō’ŗ╩¼ż╦źŽź¾ź└ż¼¤²ż»ż¼ĪóżĮżņ░╩│░ż╬ōļ░Ķż╦żŽźŽź¾ź└żŽ¤²ŠÆżĘż╩żżĪŻż│ż╬ż┐żßĪóźĮźļź└Ī╝źņźĖź╣ź╚ż╦ä┘ż’żņż┐ŗ╩¼ż¼Ū█└■ż╬╩▌ĖŅ╦ņż╚ż╩żļĪŻż│ż╬ż┐żß└õ▒’╦ņż╬┐«═Ļ└Łż¼╠õż’żņżļż│ż╚ż╦ż╩żļĪŻ

źūźĻź¾ź╚övŽ®┤łżŪżŽĪóżŌż╚żŌż╚Ū█└■╔²ż¼┐¶╝åµmż╚╚ŠŲ│öüż╬Ū█└■╔²ż╬1µm░╩▓╝ż╚żŽµ£ż»░ŃżżĪó░§║■Č\Įčż“╗╚ż├żŲżżż┐ĪŻżĘż½żĘĪóIntelżõSoCźßĪ╝ź½Ī╝ż╬ź┴ź├źūż╬źčź├ź▒Ī╝źĖż¼źĻĪ╝ź╔źšźņĪ╝źÓżŪżŽż╩ż»źūźĻź¾ź╚┤łż“╗╚ż”żĶż”ż╦ż╩ż├ż┐║óż½żķĪó100µmż½żķ50µmżžż╚╝Īŗīż╦źūźĻź¾ź╚övŽ®ż╬Ū█└■╔²ż╬╚∙║┘▓Įż¼┐╩ż▀Īó╚ŠŲ│öüż╬żĮżņż╦ŖZż┼żŁ╗ŽżßĪó░§║■ż½żķźšź®ź╚źĻźĮź░źķźšźŻČ\Įčżžż╚öĪ╣įżĘżŲżŁż┐ĪŻżĮżĘżŲĪó└Ķ├╝źčź├ź▒Ī╝źĖż╬źĄźųź╣ź╚źņĪ╝ź╚żõźżź¾ź┐Ī╝ź▌Ī╝źČż╩ż╔ż╬Ū█└■╔²ż╚ż╩żņżą┐¶µmźņź┘źļżžż╚╚∙║┘▓ĮżĘĪó╚ŠŲ│öüźūźĒź╗ź╣Č\Įčż╦ŖZż┼żżżŲżŁż┐ĪŻ

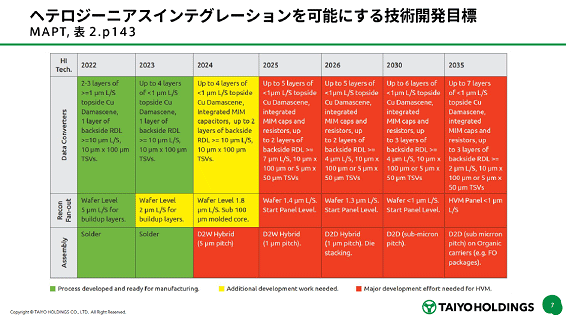

┐▐1ĪĪSRCż¼╚»╔ĮżĘż┐MAPTźĒĪ╝ź╔ź▐ź├źūż╬▐kŗĪĪĮąųZĪ¦SRCĪóģ╬═█HD

ä▌SRCĪ╩Semiconductor Research Corp.Ī╦żŽĪó║“ŃQMAPTĪ╩Microelectronics and Advanced packaging TechnologiesĪ╦źĒĪ╝ź╔ź▐ź├źūż“╚»╔ĮĪ╩╗▓╣═½@╬┴1Ī╦Īó3D-ICżõ└Ķ├╝źčź├ź▒Ī╝źĖż╬Įø═Ķżžż╬╠OČ┌ż“ż─ż▒ż┐Ī╩┐▐1Ī╦ĪŻ2023ŃQż▐żŪż╬źĒĪ╝ź╔ź▐ź├źūż╚ż╩ż├żŲżżżļĪŻż│żņż╦żĶżļż╚Ū█└■╔²ż╚Ū█└■┤ų│ųĪ╩L/SĪ╦żŪżŽ1µmżŪ4┴žĪó╬óĀC║ŲŪ█└■┴ž1┴žż¼10µmż╚żżż”źūźĒź╗ź╣ż¼Ö┌ŠÅØŹ×ó├╩│¼ż╦═ĶżŲżżżļż╚żżż”ĪŻżĘż½żŌĪóŲ╝Ū█└■żŽ“£═Ķż╬źßź├źŁżŪżŽż╩ż»╚ŠŲ│öüżŪ╗╚ż├żŲżżżļź└ź▐źĘź¾źūźĒź╗ź╣ż╦┬Õż’ż├żŲżżżļĪŻ

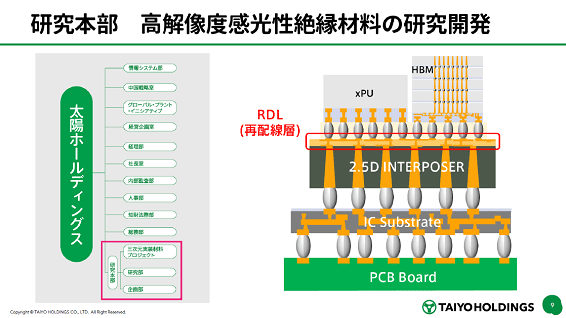

┐▐2ĪĪźżź¾ź┐Ī╝ź▌Ī╝źČż╬║ŲŪ█└■┴ž║Ó╬┴ż╦ÅR╬üĪĪĮąųZĪ¦ģ╬═█HD

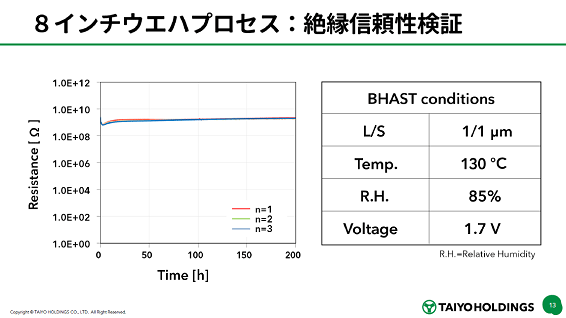

ģ╬═█HDżŪżŽĪóįÆ╝ĪĖĄ╝┬äó║Ó╬┴źūźĒźĖź¦ź»ź╚ż╚żżż”┴╚“Eż“║ŅżĻĪó║ŲŪ█└■┴žRDLĪ╩Re-Distribution LayerĪ╦ż╦ż¬ż▒żļ╣Ō▓“ćĄ┼┘ż╬┤ČĖ„└Ł└õ▒’║Ó╬┴ż╬│½╚»ż╦╬üż“Ų■żņ╗Žżßż┐Ī╩┐▐2Ī╦ĪŻż│ż╬ż█ż╔8źżź¾ź┴ź”ź¦Ī╝źŽżŪ21Ė─ż╬ź┴ź├źū╝┬äóōļ░Ķż╬źųźĒź├ź»ż“║ŅżĻĪóL/Sż¼1µmż╬źčź┐Ī╝ź¾ż“ķWż»╝┬┘xż“└«Ė∙żĄż╗żŲżżżļĪŻżĄżķż╦ż│ż╬8źżź¾ź┴ź”ź¦Ī╝źŽż╬└õ▒’╗Ņ┘xżŌ╣įżżĪóźąźżźóź╣┼┼░Ą1.7VĪó130°CĪó┴Ļ×┤╝Š┼┘85%ż╬╣Ōča╣Ō╝Šźąźżźóź╣╗Ņ┘xżŪ200╗■┤ųż▐żŪ└õ▒’└Łż¼╩▌ż┐żņżŲżżżļż╚żżż”±T▓╠ż“įużŲżżżļĪ╩┐▐3Ī╦ĪŻ

┐▐3ĪĪ╣Ōča╣Ō╝Šźąźżźóź╣╗Ņ┘xżŪżŽ└õ▒’└Łż╬╬¶▓ĮżŽĖ½żķżņż╩żżĪĪĮąųZĪ¦ģ╬═█HD

ģ╬═█HDżŽ║ŻĖÕĪó300mmź”ź¦Ī╝źŽżŪż╬ĖĪŠ┌╝┬┘xż╦ŲDżĻ┴╚ż¾żŪżżż»ĪŻżĄżķż╦Īó└ż─c┼¬ż╩╚ŠŲ│öüĖ”ē|ĮĻżŪżóżļź┘źļź«Ī╝ż╬imecż╬3DźūźĒź░źķźÓż╦╗▓▓├żĘĪóRDLČ\Įčż╬╚∙║┘▓Įż╬Č”Ų▒│½╚»ż╦ŠÆŠ}żĘż┐ż╚żżż”ĪŻ

╗▓╣═½@╬┴

1. "Microelectronics and Advanced Packaging Technologies Roadmap", SRC