ØŖĮĖĪ¦▒č╣±│¶╝░▓±╝ę (4)ź▐źļź┴ź│źóDSPżŪ╠Ą└■źżź¾źšźķ▌xŠņżž

║Żż½żķ2000ŃQż█ż╔ØiĪóźĒĪ╝ź▐┐═ż¼Ü¦Ū█żĘżŲżżż┐źżź«źĻź╣ŲŅūÄŗż╬ÅžźąĪ╝ź╣Ī╩BathĪ╦żŽĪóča└¶ż¼═»żŁż¬╔„Žżż╬ĖņĖ╗ż╦żŌż╩ż├ż┐ÅžżŪżóżļĪŻż│ż│ż╦└ż─cż╬╚ŠŲ│öüźßĪ╝ź½Ī╝żõźĘź╣źŲźÓźßĪ╝ź½Ī╝ż“┴ĻŠ}ż╦ż╣żļĪó╣{żż╚ŠŲ│öüźšźĪźųźņź╣┤ļČ╚ż¼żóżļĪŻ┴Ž╬®7ŃQż╬picoChip Designs╝ęż╬Ęą▒─┐žżŽź░źĒĪ╝źąźļż╩┤ļČ╚ż½żķżõż├żŲżŁż┐┐═ż┐ż┴ż¼░Ą┼▌┼¬ż╦¾HżżĪŻOak TechnologyĪóIBM MicroelectronicsĪóCadence Design SystemsĪóConexant SystemsĪóAgere SystemsĪóVodafoneĪóAnalog Devicesż╩ż╔└ż─cĘQ├Žż╬┤ļČ╚ż½żķĮĖż▐ż├żŲżżżļĪŻ

picoChip╝ęż¼įu┴Tż╚ż╣żļ×æē俎Īóź’źżźõźņź╣╩¼╠Ņż╦ØŖ▓ĮżĘż┐ź▐źļź┴ź│źóDSPźūźĒź╗ź├źĄż└ĪŻĪų╗╚żżżõż╣ż»Īóź│ź╣ź╚Ī”źčźšź®Ī╝ź▐ź¾ź╣ż¼żĶż»─ŃŠ├õJ┼┼╬üżŪżóżĻĪómWżóż┐żĻż╬MIPS└Łē”żŽ“£═Ķż╬DSP×æēäż╚╚µż┘żŲ10Ī┴40Ū▄═źżņżŲżżżļĪūż╚Ų▒╝ęź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷╔¹╝ę─╣ż╬Rupert BainesĢ■żŽżżż”ĪŻŲ▒Ģ■żŽ▓żä”Įj╬”ż╬Atlantic TelecomĪóżĮż╬ØiżŽä▌Analog Devicesż╦żŌżżż┐ĪŻ

┴└ż”▌xŠņżŽĪóź╗źļźķĪ╝┼┼ÅBż╬3G░╩æTż╬HSDPAĪóHSUPAĪóLTEĪóźšź¦źÓź╚ź╗źļż╩ż╔ż╬ź╗źļźķĪ╝ź═ź├ź╚ź’Ī╝ź»ż╦▓├ż©ĪóWiMAXź═ź├ź╚ź’Ī╝ź»ż╩ż╔┐ʿʿż╣ŌÅ]ź═ź├ź╚ź’Ī╝ź»ż╬┤├ŽČ╔Ė■ż▒ź┴ź├źūżŪżóżļĪŻØŖż╦Īó║ŪŖZÅRų`żĄżņżŲżżżļźšź¦źÓź╚ź╗źļĖ■ż▒ż╦żŽż│żņż▐żŪż╬żĶż”ż╩╣Ō▓┴ż╩DSPżŽ╗╚ż©ż╩żżĪŻźšź¦źÓź╚ź╗źļżŽ▓╚─Ēżõź¬źšźŻź╣żŪ╗╚ż”Š«żĄż╩┤├ŽČ╔ż└ż½żķżŪżóżļĪŻż╗żżż╝żż▓╚─Ē├ōźļĪ╝ź┐Ī╝µć┼┘ż╬▓┴│╩ż╦Ū╝żßż╩ż▒żņżąż╩żķż╩żżĪŻ

╝┬żŽĪóBainesĢ■ż¼Įęż┘ż┐ż│ż╬┐¶ÖCżŽŗīįÆŪvż╬äh▓┴ĄĪ┤žżŪżóżļBDTI(źąĪ╝ź»źņźżĪ”źŪźČźżź¾Ī”źŲź»ź╬źĒźĖĪ╝╝ę)ż¼ź┘ź¾ź┴ź▐Ī╝ź»źŲź╣ź╚żĘż┐żŌż╬żŪĪópicoChip╝ęż╬║ŪĮķż╬×æēäPC102ż╚ĪóTexas Instruments╝ęż╬źŽźżź©ź¾ź╔DSP×æēäTMS320C6455ż“1GHzżŪŲ░║ŅżĄż╗ĪóFreescale Semiconductorż╬DSPĪĪMPC8144ż“1GHzżŪŲ░║ŅżĄż╗żŲ╚µ│ėżĘż┐żŌż╬ĪŻPC102żŽ160MHzżŪŲ░║ŅżĄż╗ż┐ĪŻ└õ×┤┼¬ż╩└Łē”żŌĪóź┘ź¾ź┴ź▐Ī╝ź»Ī”ź┴źŃź¾ź═źļ┐¶Īóź┴źŃź¾ź═źļ┼÷ż┐żĻż╬ź│ź╣ź╚ż╩ż╔żŪ╚µ│ėżĘżŲżżżļĪŻź╦źÕĪ╝ź╣źĻźĻĪ╝ź╣ż¼ĮążŲżżżļĪ╩http://www.picochip.com/press/press_releases/press099Ī╦ĪŻ

picoChipżŽ├▒ż╩żļźšźĪźųźņź╣ż╬╚ŠŲ│öü┤ļČ╚żŪżŽż╩żżĪŻź┴ź├źū│½╚»ż╦ØŁ═ūż╩źņźšźĪźņź¾ź╣źŪźČźżź¾ź▄Ī╝ź╔żõĪó3G/WiMAXĪóLTEż╣ż┘żŲż“ź½źąĪ╝ż╣żļźĮźĻźÕĪ╝źĘźńź¾ż▐żŪżŌ─¾ČĪż╣żļĪŻ╚ŠŲ│öüź┴ź├źūżĮż╬żŌż╬ż╬└Łē”ż¼╬╔żżż└ż▒żŪżŽż╩żżĪŻźĮźšź╚ź”ź©źó╠Ą└■öĄ╝░żŪżóżļż┐żßĪóź┘Ī╝ź╣źąź¾ź╔└▀╝Ŗż“źĮźšź╚ź”ź©źóż└ż▒żŪ╩čśŗżŪżŁżļĪŻż└ż½żķĪó3GżõLTEż╦ż╩żĒż”ż¼ĪóWiMAXż╦ż╩żĒż”ż¼┤žĘĖż╩ż»ż╔ż┴żķż╦żŪżŌ×┤▒■żŪżŁżļĪŻ

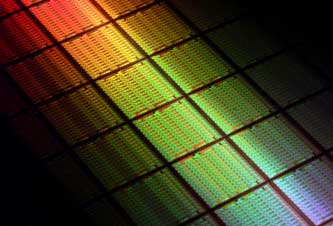

DSPź┴ź├źūż╚żĘżŲżŽĪó╣Ō└Łē”Ī”─Ń▓┴│╩Ī”źšźņźŁźĘźėźĻźŲźŻż╚įÆŪ’╗ę×óż©ż┐╚ŠŲ│öüżŪżóżļĪŻŲ▒╝꿎ż▐ż└ź┘ź¾ź┴źŃĪ╝ż╚żżż©żļżĶż”ż╩Š«żĄż╩┤ļČ╚żŪĪóźąĪ╝ź╣ż╦╦▄╝ęż“ÅøżŁĪ󵣓£Č╚µ^żŽ130ć@µć┼┘ż└ĪŻż│ż│ż╦90┐¶ć@ż█ż╔ĮĖżżĪó30ć@µć┼┘ż¼└ż─cĘQ├Žż╬ź╗Ī╝źļź╣ź¬źšźŻź╣Ī╩Ē×»BĪó┼ņ»BĪóź▄ź╣ź╚ź¾ĪóźĮź”źļĪ󟥟¾źĖź¦ź┤ż╩ż╔Ī╦ż╦żżżļĪŻź┘ź¾ź┴źŃĪ╝źŁźŃźįź┐źļż½żķ4övż╦┼Žżļ═╗½@ż“£pż▒żŲżŁż┐ĪŻČ\Įčźóź╔źąźżźČźĻź▄Ī╝ź╔ż╦żŽĪóXMOS Semiconductor╝ęż╬┴Ž╬®ŪvżŪżŌżóżļDavid MayźųźĻź╣ź╚źļĮj│žČĄĶbĪ╩▒č╣±ØŖĮĖĪ╩2Ī╦ż“╗▓Š╚Ī¦Ī╦żŌć@ż“Žóż═żŲżżżļĪŻ

130nmźļĪ╝źļżŪ║Ņż├ż┐║ŪĮķż╬ź┴ź├źūPC102żŽ2004ŃQż╦10~20╦³Ė─Ö┌ŠÅżĘĪó║ŻżŽ90nmż╬ŗī2└ż┬Õź┴ź├źūżŽ2006ŃQż╦╚»ŪõżĘż┐ĪŻ╩Å╝ŖżŪ100╦³Ė─ż╦żŌ├Żż╣żļż╚żżż”ĪŻ║ŻŃQ╚»Ūõż╣żļź┴ź├źūżŽ65nmźļĪ╝źļżŪ║ŅżļPC20xĪóPC302/305ż“═Į─ĻżĘżŲżżżļĪŻēä¹|ż“żżż»ż─ż½└▀ż▒żŲżżżļż╬żŽĪóĮjżŁż╩┤├ŽČ╔ż½żķźšź¦źÓź╚ź╗źļż▐żŪ╣Łż»ź½źąĪ╝ż╣żļż┐żßżŪżóżļĪŻ

picoChip╝ęż╬ź▐źļź┴ź│źóDSPź┴ź├źūżŽ1ź┴ź├źūæųż╦16źėź├ź╚ż╬DSPź│źóż“┐¶╝åĖ─╩┬š`ż╦╩┬ż┘ż┐╣Įļ]ż“żŌż─ĪŻź▐źļź┴ź│źóż╦żĘż┐═²ĮyżŽĪóźĘź¾ź░źļź│źóżŪ└Łē”ż“æųż▓żļŠņ╣ńż╦ź╚źķź¾źĖź╣ź┐┐¶Īóż╣ż╩ż’ż┴ź┴ź├źūĀC└čż¼╗\▓├żĘżŲżĘż▐ż”ż┐żßż└ĪŻ2007ŃQż╦Intel╝ęż¼╩¼└Ž─┤ØhżĘż┐±T▓╠ĪóMIPS┐¶żŪ└Łē”ż“2Ū▄ż╦æųż▓żļż╬ż╩żķź╚źķź¾źĖź╣ź┐ĀC└迎3Ū▄ż╦╗\ż©ĪóŻ┤Ū▄ż╦æųż▓żņżą9Ū▄ż╦żŌ╗\ż©żŲżĘż▐ż”ż│ż╚ż¼ż’ż½ż├ż┐ĪŻ

picoChip╝꿎Īó═²„[┼¬ż╩DSPż“╩¼└ŽżĘĪó▓┐ź╚źķź¾źĖź╣ź┐żŪ▓┐MIPSż╬DSPż¼1Ė─ż╬DSPź│źóż╚żĘżŲź┘ź╣ź╚ż╩ż╬ż½ż“ĖĪŲżżĘż┐ĪŻżĮż╬±T▓╠Īó16źėź├ź╚ż╬DSPź│źóżŪ100Ī┴200MHzżŪŲ░║ŅżĄż╗ż┐Īó3ź”ź©źżVLIWźóĪ╝źŁźŲź»ź┴źŃż¼║Ū┼¼ż└ż╚Ė½ĮążĘż┐ĪŻż│ż╬ź│źóż“║ŪŠ«ż╬źėźļźŪźŻź¾ź░źųźĒź├ź»├▒░╠ż╚żĘżŲĪó300Ė─µć┼┘╩┬š`Ų░║Ņż╣żļź▐źļź┴ź│źóDSPż“└▀╝ŖżĘż┐ĪŻ║ŪĮķż╬ź┴ź├źūżŪżóżļPC102(130nmźūźĒź╗ź╣)żŪżŽĪó308Ė─ż╬DSPź│źóż“ĮĖ└čżĘż┐ĪŻż│ż╬ź┴ź├źūż╬└Łē”żŽĪ󟻟Ēź├ź»╝■āS┐¶160MHzżŪĪó197GIPSĪ╩giga instructions per secondĪ╦Īó└čŽ┬▒ķōQÅ]┼┘żŽ38.6GMACsĪóźßźŌźĻĪ╝ż╬┼Š┴„Å]┼┘żŽ3.3Tźėź├ź╚/╔├ż╚Č╦żßżŲ╣Ōżż└Łē”ż“┐āżĘż┐ĪŻż┐ż└żĘĪóŗī▐k└ż┬Õ×æēäż╬PC102ż╬Š├õJ┼┼╬üżŽ5Wż╚żõżõĮjżŁżżĪŻ

└Łē”żŽDSPź│źóż╬┐¶ż╦╚µ╬Ńż╣żļż¼ĪóĀC└čżŌżĮż╬╩¼ĮjżŁż»ż╩żļĪŻż│ż╬PC102ż“4Ė─╩┬ż┘DSPż“1200Ė─ż╬ź│źóż╦╩┬š`Ų░║ŅżĄż╗żļż╚Īó800GIPSż╦ż╩żļż╚żĘżŲżżżļĪŻ║ŪżŌĮjżŁż╩æä╠Žż╬Š”├ōźĘź╣źŲźÓżŽ4800Ė─ż╬DSPź│źóżŪ3.3TIPSż╚żżż”└Łē”ż“┐āżĘż┐ĪŻż┴ż╩ż▀ż╦ĖĮ║▀Įą▓┘├µż╬PC202żŽ90nmźūźĒź╗ź╣żŪ×æļ]żĘżŲż¬żĻĪó20Ī┴30ź╔źļµć┼┘ż╬▓┴│╩ż└ż╚żżż”ĪŻ

Ų▒żĖĄĪē”ż“FPGAżŪ╝┬ĖĮżĘżĶż”ż╚ż╣żļż╚ĪóĀC└čĖ·╬©żŽĄKżżĪŻFPGAżõ“£═Ķż╬DSPż╚╚µ│ėż╣żļż╚źĘźĻź│ź¾ĀC└č┼÷ż┐żĻż╬└Łē”Ī╩▒ķōQ┐¶/mm2Ī╦żŽ└ņ├ōż╬ASICżĶżĻżŽĄKżżżŌż╬ż╬ĪóźūźĒź░źķź▐źųźļźŪźąźżź╣ż╬├µżŪżŽ║ŪżŌ╬╔żż░╠Åøż╦żżżļĪŻ

ĘQ¹|ż╬╠Ą└■öĄ╝░ż╦×┤żĘżŲżŽźĮźšź╚ź”ź©źóżŪ└┌żĻü÷ż©żķżņżļĪóźĮźšź╚ź”ź©źó╠Ą└■żŪżóżļĪŻźĮźšź╚ź”ź©źóżŽ“£═Ķż╬DSPż╬źūźĒź░źķźÓż╚Ų▒══ĪóCĖ└ĖņżóżļżżżŽźóź╗ź¾źųźķĖ└ĖņżŪĮ±ż▒żļĪŻźūźĒź░źķźÓż“źųźĒź├ź»ź└źżźõź░źķźÓż╚±Tżėż─ż▒żļż│ż╚ż¼żŪżŁżļĪŻźŪźĖź┐źļLSIżŪ║ŪŖZżĶż»Ė½ż½ż▒żļCADż╚CAEż“±Tżėż─ż▒ĪóLSIż╬└Łē”ż“äh▓┴żŪżŁżļżĶż”ż╦żĘżŲżżżļżĶż”ż╩żŌż╬ż└ż╚żżż”ĪŻ

picoChip╝꿎źšźĪźųźņź╣╚ŠŲ│öüż¼╝ńż╩źėźĖź═ź╣żŪżŽżóżļż¼ĪóźĮźšź╚ź”ź©źóż¬żĶżėźŽĪ╝ź╔ź”ź©źó│½╚»ź─Ī╝źļżŌ─¾ČĪżĘżŲżżżļĪŻW-CDMAżõHSDPAĪóLTEĪóCDMA2000/EVDOĪóWiMAXż╩ż╔ż╬ĘQ¹|ż╬─╠┐«öĄ╝░ż╦×┤żĘżŲżŽźĮźšź╚ź”ź©źóżŪ×┤ĮĶż╣żļż┐żßĪóźĮźšź╚ź”ź©źóźĻźšźĪźņź¾ź╣źŪźČźżź¾ż“╗╚żżĪóź┴ź├źūż╬æųż╬źżź¾ź┐źšź¦Ī╝ź╣żõźŽĪ╝ź╔ź”ź©źóż╬╩čśŗż╦×┤żĘżŲżŽźŽĪ╝ź╔ź”ź©źóźūźķź├ź╚źšź®Ī╝źÓż“╗╚ż”ĪŻżĮżņżŠżņ10¹|╬Óż“«Ćż©żļź─Ī╝źļż¼żóżļĪŻĘQź─Ī╝źļżŽ║ŪŠ«ż╬ĄĪē”ż“║▄ż╗żŲżóżĻĪóż│żņż└ż▒żŪżŌźĘź╣źŲźÓżŽ┴╚żßżļĪŻż╣ż╩ż’ż┴źĮźĻźÕĪ╝źĘźńź¾ż╚ż╩ż├żŲżżżļĪŻ