2”╠mĖ³ż╬GaAsź©źįż“CMOSICż╦ĮĖ└čżĘż┐LEDźūźĻź¾ź╚źžź├ź╔ż“▓Łż¼ĘŅŠÅ20╦³Ė─╬╠ŠÅ

CMOSź╔źķźżźąICż╬æųż╦AlGaAs LEDż“┼ļ║▄żĘż┐LEDźūźĻź¾ź╚źžź├ź╔ż“Īó▓ŁźŪźĖź┐źļźżźßĪ╝źĖź¾ź░Ī╩Oki Digital Imaging Corp www.odij.co.jp/indexe.htmlĪ╦ż¼ĘŅŠÅ10Ī┴20╦³Ė─╬╠ŠÅżĘżŲżżżļż│ż╚ż“ĪóINC4 Ī╩Fourth International Nanotechnology Conference on Communication and CorporationĪ╦ż╦ż¬żżżŲ£½żķż½ż╦żĘż┐ĪŻ

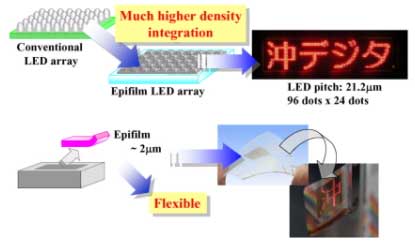

ż│ż╬Č\Į迎ĪóLEDż“ź╔źķźżźųż╣żļż┐żßż╬źĘźĻź│ź¾CMOSź╔źķźżźąź”ź¦Ī╝źŽż╬æųż╦ź©źįź┐źŁźĘźŃźļ└«─╣żĘż┐Ė³żĄ2”╠mż╬GaAs LEDż“ĮĖ└čż╣żļżŌż╬ĪŻż│ż╬Č\Įčż“╗╚ż©żąĪóĘQLEDż╚ź╔źķźżźąż“ź▄ź¾źŪźŻź¾ź░ź’źżźõĪ╝żŪż─ż╩ż░ØŁ═ūż¼ż╩żżż┐żßĪó╝┬äóĀC└čż¼Š«żĄż»ż╩żļż└ż▒żŪżŽż╩ż»Īó1ĮŚż╬GaAsź”ź¦Ī╝źŽż½żķŲDżņżļLEDź┴ź├źūż╬┐¶ż“5Ū▄░╩æųż╚żņżļż┐żßÖ┌ŠÅ└Łż¼æųż¼ż├ż┐ĪŻ

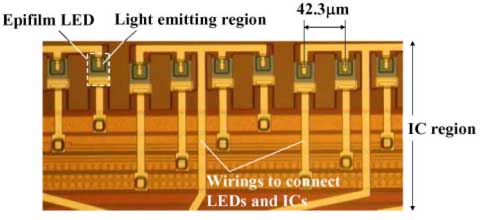

ż│żņż▐żŪż╬LEDźūźĻź¾ź┐źžź├ź╔żŽĪóCMOSź╔źķźżźąż╚GaAsż╬LEDż“▐kż─ż╬┤łæųż╦║▄ż╗ĪóżĮżņżŠżņż“ź▄ź¾źŪźŻź¾ź░ź’źżźõĪ╝żŪ1╦▄ż║ż─ż─ż╩żżżŪżżż┐ĪŻź▄ź¾źŪźŻź¾ź░ź’źżźõĪ╝ż╬┐¶żŽ╦─Įjż╦ż╩żĻĪó╗╚├ōż╣żļGaAsLEDź┴ź├źūżŽź▄ź¾źŪźŻź¾ź░źčź├ź╔ż“└▀ż▒ż╩ż▒żņżąż╩żķż╩żżż┐żßĪóĮjżŁż»ż╩żķżČżļż“įuż╩ż½ż├ż┐ĪŻLED╚»Ė„ŗż╬źĄźżź║ż¼╬Ńż©żą20”╠mżŪżóżļż╬ż╦×┤żĘżŲĪóLEDźóźņźżź┴ź├źūż╬╔²ż¼350Ī┴400”╠mż╦żŌż╩ż├żŲżżż┐ĪŻ

▓ŁźŪźĖź┐źļż¼ź©źįźšźŻźļźÓź▄ź¾źŪźŻź¾ź░Ī╩EFBĪ╦ż╚Ō}żųż│ż╬Č\Į迎ĪóGaAs┤łæųż╦Ę┴└«ż╣żļĖ³żĄ2”╠mż╬LEDź©źįź┐źŁźĘźŃźļ┴žż“ź┴ź├źūż╚żĘżŲŁéż¼żĘĪóźĘźĻź│ź¾ż╬CMOSź┴ź├źūż╬æųż╦─źżĻ╣ńż’ż╗żļż│ż╚żŪźĘźĻź│ź¾æųż╬LEDż“Ę┴└«ż╣żļĪŻż│ż╬Č\Į迎ĪóLEDż╦ź▄ź¾źŪźŻź¾ź░źčź├ź╔ż“└▀ż▒żļØŁ═ūż¼ż╩żżż┐żßźóźņźżż╬╔²ż“70”╠mµć┼┘żŪż╣żÓĪŻż│ż╬±T▓╠ĪóGaAsź”ź¦Ī╝źŽ1ĮŚ┼÷ż┐żĻż╦╗╚ż©żļLEDź┴ź├źūż╬┐¶ż¼5Ū▄░╩æųĪó╝┬║▌ż╦żŽ10Ū▄µć┼┘╗\ż©ż┐ż╚żżż”ĪŻLEDż╚CMOSź┴ź├źūż╚żŽĪóCMOSźūźĒź╗ź╣ż╬─╠Š’ż╬AlŪ█└■Ę┴└«ż╦żĶżĻ└▄¶öż╣żļĪŻ

LEDź©źįź┐źŁźĘźŃźļ┴žż“GaAs┤łż½żķżŽż¼ż╣Šņ╣ńż╦żŽĪóź©źį┴žż╚┤łż╚ż╬┤ųż╦żóżļĄŠ└Ę┴žż“ź©ź├ź┴ź¾ź░żŪĮ³ĄŅż╣żļż│ż╚żŪĪóLEDź©źį┴žż“ŲDżļĪŻżĮż╬ĖÕĪóźĘźĻź│ź¾ż╬CMOSź╔źķźżźąICż╦└▄ŠÆż╣żļŚlż└ż¼ĪóSiź”ź¦Ī╝źŽż╬─źżĻ╣ńż’ż╗Č\Įčż╚Ų▒══ĪóźšźĪź¾źŪźóź’Ī╝źļź╣╩¼╗ę┤ų╬üżŪ└▄ŠÆż╣żļż╚żĘżŲżżżļĪŻźĘźĻź│ź¾ż╚LEDź©źį┴žż╚ż╬┤ųż╦źąź├źšźĪ┴žĪ╩ź╣źÓĪ╝źĖź¾ź░┴žĪ╦ż“Ų│Ų■żĘżŲżżżļż╬żŽĖ└ż”ż▐żŪżŌż╩żżĪŻ╝┬║▌ż╬Ö┌ŠÅ╣®µćżŪżŽĪóÖ┌ŠÅ└Łż“æųż▓żļż┐żß¾H┐¶ż╬LEDź©źį┴žż“▐k┼┘ż╦ź▄ź¾źŪźŻź¾ź░żĘżŲżżżļż¼ĪóżĮż╬Š▄║┘żŽ£½żķż½ż╦żĘż╩żżĪŻ

LEDźūźĻź¾ź┐źžź├ź╔żžż╬▒■├ōżŪżŽĪóLEDż“ż│żņż▐żŪżĶżĻżŌ╠®ż╦╩┬ż┘żļż│ż╚ż¼żŪżŁżļż┐żßĪó╩¼▓“ē”ż╬╣Ōżż░§ÖCż¼▓─ē”ż╦ż╩żļĪŻ600dpiż╬A4źĄźżź║ż╬LEDźūźĻź¾ź╚źžź├ź╔żŪżŽĪó192Ė─ż╬LEDż“╩┬ż┘ż┐LEDźóźņźżź┴ź├źūż“26Ė─╩┬ż┘żŲżżżļĪŻż│ż╬ż┐żßĪó192ź╔ź├ź╚Ī▀26ź┴ź├źūĪß4992ź╔ź├ź╚Īóż╣ż╩ż’ż┴╠¾5000ź╔ź├ź╚ż╬LEDż¼1š`ż╦╩┬ż¾żŪżżżļĪŻ┐ĘĘ┐LEDźóźņźżżŪżŽ192Ė─ż╬LEDż¼Ū█š`żŪżŁżļ─╣żĄĪ╩╠¾8mmĪ╦ż╬ź╔źķźżźąICź┴ź├źūż╬æųż╦ź©źįźšźŻźļźÓLEDźóźņźżż“ź▄ź¾źŪźŻź¾ź░żĘżŲżżżļĪŻ

LEDźūźĻź¾ź╚źžź├ź╔ż╬╬╠ŠÅżŪżŽĪó╠¾5000ź╔ź├ź╚ż“╣Į└«ż╣żļµ£żŲż╬LEDż¼╬╔╣źż╩ØŖ└Łż╚╣Ōżż┐«═Ļ└Łż“Ęeż┐ż╩ż▒żņżąĪó×æēäż╚żĘżŲ╔į╣ń│╩ż╚ż╩żļż┐żßĪóĘŅŠÅżŪ10╦³Ī┴20╦³Ė─ż╬źūźĻź¾ź╚źžź├ź╔ż“╬╠ŠÅżĘżŲżżżļż╚żżż”ż│ż╚żŽĪóż│ż╬Č\Įčż¼╣Ōżżēä䮿╚┐«═Ļ└Łż“Ęeż─LEDźóźņźżż“║Ņ×æżŪżŁżļ╝┬├ōČ\Įčż╚żĘżŲ│╬╬®żĘżŲżżżļż│ż╚ż╦ż╩żļĪŻ▌x╚╬ż╬LEDźūźĻź¾ź┐ż╦ż│ż╬LEDźūźĻź¾ź╚źžź├ź╔ż¼┼ļ║▄żĄżņżŲżżżļĪŻ

║Żövż╬Č\Į迎ĪóĪųź©źįźšźŻźļźÓź▄ź¾źŪźŻź¾ź░Č\Įčż╬│½╚»Įķ┤³ż╬├╩│¼żŪĪóź╩ź╬źŲź»Ü¦▐qż╬Ą“┼└żŪżóżļ╣ŁćŖĮj│žĪ╩Hiroshima University www.hiroshima-u.ac.jp/index.htmlĪ╦ż╬ź╩ź╬źŪźąźżź╣Ī”źĘź╣źŲźÓĖ”ē|ź╗ź¾ź┐Ī╝ż╚ż╬Č”Ų▒Ė”ē|ż╦żĶżĻ│½╚»ż“┐õ┐╩żĘżŲżżż┐Īūż╚Ų▒╝ę│½╚»ŗŗ─╣ż╬▓«ĖČĖ„“}Ģ■żŽĖ└ż”ĪŻ╩Ėŗ▓╩│žŠ╩(Ministry of Education, Culture, Sports, Science & Technology)Ī╩www.mext.go.jp/english/index.htmĪ╦żŽź╩ź╬źŲź»Ü¦▐qźūźĒźĖź¦ź»ź╚żŪĪó╩Ėŗ▓╩│žŠ╩ż¼Ą“┼└ż╚ż╩żļĮj│žż╦½@ČŌż“─¾ČĪżĘĪóĄ“┼└ż╚ż╩żļĮj│žż╬╗▄└▀ż“ŠW├ōżĘż┐Ė”ē|│½╚»ż“ܦ▐qż╣żļĪóż╚żżż”źĘź╣źŲźÓż“ŠW├ōżĘż┐ĪŻ

2”╠mż╚Ū÷żżź©źį┴žż“źĘźĻź│ź¾ź┴ź├źūż╦ĮĖ└čż╣żļż╚żżż”ż│ż╬Č\Į迎ĪóÕX┼┴Ų│╬©ż╬╣Ōżż┤łżóżļżżżŽźšźņźŁźĘźųźļ┤łżž┼ļ║▄ż╣żļż╚żżż├ż┐Īó┐ʿʿż▒■├ōżŌżóżĻż”żļĪŻż▐ż┐ĪóźūźĻź¾ź╚źžź├ź╔żŽ1╝ĪĖĄźóźņźżż└ż¼Īó2╝ĪĖĄźóźņźżż╦LEDż“ĮĖ└čżĘżŲ▓“ćĄ┼┘ż╬╣ŌżżźŪźŻź╣źūźņźżżžż╬▒■├ōżŌ▓─ē”ż└ĪŻ║ŻĖÕż╬▒■├ōżŽ╣ŁżżĪŻ