3╝ĪĖĄSiPĮĖ└č▓ĮČ\Įčż¼źĘź╣źŲźÓ╠õ¼öŲDżĻ┴╚ż▀ż╦Ė■ż½żż╗Žżßż┐

źĘźĻź│ź¾ź┴ź├źūż“3╝ĪĖĄż╦─_ż═╣ńż’ż╗żŲĪó▐kż─ż╬ICźčź├ź▒Ī╝źĖż╦ĮĖ└čż╣żļČ\ĮčĪó3╝ĪĖĄSiPČ\Įčż¼┐ʿʿżźšź¦Ī╝ź║ż╦Ų■ż├ż┐ĪŻTSVĪ╩through silicon viaĪ╦ż╚Ō}żążņżļÅ──╠┼┼Č╦ĪóżĮżņż╦╚╝ż”ź©ź├ź┴ź¾ź░Īó┼┼Č╦ĘĻļmżßż╚żżż├ż┐ż│żņż▐żŪż╬×æļ]źūźĒź╗ź╣ż╦IJ┼└ż¼┼÷ż┐ż├żŲżżż┐3DĮĖ└čČ\Įčż╬▒■├ōż¼Ė½ż©╗ŽżßĪó└▀╝Ŗżõ┐«═Ļ└Łäh▓┴ĪóźŲź╣ź╚żžż╚źĘź╣źŲźÓ┼¬ż╩╣Łż¼żĻż“Ė½ż╗żŲżŁż┐ĪŻASETĪ╩«Ć└Ķ├╝┼┼╗ęČ\Įč│½╚»ĄĪ╣ĮĪ╦ż¼╝ń╠¢żĘż┐International 3D System Integration Conference (3D SIC) 2008ż╦ż¬żżżŲż│ż”żżż├ż┐’łĖ■ż¼Ė½ż©żŲżŁż┐ĪŻ

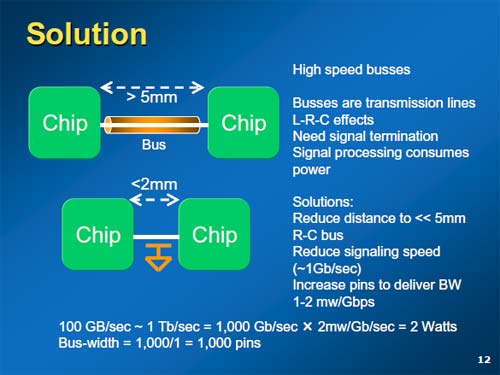

ĮķŲ³║ŪĮķż╬┤─┤╣ų▒ķżŪĪóä▌Intel╝ęMicroprocessor TechnologyĖ”ē|ĮĻż╬Shekhar BorkarĢ■żŽĪó3╝ĪĖĄż╦ĮĖ└čż╣żļż│ż╚ż╬║ŪĮjż╬źßźĻź├ź╚ż¼CPUżõI/Oż╬╣ŌÅ]ż╬źŪĪ╝ź┐źņĪ╝ź╚ż╦×┤żĘżŲĪóźßźŌźĻĪ╝ż╬ęÆżżźŪĪ╝ź┐źņĪ╝ź╚Īóż╣ż╩ż’ż┴źąź¾ź╔╔²ż╚ż╬ź«źŃź├źūż“ļmżßżļż┐żßż╬źŁĪ╝źŲź»ź╬źĒźĖż└ż╚Įęż┘ż┐ĪŻżĘż½żŌI/Oźįź¾żŪżŽGbps┼÷ż┐żĻż╬Š├õJ┼┼╬üżŽż▐ż└ĮjżŁżżż┐żßĪóż│żņżŌ▓╝ż▓żļØŁ═ūż¼żóżļĪŻż│ż╬ż┐żßż╬3D╝┬äóż¼»éżßŠ}ż╦ż╩żļż╚żżż”ĪŻ╬Ńż©żąĪóź┴ź├źū┤ųż╬┐«ęÄżŽ5mm░╩æų▀`żņżļż╚źżź¾ź└ź»ź┐ź¾ź╣└«╩¼ż¼Ė·żżżŲżŁżŲ╩¼╔█─Ļ┐¶┼¬ż╩┐Čżļ╔±żżż“ż╣żļż┐żßźżź¾źįĪ╝ź└ź¾ź╣ź▐ź├ź┴ź¾ź░ż╬ØŁ═ūżõźĘź░ź╩źļźżź¾źŲź░źĻźŲźŻż¼╠õ¼öż╚ż╩ż├żŲż»żļĪŻżĘż½żĘĪóź┴ź├źū┤ųš{▀`ż¼2mm░╩▓╝ż└ż╚źżź¾ź└ź»ź┐ź¾ź╣└«╩¼ż“╠Ą£åżŪżŁĮĖ├µ─Ļ┐¶övŽ®żŪŲDżĻ░Ęż©żļż┐żßĪó╣ŌÅ]▓Įż╦Ė■ż»ż╚żĘżŲżżżļĪŻ

żĄżķż╦ź▐źļź┴ź│źóżõź▐źļź┴źūźĒź╗ź├źĄźĘź╣źŲźÓżŪżŽź│źóż╚L1ż¬żĶżėL2źŁźŃź├źĘźÕż╚ż╬źąź¾ź╔╔²ż“╣Łż»żŪżŁżļż┐żßĪóL2źŁźŃź├źĘźÕż╚źąźļź»źßźŌźĻĪ╝ż╚ż╬┤ųż╦3DźßźŌźĻĪ╝ż“┼ļ║▄ż╣żņżąĪó╣ŌÅ]▓Įż└ż▒żŪżŽż╩ż»─ŃŠ├õJ┼┼╬ü▓ĮżŌ▓─ē”ż╦ż╩żĻĪó100Gźąźżź╚┼÷ż┐żĻ25Wż└ż├ż┐ż╬ż¼2Wµć┼┘ż╦╝²ż▐żļż╚Ė½└čżŌż├żŲżżżļĪŻIntelżŽ░╩Øi80ź│źóż╬╩┬š`źūźĒź╗ź├źĄż“╚»╔ĮżĘżŲżżż┐ż¼ĪóżĮż╬ź│źóż┤ż╚ż╦256Kźąźżź╚ż╬źĒĪ╝ź½źļźßźŌźĻĪ╝ż“Ęeż┐ż╗żļż╚żżż”źóĪ╝źŁźŲź»ź┴źŃż“3Dź╣ź┐ź├ź»╣Įļ]żŪ╝┬ĖĮżŪżŁżļĪŻż│ż│ż╦«Ć╩┬š`ź▐źļź┴ź│źóźūźĒź╗ź├źĄż╬źĘź╣źŲźÓż¼Ö┌żŁżŲż»żļż╚żĘżŲżżżļĪŻ

¶öżżżŲź┘źļź«Ī╝IMECż╬Eric BeyneĢ■żŽĪó3DĮĖ└č▓ĮżŪżŽź│ź╣ź╚ź└ź”ź¾ż¼╝┬├ō▓Įż╬ź½ź«ż“É█żļż┐żßĪó3D╝┬äóż╬WLPĪ╩ź”ź¦Ī╝źŽźņź┘źļźčź├ź▒Ī╝źĖĪ╦żõź’źżźõź▄ź¾ź╔ż╦żĶżļ“£═Ķż╬ź╣ź┐ź├ź»╝┬äóĪóTSVż╦żĶżļ╝┬äóż╩ż╔ż╬╚µ│ėż“╣įż├ż┐ĪŻżĮż╬±T▓╠ĪóżõżŽżĻTSVż¼ź│ź╣ź╚┼¬ż╦Ė½╣ńż”ż│ż╚ĪóżŪżŁżļż└ż▒Å──╠╣”ż“Š«żĄż»ż╣żļż│ż╚ż╩ż╔ż“Įęż┘ż┐ĪŻTSVż╬║ŪĮjż╬╠õ¼öżŽĪóŪ█└■ż╬źļĪ╝źŲźŻź¾ź░żŪżóżļż╚╗ž╝~żĘż┐ĪŻźļĪ╝źŲźŻź¾ź░żŽż│żņż▐żŪ░╩æųż╦╩Ż╗©ż╦ż╩żĻĪóżžż┐ż“ż╣żļż╚źßź┐źļ┴žż“╝{▓├żĘż┐żĻĪóź┴ź├źūż“ĮjżŁż»żĘż╩ż»żŲżŽż╩żķż╩ż»ż╩żļČ▓żņżĄż©żóżļż╚żĘżŲżżżļĪŻTSVż└ż▒ż╩żķĪó╚Š┼─żŪżŽż╩ż»Cuż“╗╚ż├ż┐20”╠mµć┼┘ż╬Ū÷żżź”ź¦Ī╝źŽż╬Å──╠źėźóż¼╣Ō╠®┼┘▓ĮżŪżŁżļż╚żżż”ĪŻ

źßźŌźĻĪ╝źßĪ╝ź½Ī╝ż╬ź╔źżź─Qimonda╝ęBackend Innovationŗ╠ńż╬╝ń└╩ź©ź¾źĖź╦źóżŪżóżļHarry HelderĢ■żŽĪóźßźŌźĻĪ╝3DĮĖ└č▓Įż╬źßźĻź├ź╚żŽźßźŌźĻĪ╝ż╬źąź¾ź╔╔²ż“żĄżķż╦╣Łż▓żļż│ż╚ż└ż╚Įęż┘ż┐ĪŻżõżŽżĻIntelż╚Ų▒══ż╩╣═ż©żŪźßźŌźĻĪ╝ż╬3D▓Įż“┐╩żßżŲżżżļĪŻŲ▒Ģ■żŽĪóQimondaČ\Įčż╬Š▄║┘żŽÅBż╗ż╩żżż╚żĘż╩ż¼żķżŌCuź▐źżź»źĒźąź¾źūż¼¾Hźįź¾▓Įż╬»éżßŠ}ż╦ż╩żļż╚żĘżŲżżżļĪŻż│żņżŽCu┼┼Č╦ż╬æųż╦SnżóżļżżżŽSn-Ag╣ńČŌż“ź│Ī╝źŲźŻź¾ź░żĘżŲżżżļż¼Īó╔w┴Ļ╚┐▒■żŪ┼┼Č╦Ų▒╗╬ż¼±T╣ńż╣żļSOLIDĪ╩solid liquid interdiffusionĪ╦Č\Įčż╚Ō}ż¾żŪżżżļĪŻ

ä▌UCLAż╬Jason CongĢ■żŽĪó╩³ÕX└▀╝ŖæųżŪTSVżŽÕXż“Ų©ż¼ż╣─_═ūż╩╠“│õż“▓╠ż┐ż╣ż│ż╚ż“źĘź▀źÕźņĪ╝źĘźńź¾żŪĖĪŠ┌żĘĪóźšźĒźóźūźķź¾ź╦ź¾ź░żõ¾H┴žź╣ź┐ź├ź»æųż╬ź▌Ī╝ź╚ż╬źčĪ╝źŲźŻźĘźńź╦ź¾ź░ĪóŪ█└■ż╬└▐żĻ╩ųżĘźŪźČźżź¾ż╩ż╔ż¼ÕX°BŃ^ż“╣═╬ĖżĘż┐ÕX└▀╝Ŗż╬╗ž┐╦ż╦ż╩żļż│ż╚ż“┐āżĘż┐ĪŻ

╣ŌÅ]▓Įż╦×┤żĘżŲżŽĪóźĘźĻź│ź¾ż╬źżź¾ź┐Ī╝ź▌Ī╝źČĪ╩ź┴ź├źūż“║▄ż╗żļ┤łĪ╦ż╬öĄĖ■żžĖ■ż½ż”ż│ż╚ż“▓Ł┼┼Ąż╣®Č╚żõŠÅČ╚Č\Įč┴Ē╣ńĖ”ē|ĮĻż╩ż╔ż¼╗ž╝~żĘżŲżżżļĪŻ

ASETżŽ╩┐└«19ŃQ┼┘ż╦Īų╝Ī└ż┬ÕįÆ╝ĪĖĄ└č┴žČ\Įč│½╚»ż╬└ĶŲ│Ė”ē|Īūż╚Š╬żĘżŲ3╝ĪĖĄSiPĮĖ└č▓ĮČ\Įčż╬─┤Øhż“╣įż├żŲżŁż┐ż¼ĪóżĮż╬─┤Øh±T▓╠ż“3D-SICĮ¬╬╗ĖÕż╦╚»╔ĮżĘż┐ĪŻżĮż╬└«▓╠╩¾╣ż“£pż▒Īó2008ŃQ┼┘ż½żķ3╝ĪĖĄĮĖ└č▓ĮČ\ĮčźūźĒźĖź¦ź»ź╚ż╬─╠Š╬Īųź╔źĻĪ╝źÓź┴ź├źū╝Ŗ▓ĶĪūż“NEDOż╦┐ĮæążĘĪóĖĮ║▀ĖĪŲż├µżŪ╦▄│╩┼¬ż╩3D SiPĮĖ└č▓ĮČ\ĮčźūźĒźĖź¦ź»ź╚ż¼ż▐żŌż╩ż»╗Žż▐żļż╚Ė½żŲżżżļĪŻ