░Õ┬ä├ōż╦╣╩żĻ─Ń┼┼╬ü8ź┴źŃź¾ź═źļA-Dź│ź¾źąĪ╝ź┐ICżŪ▒M╔ķż╣żļź╬źļź”ź¦Ī╝ż╬ASD

ź╬źļź”ź¦Ī╝żŪ2007ŃQ5ĘŅż╦Ö┌ż▐żņż┐żąż½żĻż╬ź┘ź¾ź┴źŃĪ╝Arctic Silicon Devices╝ęż¼Īóż│żņż½żķż╬źóź╩źĒź░źĘź░ź╩źļź┴ź¦Ī╝ź¾ż“1ź┴ź├źūż╦ĮĖ└čż╣żļ└’ŠSż“┐╩żßżŲżżżļĪŻżŌż┴żĒż¾Īó─ŃŠ├õJ┼┼╬üż¼Įj(lu©░)Øi─¾ż└ĪŻ─ŃŠ├õJ┼┼╬üż╬źóź╩źĒź░ż╚ź▀ź»ź╣ź╚źĘź░ź╩źļż“įu┴Tż╚ż╣żļż│ż╬ź┘ź¾ź┴źŃĪ╝żŽ2008ŃQ8ĘŅż╦ź┘ź¾ź┴źŃĪ╝źŁźŃźįź┐źļĪ╩VCĪ╦ż½żķ420╦³ź╔źļż╬ŗī2övų`½@ČŌż“įuż┐ĪŻĪųźĻĪ╝ź▐ź¾źųźķźČĪ╝ź╣ż¼Ū╦ż┐ż¾ż╣żļ2ĮĄ┤ųØiż╦─┤├ŻżŪżŁż┐ż╬żŪźķź├źŁĪ╝ż└ż├ż┐Īūż╚Ų▒╝ęCEOż╬John RaaumĢ■żŽČ╗ż“ż╩żŪż¬żĒż╣ĪŻ

Ų▒╝꿎Īó░Õ┬äĄĪ▀_ĪóØŖż╦▓Ķ楿“Ņ~╗╚ż╣żļCTź╣źŁźŃź╩Ī╝żõMRIĪó«Ć▓╗āSÜżéāäóÅøż╩ż╔╬®öü▓Ķ楿“ķWżŁĮąż╣░Õ┬äĄĪ▀_ż╦Ė■ż▒ż┐ź▀ź»ź╣ź╚źĘź░ź╩źļź┴ź├źūż“│½╚»żĘżŲżżżļĪŻż│ż╬├ō²ŗżŪżŽ¾Hź┴źŃź¾ź═źļż╬źĘź░ź╩źļź┴ź¦Ī╝ź¾ż¼ØŁ═ūż╦ż╩żļĪŻ▒■├ō╬Ńż╚żĘżŲ«Ć▓╗āSÜżéāäóÅøż╬Šņ╣ńĪó3ż─ż╬▒■├ōż“╣═ż©żŲżżżļĪŻ▐kż─ż╬Įj(lu©░)żŁż╩Ļā▒Īż╦1±ś└▀Åøż╣żļżĶż”ż╩┐°ż©ÅøżŁĘ┐Īóź╬Ī╝ź╚źčźĮź│ź¾╩┬ż▀ż╬Įj(lu©░)żŁżĄż╬ŌgŠå├ō²ŗĪ╩ŅŹŠå┘Zż╦┼ļ║▄Ī╦Īó░ÕŪvĖ─┐═ż¼Ęeż─Ę╚┬ėĘ┐ż╬3ż─żŪżóżļĪŻ╬®öü▓Ķ楿“Ę┴└«ż╣żļż┐żßż╬övŽ®żŽżĮżņżŠżņż╬├ō²ŗż╦żĶż├żŲ░Ńż”ĪŻĘ╚┬ėĘ┐żŽ16ź┴źŃź¾ź═źļĪóź╬Ī╝ź╚źčźĮź│ź¾╩┬ż▀ż╬äóÅøż╦żŽ64Ī┴128ź┴źŃź¾ź═źļĪó┐°ż©ÅøżŁĘ┐ż╦żŽ192Ī┴512ź┴źŃź¾ź═źļż╬źĘź░ź╩źļź┴ź¦Ī╝ź¾ż“Ų│Ų■ż╣żļĪŻ

║ŻövĪóŲ▒╝ęż¼ŗī2É׿╬┐Ę×æēäż╚żĘżŲ╚»╔ĮżĘż┐ż╬ż¼Īó8ź┴źŃź¾ź═źļ╩¼ż╬źĘź░ź╩źļź┴ź¦Ī╝ź¾ĮĖ└čövŽ®ĪŻ«Ć▓╗āSź╗ź¾źĄĪ╝ż½żķż╬Ų■╬ü┐«ęÄ(gu©®)ż“ĮĶ═²ż╣żļż┐żßż╦źóź¾źūĪóźšźŻźļź┐ĪóA-Dź│ź¾źąĪ╝ź┐ż“▐kż─ż╬┴╚ż╚żĘżŲ8ź┴źŃź¾ź═źļ╩¼ż╬övŽ®ż╚Īó8ź┴źŃź¾ź═źļż╬╩┬š`źŪĪ╝ź┐ż“źĘźĻźóźļźŪĪ╝ź┐ż╦╩č┤╣ż╣żļźĘźĻźóźķźżźČż“ĮĖ└čżĘĪóLVDSĮą╬üż“Ęeż─ĪŻÜżéāäóÅøżŽ«Ć▓╗āSź╚źķź¾ź╣ź▀ź├ź┐1±śż½żķ╚»╝ożĄżņż┐«Ć▓╗āS┐«ęÄ(gu©®)ż“8ż─ż╬ź╗ź¾źĄĪ╝żŪ×RżżĪóź╣źŁźŃź¾żĘżŲżżż»ĪŻź┴źŃź¾ź═źļ┐¶ż¼¾Hż▒żņżą¾Hżżż█ż╔äóÅøżŽŠ«Ę┐ż╦ż╩żļĪŻ

2008ŃQż╦║ŪĮķż╬×æēäż“ĮążĘż┐╗■żŽ1ż¬żĶżė2ź┴źŃź¾ź═źļ╩¼ż╬źĘź░ź╩źļź┴ź¦Ī╝ź¾żĘż½ĮĖ└čżĘżŲżżż╩ż½ż├ż┐ĪŻźĄź¾źūźĻź¾ź░╝■āS┐¶80MSPSĪ╩źĄź¾źūźļ/╔├Ī╦żŪ╩¼▓“ē”12źėź├ź╚ż╬A-Dź│ź¾źąĪ╝ź┐ż╬źŪźÕźóźļź┴ź¦Ī╝ź¾żŪżŽĪóS/N╚µż¼72.4dBż╚Įj(lu©░)żŁż»ĪóŠ├õJ┼┼╬üżŽ102mWż╚Š«żĄż½ż├ż┐ż¼Īó║ŻövĪó20Ī┴80MSPSżŪ12źėź├ź╚ż╬A-Dź│ź¾źąĪ╝ź┐ż“8ź┴źŃź¾ź═źļĮĖ└čżĘżŲżżżļż¼ĪóŠ├õJ┼┼╬üż╬║’žōż“żĄżķż╦┐╩żßĪó50MSPSżŪ40mW/ź┴źŃź¾ź═źļż╚─ŃžōżĘż┐ĪŻ

Š├õJ┼┼╬üż“▓╝ż▓żķżņż┐ż╬żŽĪó¾H┐¶ż╬ź╣źżź├ź┴ź╚źŁźŃźčźĘź┐övŽ®ż╬ź╬źżź║ż╚Š├õJ┼┼╬«ż╚ż╬┤žĘĖ╝░ż“ĄßżßĪóżĮżņżŠżņż╬ź╣źżź├ź┴ź╚źŁźŃźčźĘź┐ż╦╬«żņżļ┼┼╬«ż¼ż╔ż╬µć┼┘ź╬źżź║ż╦┤¾═┐ż╣żļż╬ż½ż“╝ŖōQżĘż┐ĪŻź╣źżź├ź┴ź╚źŁźŃźčźĘź┐1Ė─ż└ż╚ź╬źżź║┼┼░Ąż╬śOŠĶżŽ┼┼╬«ż╦╚┐╚µ╬Ńż╣żļż┐żßĪóź╬źżź║żŽ┼┼╬«ż¼Įj(lu©░)żŁżżż█ż╔▓╝ż¼żļĪŻż│ż╬┤žĘĖż“║Ū┼¼▓ĮżĘż┐ĪŻżĄżķż╦ż│ż╬öĄ(sh©┤)µć╝░ż½żķźŪźČźżź¾źšźĒĪ╝ż“ĄßżßĪóövŽ®ź╚ź▌źĒźĖĪ╝ż“└▀╝ŖżĘż┐ĪŻż│ż╬Č\Į迎ØŖß×┐Įæą├µż└ż╚żżż”ĪŻ

Š├õJ┼┼╬üżŽ«Ć▓╗āSż“┼┴┴„ż╣żļźŪźÕĪ╝źŲźŻ╚µż╦Įj(lu©░)żŁż»░═┘Tż╣żļĪŻ«Ć▓╗āS╚»Ö┌żŽźčźļź╣╝■┤³ż╬75%ż“ź¬ź¾Īó25%ż“ź¬źšż╣żļż¼Īó8ź┴źŃź¾ź═źļż╬£p┐«ŖõżŽ25%ż“ź¬ź¾Īó75%ż“ź¬źšż╦ż╣żļĪŻ▓├ż©żŲĪ󟬟¾ż╦ż╩żļ╗■ż╬╬®ż┴æųż¼żĻ╗■┤ųż“0.5”╠sż╚╣ŌÅ]ż╦żĘĪ󟬟¾╗■ż╬źčźļź╣╔²ż“25%żĶżĻ╗\Įj(lu©░)żĘż╩żżżĶż”ż╦╣®╔ūżĘż┐ĪŻ╬®ż┴æųż¼żĻ╗■┤ųż¼ęÆż▒żņżąź¬ź¾╗■ż╬Š├õJ┼┼╬üż¼╗\Įj(lu©░)żĘżŲżĘż▐ż”ĪŻ

A-Dź│ź¾źąĪ╝ź┐övŽ®żŽĪó3źėź├ź╚źčźżźūźķźżź¾ż╬╗■╩¼│õ¾H─_öĄ(sh©┤)╝░ż“║╬├ōĪóź╣źįĪ╝ź╔żŽźšźķź├źĘźÕź│ź¾źąĪ╝ź┐ż╦ŖZż┼ż▒Īó╩¼▓“ē”żŽŠd╝Ī╚µ│ėöĄ(sh©┤)╝░ż╦ŖZż┼ż▒żŲżżżļĪŻ

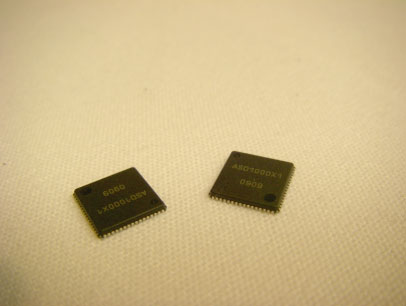

TSMCż╬0.18”╠mż╬CMOSźūźĒź╗ź╣żŪ×æ║Ņż╣żļĪŻ64źįź¾ż╬QFNźčź├ź▒Ī╝źĖż╦╝²═ŲżĘĪ󟥟¾źūźļĮą▓┘ż“╗Žżßż┐ż╚ż│żĒĪŻ╬╠ŠÅżŽ2009ŃQŗī3╗═╚Š┤³ż╦ż╩żļ═Į─ĻĪŻŲ▒╝꿎Ī󿥿▐żČż▐ż╩ź▀ź»ź╣ź╚źĘź░ź╩źļźßĪ╝ź½Ī╝ż½żķŲ■╝ężĘż┐ź┘źŲźķź¾ż╬ź©ź¾źĖź╦źóż¼¾Hż»ĪóČ\Įčż╦żŽ└õĮj(lu©░)ż╩śO┐«ż¼żóżļż╚John RaaumĢ■żŽżżż”ĪŻ