IntelĪó3D-XpointČ\Įčż╦żĶżļźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż“─¾░ŲĪó│¼┴ž╣Į└«ż“Ė½─ŠżĘ

IntelżŽĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬źßźŌźĻż╚ź╣ź╚źņĪ╝źĖż╬│¼┴ž╣Įļ]ż“Ė½─Šż╣ż┘żŁĪó┐ĘĘ┐źßźŌźĻż“źĄź¾źūźļĮą▓┘ż╣żļż╚╚»╔ĮżĘż┐ĪŻ╚ÓżķżŽĪóCPUż╦║ŪżŌŖZżż┴žżŪżŽ“£═Ķż╬DRAMĪó╝Īż╦3D-XpointźßźŌźĻż“├ōżżż┐OptaneźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻ(┐▐1)ĪóżĮż╬╝Īż╦3D-XpointźßźŌźĻż“├ōżżż┐SSDĪóżĮżĘżŲ3D-NANDż╬SSDż╚żżż”╣Į└«ż“─¾░ŲżĘż┐ĪŻźĄź¾źūźļĮą▓┘ż“╗Žżßż┐żąż½żĻż╬źčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻżŽĪó║ŪĮj512Gźąźżź╚ż╬źßźŌźĻźŌźĖźÕĪ╝źļĪŻ

┐▐1ĪĪIntel VPżŪXeon×æēä├┤┼÷źĖź¦ź═źķźļź▐ź═Ī╝źĖźŃĪ╝Ę¾źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ź░źļĪ╝źūż╬ź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷ż╬Lisa SpelmanĢ■ĪĪŠ}ż╦Ęeż├żŲżżżļż╬ż¼OptaneźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻ

źčĪ╝źĘź╣źŲź¾ź╚Ī╩PersistentĪ╦ż╚żŽĪų╣P¶ö┼¬ż╩Īūż╚żżż”┴T╠ŻżŪżóżĻĪóDRAMż╚żŽ░Ńż├żŲ┼┼Ė╗ż“└┌ż├żŲżŌĄŁ▓▒ŲŌ═ŲżŽŠ├ż©ż║ż╦╩▌ĘeżĄżņżļĪŻIntel╝ęż╬VPżŪXeon×æēä├┤┼÷źĖź¦ź═źķźļź▐ź═Ī╝źĖźŃĪ╝Ę¾źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ź░źļĪ╝źūż╬ź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷Lisa SpelmanĢ■Ī╩┐▐1Ī╦ż╦żĶżļż╚Īó25ŃQż╬Öæ╠┐żŽżóżļż╚Ė└ż”ĪŻ3D-XpointźßźŌźĻżŽĪó╔įĦ╚»└ŁźßźŌźĻż╩ż¼żķĪó╣ŌÅ]żŪRAM┼¬ż╩Ų░║Ņż¼żŪżŁżļżĶż”ż└ĪŻ╚ŠŲ│öüź╣ź╚źņĪ╝źĖż╬SSDż└ż╚źŪĪ╝ź┐ż“Ų╔ż▀Įąż╣Šņ╣ńż╬źņźżźŲź¾źĘż¼Č╦żßżŲĮjżŁż»ĪóźĘź╣źŲźÓŲ░║Ņż¼ęÆżņżŲżĘż▐ż”ż¼Īóż│ż│ż╦źčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż“Åøż»ż│ż╚żŪźņźżźŲź¾źĘż“║ŪŠ«ż╦═▐ż©ĪóDRAMż╦ŖZżżÅ]┼┘ż“─¾ČĪż╣żļĪ╩╗▓╣═½@╬┴1Ī╦ĪŻ

ż│ż╬OptaneźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż╬Ė┬─ĻĖ▄Ąężžż╬Įą▓┘żŽ║ŻŃQż╬ĖÕ╚ŠĪó▐k╚╠▌xŠņżŪż╬Ų■Š}żŽ2019ŃQż╦ż╩żļĖ½╣■ż▀żŪżóżļĪŻ╔²╣ŁżżźĮźšź╚ź”ź©źó│½╚»ż“ż╣ż░ż╦╗Žżßżļż┐żßĪóIntelżŽźĮźšź╚ź”ź©źó│½╚»Ūvż╦Ė■ż▒ĪóOptaneźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż“×óż©ż┐źĘź╣źŲźÓż╦źĻźŌĪ╝ź╚żŪźóź»ź╗ź╣żŪżŁżļżĶż”ż╦ż╣żļż╚żżż”ĪŻIntel Builders Construction Zoneż“─╠żĘżŲźĮźšź╚│½╚»ż╚źŲź╣ź╚ż¼▓─ē”ż╦ż╩żļĪŻ

ż│ż╬Optane źčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż╬ØŖ─╣żŽ╣Ō╠®┼┘żŪżóżĻĪóPCIeźąź╣æųżŪź╣ź╚źņĪ╝źĖż½żķźŪĪ╝ź┐ż“źóź»ź╗ź╣ż╣żļŠņ╣ńż╬źņźżźŲź¾źĘ(ęÆūā)ź┌ź╩źļźŲźŻż“£pż▒ż╩ż»żŲ║čżÓżĶż”ż╦ż╩żļĪŻ│½╚»Ūvż¼źĮźšź╚ź”ź©źóż“┼¼└┌ż╦ż╩żļżĶż”ż╦─┤┼Dż╣żļż╚Īóż│ż╬┐ĘĘ┐źßźŌźĻżŽ─Ńź│ź╣ź╚żŪĮj═Ų╬╠ż╬źżź¾źßźŌźĻźŪĪ╝ź┐ź┘Ī╝ź╣źĮźĻźÕĪ╝źĘźńź¾ż¼įużķżņżļżĶż”ż╦└▀╝ŖżĄżņżŲżżżļĪŻDRAMźßźŌźĻźŌźĖźÕĪ╝źļż╬żĶż”ż╦CPU┼÷ż┐żĻ3Tźąźżź╚░╩æųż╬źĘź╣źŲźÓźßźŌźĻż╦│╚─źż╣żļż│ż╚ż╦żĶż├żŲĪóź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż╬ź©ź¾ź╔źµĪ╝źČżŽż│ż╬┐ĘĘ┐źßźŌźĻż“╗╚ż©żą╝ŖōQ╔ķ▓┘ż“║Ū┼¼▓ĮżŪżŁżļżĶż”ż╦ż╩żļĪŻż─ż▐żĻĪóĮjżŁż╩źŪĪ╝ź┐╬╠ż“źūźĒź╗ź├źĄż╦ŖZż┼ż▒żļż│ż╚ż╦żĶż├żŲĪóźĘź╣źŲźÓź╣ź╚źņĪ╝źĖż╦ŖZżżźŪĪ╝ź┐ż“źšź¦ź├ź┴ż╣żļ╗■┤ųęÆżņż“║ŪŠ«ż╦żŪżŁżļż½żķż└ż╚żĘżŲżżżļĪŻ

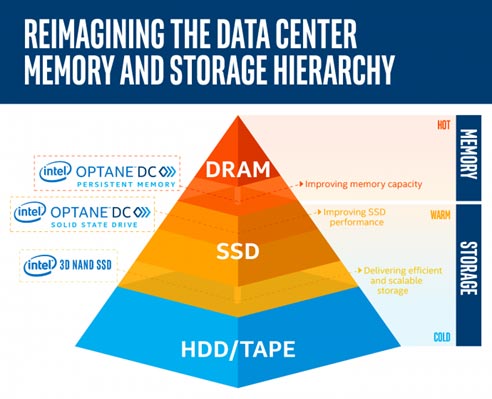

IntelżŽĪóż│ż╬OptaneźßźŌźĻż“ĪóCPUż½żķ║ŪżŌŖZżżDRAMżõHBM-2ż╬ż╣ż░ĖÕż╦Åøż»ż│ż╚żŪĪóæųż╦Įęż┘ż┐żĶż”ż╩źņźżźŲź¾źĘż“║ŪŠ«ż╦żŪżŁĪóźĘź╣źŲźÓż“╣ŌÅ]▓ĮżŪżŁżļż╚ż╣żļĪŻżĄżķż╦ż│żņż▐żŪżŽDRAMż╬ź╣ź╚źņĪ╝źĖż╚żĘżŲSSDż¼░╠ÅøżĘżŲżżż┐ż¼Īóż│ż╬OptaneźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż╚SSDż╚ż╬┤ųż╦Optane SSDż“Åøż»ż╚żżż”╣Į└«ż“─¾░ŲżĘżŲżżżļĪ╩┐▐2Ī╦ĪŻ

┐▐2ĪĪIntelż¼─¾░Ųż╣żļ┐ʿʿżźßźŌźĻż╚ź╣ź╚źņĪ╝źĖż╬╣Į└«ĪĪDRAMż╚SSDż╚ż╬┤ųż“OptaneźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż╚Optane SSDż¼ļmżßĪ󿥿ķż╦SSDż╚HDDżõźŲĪ╝źūż╬ź╣ź╚źņĪ╝źĖż╬┤ųż“3D-NANDż╬SSDż¼ļmżßżļĪĪĮąųZĪ¦Intel

ż│ż╬╣Į└«żŪżŽĪóOptaneźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż¼źßźŌźĻż╬Įj═Ų╬╠▓Įż“▌öżżĪóOptane SSDż¼SSDż╬Å]┼┘ż“▓■║¤ż╣żļĪŻ3D-NAND╣Į└«ż╬SSDżŽ╣Ō╠®┼┘żŪżŽżóżļż¼ĪóÅ]┼┘żŽSSDżĶżĻżŌęÆżżż┐żßĪóHDDż╚ż╬┤ųż╬Å]┼┘║╣ż“ļmżßżļż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩żļĪŻIntelż╬3D-NANDż╬SSDżŽĪó4źėź├ź╚/ź╗źļ╣Į└«żŪĪó96┴žż╬NANDźšźķź├źĘźÕż“├ōżżżļżŌż╬żŪ(╗▓╣═½@╬┴2)ĪóÅ]┼┘ż╚żĘżŲżŽ“£═Ķż╬╩┐ĀCNANDżõ1źėź├ź╚/ź╗źļöĄ╝░żĶżĻżŽęÆż»ż╩żļĪŻż│ż╬ż┐żßĪóSSDż╚HDDż╩ż╔ż╬ź╣ź╚źņĪ╝źĖż╚żĘżŲ░╠Åø¤²ż▒żŲżżżļĪŻ

OptaneżŽźčĪ╝źĘź╣źŲź¾ź╚ĪóSSDż╚żŌŲ▒żĖ3D-XpointźßźŌźĻź╗źļ╣Įļ]ż“├ōżżż╩ż¼żķĪóźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻż╚SSDżŪż╔ż╬żĶż”ż╦żĘżŲÅ]┼┘║╣żõ═Ų╬╠║╣ż“╝┬ĖĮżĘżŲżżżļż╬ż½ĪóIntelżŽ£½żķż½ż╦żĘżŲżżż╩żżĪŻ

╗▓╣═½@╬┴

1. Reimaging the Data Center Memory and Storage Hierarchy (2018/05/30)

2. Intel/Micronż¼NAND┤žĘĖż“║Ųäė▓ĮĪó4źėź├ź╚/ź╗źļż╬64┴žż“×æēäŪ¦─Ļ (2018/05/23)