ČŌō’Ū█└■żŪź½ź╣ź┐źÓ▓Įż╣żļź▐źżź│ź¾ż“Atmel ż¼╚»ŪõĪó╣ŌÅ]─ŃŠ├õJ┼┼╬üż“▓─ē”ż╦

ĪĪä▌Atmel╝ęż¼ź½ź╣ź┐ź▐źżź║żŪżŁĪóFPGAżĶżĻżŌ╣ŌÅ]żŪ─ŃŠ├õJ┼┼╬üĪó─Ń▓┴│╩ż╬32źėź├ź╚ź▐źżź»źĒź│ź¾ź╚źĒĪ╝źķCAP (Customizable Atmel Processor)ż“╚»Ūõż╣żļĪŻFPGAż“╗╚ż├żŲ╝┬╣įż╣żļDSPźóźļź┤źĻź║źÓż“╗╚ż├ż┐╚µ│ė╬ŃżŪżŽ8Ū▄żŌÅ]ż½ż├ż┐ż╚żżż”ĪŻ

ØŖż╦Īóź▐źżź│ź¾ż╚│░¤²ż▒FPGAż“┴╚ż▀╣ńż’ż╗żŲOFDMżõGPS┴Ļ┤ž▀_ż╩ż╔ż“╣Į└«ż╣żļŠņ╣ńĪó│░ŗźĒźĖź├ź»µ£öüż╦×┤żĘżŲź»źĒź├ź»╝■āS┐¶ż“50MHz░╩æųż╦æųż▓żļż│ż╚żŽžMżĘżżż╚żżż’żņżŲżżżļĪŻźĘź¾ź░źļź┴ź├źūż╦Ų▒┼∙ż╩ĄĪē”ż“źŽĪ╝ź╔ź’Ī╝źõĪ╝ź╔żŪ╝┬ĖĮżĘźßź┐źļŪ█└■żŪźūźĒź░źķźÓż╣żņżąĪóSRAMź┘Ī╝ź╣ż╬FPGAżĶżĻżŌ╣ŌÅ]żŪĪó─ŃŠ├õJ┼┼╬üż╦żŪżŁżļĪŻ

żĮż╬źĘźĻĪ╝ź║ż╬▐kż─ĪóAT91CAPź▐źżź│ź¾ż╦żŽĪó“£═Ķż╬ź│źóżõĘQ¹|╝■╩šźżź¾ź┐Ī╝źšź¦Ī╝ź╣Īó╣ŌÅ]źąź╣ż╦▓├ż©Īóźßź┐źļżŪźūźĒź░źķźÓż╣żļźųźĒź├ź»övŽ®Ī╩MPźųźĒź├ź»Ī╦ż¼żóżļĪŻż│ż╬źßź┐źļŪ█└■ż“źūźĒź░źķźÓż╣żļż│ż╚żŪź½ź╣ź┐ź▐źżź║ż╣żļĪŻMPźųźĒź├ź»ż╦żŽ║ŪĮj200╦³FPGA┴Ļ┼÷ź▓Ī╝ź╚ż¼┤▐ż▐żņżŲżżżļĪŻż│ż╬MPźųźĒź├ź»ż“╗╚ż”ż╬żŽĪó1) FPGAżŪżĶż»╗╚ż’żņżŲżŁż┐żĶż”ż╩IPżõDSPźóźļź┤źĻź║źÓĪó2) ▐kż─░╩æųż╬źūźĒź╗ź├źĄź│źóż╬╝{▓├Īó3) ż▐ż└║YØŹēäż╦ż╩ż├żŲżżż╩żż╝■╩šövŽ®Īóż╩ż╔ĪŻ

║ŪĮķż╬×æēäźšźĪź▀źĻżŽĪóARM╝ęż╬ARM7ĪóARM9ż╬źūźĒź╗ź├źĄź│źóż“╗╚ż”AT91CAP7ĪóAT91CAP9ż╦ź½ź╣ź┐ź▐źżź║żĘż┐×æēäż╦ż╩żļĪŻ┘J┘Tż╬ARM7ż¬żĶżėŻ╣ż╚ĪóFPGAż“┴╚ż▀╣ńż’ż╗ż┐övŽ®ż“1ź┴ź├źū▓Įż╣żļŠņ╣ńżŪżŌöĪ╣įż╦ż½ż½żļź│ź╣ź╚żŽ15╦³ź╔źļżŪżóżļĪŻ1ź┴ź├źū▓Įż╣żļż│ż╚żŪ║ŪĄK╗■ż╬ź╣ź┐źŲźŻź├ź»ż╩Š├õJ┼┼╬üżŽ3Ī┴4mWż╚Š«żĄż»ĪóFPGAövŽ®żĶżĻżŌ3ĘÕŠ»ż╩ż»Īóź└źżź╩ź▀ź├ź»ż╩Š├õJ┼┼╬üżŌFPGAż╬1/10µć┼┘ż╚żżż”ĪŻ

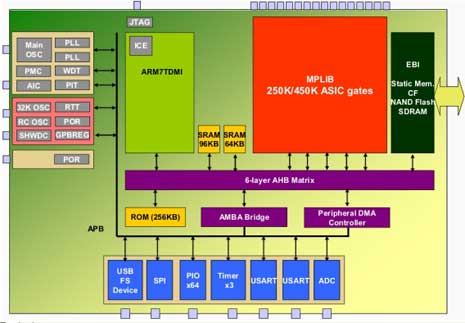

AT91CAP7ź▐źżź│ź¾żŽĪó6┴žż╬źąź╣Ū█└■ź▐ź╚źĻź├ź»ź╣ż╚4┴žż╬źąź╣ź▐ź╣ź┐Ī╝Ū█└■ż“Ęeż┴ĪóĖÕŪvż╬źąź╣ź▐ź╣ź┐Ī╝Ū█└■ż¼MPźųźĒź├ź»└ņ├ōż╬Ū█└■ż╚ż╩żļĪ╩┐▐Ż▒Ī╦ĪŻŪ█└■┴žż¼Ø▓╩¼ŲDż├żŲżżżļż┐żßźąź╣Ēö╣ńż¼ż╩ż»Ī󟬟¾ź┴ź├źūż╬źąź¾ź╔╔²ż“╣Łż»ż╚żņĪó║ŪĮj19.2Gbpsż“╝┬ĖĮżŪżŁżļĪŻ

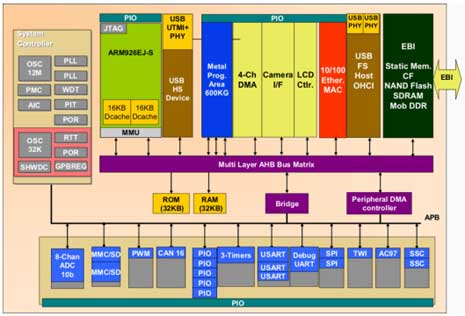

AT91CAP9ź▐źżź│ź¾żŽĪóźąź╣ź▐ź╣ź┐Ī╝Ū█└■ż¼3┴žżŪĪóźąź╣ź▐ź╚źĻź├ź»ź╣Ū█└■żŽ12┴ž╣Į└«żŪżóżļ(┐▐Ż▓)ĪŻMPźųźĒź├ź»ż╬źąź¾ź╔╔²żŽ38.4Gbpsż╚╣ŌÅ]×┤▒■żŪżŁżļĪŻ

MPźųźĒź├ź»żŽĪó╩╠ż╬źūźĒź╗ź├źĄż“┼ļ║▄ż╣żļż│ż╚żŌżŪżŁżļĪŻ╬Ńż©żąĪ󟣟џ├źĘźÕ¤²żŁż╬ARM926EJ-Sż╚ż½Īó8źėź├ź╚ż╬ź▐źļź┴ź│źóż╩ż╔ż¼żóżļĪŻ▒■├ō╬ŃżŪżŽĪó┐¶¾Hż»ż╬ź╗ź¾źĄĪ╝ż“×óż©żļ╣®Č╚├ōż╬ź│ź¾ź╚źĒĪ╝źķż╩ż╔ż╦żŽĪó╩Ż┐¶ż╬ź╗ź¾źĄĪ╝ż╦ĘQ8źėź├ź╚ź▐źżź│ź¾ż“¾H┐¶┼ļ║▄ż╣żļź┴ź├źūż¼ż█żĘżżĪŻ¾H┐¶ż╬ź▐źżź│ź¾ż“1ź┴ź├źūż╦┼ļ║▄ż╣żņżąźĘź╣źŲźÓż╬ź│ź╣ź╚ż“žōżķżĘĪóŠ├õJ┼┼╬üż“▓╝ż▓żļż│ż╚ż¼żŪżŁĪóźĘź╣źŲźÓż“į~┴Ū▓ĮżŪżŁżļĪŻż│ż╬ż╚żŁĪóźąź╣ź▐ź╣ź┐Ī╝öUĖµż╚DMAźóź»ź╗ź╣żŽMPźųźĒź├ź»ŗż╚źĘź╣źŲźÓźąź╣ż╚ż╬┤ųż╦└▀ż▒żļż╚MPźųźĒź├ź»ż╬źūźĒź╗ź├źĄż╚ż╬ż─ż╩ż¼żĻż¼Č╦żßżŲ╬╔ż»ż╩żļĪŻ

│½╚»ź─Ī╝źļż╚żĘżŲżŽĪóAtmel╝ęż╬ARMź┘Ī╝ź╣ź▐źżź│ź¾ż╚Ų▒żĖCź│ź¾źčźżźķżõRTOSĪóOSĪóICEĪóIDEż“╗╚├ōżŪżŁżļĪŻż─ż▐żĻźĄĪ╝ź╔źčĪ╝źŲźŻż╬ź─Ī╝źļż“╗╚ż©żļż│ż╚ż╦ż╩żļĪŻżŌż┴żĒż¾ĪóAtmelż╬─¾ČĪż╣żļGNU gccCź│ź¾źčźżźķżõGNU gdbźŪźąź├ź¼ż╩ż╔ż╬ź─Ī╝źļżŌŠW├ō▓─ē”ż└ĪŻ├▒▓┴żŽĪó5╦³Ė─ĻPŲ■ż╣żļŠņ╣ńAT91CAP7ż¼5.44ä▌ź╔źļĪóAT91CAP9Sż¼10╦³Ė─ĻPŲ■╗■żŪ13ä▌ź╔źļĪŻ