AMDż¼ź╣źčź│ź¾Ī”źĄĪ╝źąĪ╝├ōźŽźżź©ź¾ź╔ż╬CPUź▐źļź┴ź┴ź├źūźŌźĖźÕĪ╝źļż“╚»Ūõ

║ŻżõźšźĪźųźņź╣ż╚żĘżŲ┐╚Ę┌ż╦ż╩ż├ż┐AMDż¼12ź│źó/8ź│źóż╚żżż”Č╦żßżŲźŽźżź©ź¾ź╔ż╩ź▐źļź┴ź│źóCPUż“╚»ŪõżĘż┐ĪŻż│ż╬Opteron 6100źĘźĻĪ╝ź║ż╬źūźĒź╗ź├źĄżŽĪóHPCĪ╩╣Ō└Łē”ź│ź¾źįźÕĪ╝ź┐Ī╦żõź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐ż╩ż╔źŽźżź©ź¾ź╔ż╬ź│ź¾źįźÕĪ╝ź┐ĪóźĄĪ╝źąĪ╝├ōż╦╗╚ż”ĪŻOpteronźĘźĻĪ╝ź║żŽż╣żŪż╦ź»źņźżż╬ź╣Ī╝źčĪ╝ź│ź¾ż╦┼ļ║▄żĄżņżŲżżżļż¼Īóż│ż╬CPUżŽ▓┴│╩┼÷ż┐żĻż╬└Łē”/Š├õJ┼┼╬üż“Įj╔²ż╦æųż▓żļż│ż╚ż¼żŪżŁżļĪŻ

Opteron 6100źĘźĻĪ╝ź║ż╬│░Ę┴(║ĖżŽ╔ĮĀCĪóīÜżŽ╬óĀC)

Opteron 6100żŽĪó45nmż╬SOIźūźĒź╗ź╣ż“╗╚ż├żŲź░źĒĪ╝źąźļźšźĪź”ź¾ź╔źĻĪ╝ź║ż¼×æļ]żĘż┐żŌż╬ż└ĪŻ║ŻövżŽHigh-kź▓Ī╝ź╚║Ó╬┴Īóźßź┐źļź▓Ī╝ź╚żŽż▐ż└╗╚ż├żŲżŽżżż╩żżż¼Īó32nmźūźĒź╗ź╣żŪżŽ╗╚ż”ż│ż╚ż╦ż╩żļż╚ĪóŲ▒╝꟥Ī╝źąĪ╝/ź’Ī╝ź»ź╣źŲĪ╝źĘźńź¾ŗ╠ńźėźĖź═ź╣│½╚»źŪźŻźņź»ź┐ż╬John FrueheĢ■żŽĖ└ż”ĪŻ

ż│ż╬źūźĒź╗ź├źĄżŽ1╩šż¼┐¶cmż╬ź▐źļź┴ź┴ź├źūźŌźĖźÕĪ╝źļĪ╩źĮź▒ź├ź╚G34ż╚Ō}żążņżļ1944├╝╗ęż╬LGAĪ¦land grid arrayĪ╦żŪ╣Į└«żĄżņżŲż¬żĻĪóźĘźĻź│ź¾żŽ346mm2ż╬CPUź┴ź├źūż“2Ė─┼ļ║▄żĘżŲżżżļĪŻż│ż╬2ź┴ź├źū╣Į└«żŪ╣ń╝Ŗż╬CPUź│źó┐¶ż¼12żóżļżżżŽ8ź│źóż╚ż╩ż├żŲżżżļĪŻ

ż│ż╬źūźĒź╗ź├źĄ╝┬ĖĮż╬ź½ź«żŽĪóżŌżŽżõ×æļ]Č\ĮčżŪżŌĪóź│ź¾źįźÕĪ╝ź┐źóĪ╝źŁźŲź»ź┴źŃżŪżŌż╩żżĪŻźŁźŃź├źĘźÕ╣Į└«żõźčźżźūźķźżź¾├╩┐¶ż╩ż╔żŽż│żņż▐żŪż╬║Ū╣ŌČ\Įčż“╗╚ż├żŲżżżļż└ż▒ż╦ż╣ż«ż╩żżĪŻżŌż┴żĒż¾Īó1W┼÷ż┐żĻż╬└Łē”Ī╩└Łē”/WĪ╦żŽż│żņż▐żŪż╬2.2Ū▄░╩æųż╚╣Ōżżż╬żŪżŽżóżļż¼Īóź╗Ī╝źļź╣ź▌źżź¾ź╚żŽŠ├õJ┼┼╬üż¼─Ńż»Īó└Łē”ż¼╣Ōżżż│ż╚żŪżŽż╩żżĪŻżÓżĘżĒĪó─Ńź│ź╣ź╚żŪż│ż╬╣Ō└Łē”Ī”─ŃŠ├õJ┼┼╬üż“╝┬ĖĮżĘż┐ż│ż╚ż└ĪŻ

╬Ńż©żąĪó2źĮź▒ź├ź╚╣Į└«Ī╩ICż“2Ė─╩┬š`╣Į└«Ī╦ż╬Šņ╣ńż╦Īó12ź│źóż╬CPUżŪżŽSPECintżŌSPECfpżŌŲ▒╝ęż╬“£═Ķż╬6ź│źóCPUż╚╚µż┘żŲżŌ2Ū▄ż╬└Łē”ż“Ęeż─ż¼Īó┼D┐¶▒ķōQżŪŲ▒żĖ└Łē”ż╬▌x╚╬ēäż╚╚µż┘żļż╚Īó▓┴│╩żŽ1165ź╔źļż╚3│õżŌŖWżżĪŻż▐ż┐╔ŌŲ░Š«┐¶┼└▒ķōQżŪżŽż│ż╬▌x╚╬ēäżĶżĻ▓┴│╩ż¼3│õŖWżżż└ż▒żŪżŽż╩ż»└Łē”/WżŌ20%╣ŌżżĪŻ

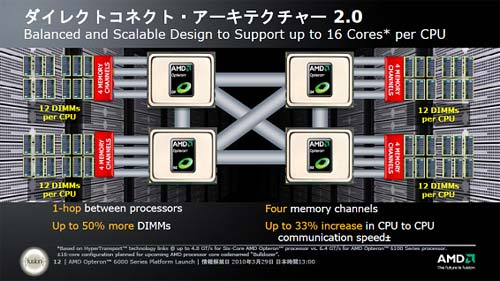

ź└źżźņź»ź╚ź│ź═ź»ź╚2.0ż╬źóĪ╝źŁźŲź»ź┴źŃ

ż│żņż█ż╔ż╬└Łē”/W/ź│ź╣ź╚ż“╝┬ĖĮżĘż┐Č\Į迎Īóź│ź¾źįźÕĪ╝ź┐źóĪ╝źŁźŲź»ź┴źŃżŪżŽż╩ż»ĪóCPUż╚CPUĪóżóżļżżżŽCPUż╚źßźŌźĻĪ╝ż╚ż╬żõżĻŲDżĻż“╣ŌÅ]ż╦ż╣żļż┐żßż╬Č\Įčź└źżźņź»ź╚ź│ź═ź»ź╚2.0ż“Ų│Ų■żĘż┐ż│ż╚ż└ĪŻż│ż╬Č\Į迎ź▄ź╚źļź═ź├ź»ż╚ż╩żĻż¼ż┴ż╩źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“ź╣źÓĪ╝ź║ż╦źŪĪ╝ź┐ż“┼Š┴„żĄż╗żļż│ż╚żŪź│ź¾źįźÕĪ╝ź┐ż╬└Łē”ż“æųż▓żļżŌż╬ĪŻ“£═Ķż╬źąź╣öĄ╝░ż╚żŽ░ŃżżĪóż▐żļżŪ─╠┐«Ė“┤╣ĄĪż╬ź»źĒź╣źąĪ╝ź╣źżź├ź┴ż╬żĶż”ż╦CPUŲ▒╗╬ĪóźßźŌźĻĪ╝ż╚ż╬żõżĻŲDżĻż“ź╣źÓĪ╝ź║ż╦żŪżŁżļżĶż”ż╩źóĪ╝źŁźŲź»ź┴źŃżŪżóżļĪŻż│ż╬╣Į└«ż“ż╚żļż│ż╚żŪCPUż╚źßźŌźĻĪ╝┤ųż╬Å]┼┘żŽ50%Ė■æųżĘĪóCPUŲ▒╗╬ż╬Å]┼┘żŽ33%æųż¼ż├ż┐ĪŻ

źßźŌźĻĪ╝ź┴źŃź¾ź═źļżŽ4╦▄Ęeż┴ĪóżĮżņżŠżņ72źėź├ź╚źąź╣żŪ─Ń┼┼░ĄDDR-3ż“źĄź▌Ī╝ź╚żĘżŲżżżļĪŻż│ż╬±T▓╠CPU┼÷ż┐żĻż╬źßźŌźĻĪ╝źąź¾ź╔╔²żŽ║ŪĮj42.7GB/sż╦ż╩żļĪŻCPUŲ▒╗╬ż╬└▄¶öż╦żŽHyperTransportźąź╣ż“4╦▄├ō┴TżĘż┐ĪŻż│ż╬źąź╣1╦▄ż╦żŽ16╦▄ż╬źĻź¾ź»ż╚Ō}żążņżļź▌Ī╝ź╚ż¼żóżĻĪó1źĻź¾ź»┼÷ż┐żĻż╬źŪĪ╝ź┐źŪĪ╝ź╚żŽ║ŪĮj6.4GT/sĪ╩Giga Transfer per secondĪ╦ż╚żżż”ĪŻGT/sż╚żżż”├▒░╠żŽĪóźąź╣╔²ż╩ż╔ż╦żĶż├żŲźŪĪ╝ź┐źņĪ╝ź╚ż¼╩čż’żļż┐żßĪóźżź¾źŲźļż╩ż╔ż¼ż│ż”╔ĮĖĮżĘżŲżżżļżĶż”ż└ĪŻ

ź└źżźņź»ź╚ź│ź═ź»ź╚2.0źóĪ╝źŁźŲź»ź┴źŃżŽż╔ż”żõż├żŲ╝┬ĖĮżĘż┐ż½ĪŻĘQCPUŲŌż╦ź└źżźņź»ź╚ź│ź═ź»ź╚2.0ż╬ź▌Ī╝ź╚źŪĪ╝ź┐öUĖµövŽ®ż“ŲŌē┼żĘżŲż¬żĻĪóG34źčź├ź▒Ī╝źĖŲŌż╦żŽØŖ╩╠ż╩ź│ź¾ź╚źĒĪ╝źķż“ĮĖ└čżĘżŲżżż╩żżĪŻż│ż╬źóĪ╝źŁźŲź»ź┴źŃżŽ╣ŌÅ]źżź¾ź┐Ī╝źšź¦Ī╝ź╣żŪżóżļHyperTransportż“ź┘Ī╝ź╣ż╦żĘż┐ź╣źżź├ź┴ź¾ź░Č\Įčż└Īóż╚FrueheĢ■żŽĖ└ż”ĪŻ═²ĮyżŽĮø═Ķ└Łż“┤▐żÓ│╚─ź└Łż╦żóżļĪŻHyperTransportż╬ź╬Ī╝ź╔┐¶ż“æųż▓ż┐«Ć╩┬š`Ī╩massive parallelĪ╦ż╬ź╣Ī╝źčĪ╝ź│ź¾ż“─Ń▓┴│╩żŪ║Ņżņżļż½żķż└ĪŻFrueheĢ■żŽĪųĮø═ĶżŽ«Ć╩┬š`ź│ź¾źįźÕĪ╝ź┐ż╚Ų▒══Īóź╬Ī╝ź╔┐¶ż“╣ŌżßżŲżżż»ż¼Īóżóż▐żĻ¾Hż╣ż«żļż╚źņźżźŲź¾źĘż¼┐╝ż»ż╩żļż┐żßĪóź╬Ī╝ź╔┐¶ż╬┐¶ż╚ĮĶ═²Å]┼┘ż╬źąźķź¾ź╣ż¼ź½ź«ż╚ż╩żļĪūż╚żĘżŲżżżļĪŻ