┐ʿʿż▌xŠņ│½¹£ż¼▓─ē”ż╦ż╩ż├ż┐FPGAČ╚─cĪóź┴źŃź¾ź╣ż╚Č╝░ęż¼±é┘T(1)

FPGAźėźĖź═ź╣ż¼╩č╦ŲżĘżŲżŁżŲżżżļĪŻä▌źČźżźĻź¾ź»ź╣ż╚źóźļźŲźķż╚żżż”2äėż¼┴Ķż├żŲżŁż┐“£═Ķż╬▌xŠņżŪżŌŠ├õJ┼┼╬üż“æųż▓ż║ż╦└Łē”Ī”ĄĪē”ż“æųż▓żŲżżż»öĄĖ■ż╦╩čż’żĻĪóź▐Ī╝ź▒źŲźŻź¾ź░┼ž╬ü╝ĪŗīżŪżŽźĒĪ╝ź©ź¾ź╔▌xŠņż╦żŌ┐®żż╣■żßżļż│ż╚ż¼ż’ż½ż├żŲżŁż┐ĪŻż│ż╬2övż╦ż’ż┐żļFPGAźņź▌Ī╝ź╚żŪżŽĪóż▐ż║“£═Ķż╬źŽźżź©ź¾ź╔▌xŠņĪ󿥿ķż╦┐Ęæäż╬źĒĪ╝ź©ź¾ź╔▌xŠņż“Ė½żŲżżż»ĪŻ

╗@┼┘ż“╩čż©żķżņżļŠĶōQ▀_ż“┼ļ║▄żĘż┐Stratix-5ĪĪĮąųZĪ¦źóźļźŲźķ

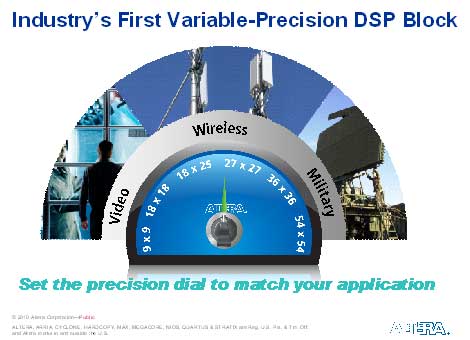

źŽźżź©ź¾ź╔▌xŠņż╦Ė■ż▒ĪóźóźļźŲźķżŽ╗@┼┘ż“9Ī▀9źėź├ź╚żõ18Ī▀18źėź├ź╚Īó18Ī▀25źėź├ź╚ż╩ż╔ż╚╩čż©żķżņżļŠĶōQ▀_ż“¾H┐¶┼ļ║▄żĘż┐┐ʿʿżFPGAĪóStratix-5źšźĪź▀źĻĪ╝ż“╚»╔ĮĪóżĮż╬▒■├ōĪó┴└żżż╦ż─żżżŲĪóä▌Global Press╝ń╠¢ż╬e-Summit2010żŪ╚»╔ĮżĘż┐ĪŻĪų╔w─Ļ╗@┼┘ż╬ŠĶōQ▀_ż└ż╚Īó╣Ō└Łē”ż╩ź’źżźõźņź╣ź╣źŲĪ╝źĘźńź¾żõ¤®├ōźņĪ╝źČĪ╝Īó░Õ├ō▓ĶćĄĮĶ═²Īó┤Ų£åźėźŪź¬ż╩ż╔ż╬▒■├ōżŪżŽź│ź╣ź╚ż╚Š├õJ┼┼╬üż“æųż▓ż║ż╦└Łē”ż“æųż▓żļż│ż╚żŽżŪżŁż╩żżĪūż╚Ų▒╝ęź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷źĘź╦źóVPż╬Danny BiranĢ■żŽéāĖ└ż╣żļĪŻ

FPGAżŽźŽźżź©ź¾ź╔▒■├ōż╚żŽżżż©Īó└Łē”ż“æųż▓żņżąŠ├õJ┼┼╬üżõź│ź╣ź╚ż“æųż▓żŲżŌżĶżżż╚żżż”ŚlżŪżŽż╩żżĪóż╚Ų▒Ģ■żŽżżż”ĪŻ┐ʿʿż▒■├ōż╦×┤żĘżŲĪó╗@┼┘ż╬╣Ōżż╝ŖōQĮĶ═²ż“µ£żŲż╬övŽ®żŪØŁ═ūż╚żĄżņżļŚlżŪżŽż╩żżĪŻStratix-5żŪżŽĪó18Ī▀18źėź├ź╚ż╬ŠĶōQż“┤╦▄ż╚ż╣żļŠĶōQ▀_ż“3,680Ė─żŌĮĖ└čżĘżŲżżżļż¼ĪóFPGAż╬ŠĶōQ▀_źųźĒź├ź»żŽźĮźšź╚ź”ź©źóżŪ9Ī▀9╣Į└«żõ18Ī▀25╣Į└«ż╦╩čż©żļż│ż╚ż¼żŪżŁżļĪŻ

źóźļźŲźķż╬źĘź╦źóVP Danny BiranĢ■

ż│żņż▐żŪźėźŪź¬▒■├ōżŪżŽĪó9Ī▀9źėź├ź╚ż╬ŠĶōQżŪØ▓╩¼ż└ż├ż┐SDæä│╩ż╬źŲźņźėżŽHDż╦ż╩żĻ12Ī▀12źėź├ź╚żžĪó4Kż╬źšźļHDż╚ż╩żļż╚18Ī▀18źėź├ź╚żžż╚┐╩▓ĮżĘżŲżŁż┐ĪŻź’źżźõźņź╣ź┘Ī╝ź╣ź╣źŲĪ╝źĘźńź¾żŪżŌ18Ī▀18źėź├ź╚ŠĶōQż¼ØŁ═ūż└ż├ż┐3GżõLTEż½żķ4Gż╚ż╩żļLTE Advancedż╦ż╩żļż╚27Ī▀27źėź├ź╚ż╬ŠĶōQż¼═ūĄßżĄżņżļĪŻ¤®├ōźņĪ╝ź└Ī╝żŪżŌż½ż─żŲżŽØŌĄĪż“Ė½ż─ż▒żļż└ż▒żŪ18Ī▀18źėź├ź╚ŠĶōQż└ż▒żŪ║čż¾ż└ż¼Īó╩Ż┐¶ż╬ź┐Ī╝ź▓ź├ź╚ż“Ė½ż─ż▒ż┐żĻĪóżĮżņżķż“╝{└ūżĘż┐żĻĪó├Žæųż╬ź▐ź├źįź¾ź░żõźĘĪ╝ź╣źļĪ╝ĄĪē”ż“▓─ē”ż╦żĘż┐żĻż╣żļżĶż”ż╩ĄĪē”ż▐żŪ┼ļ║▄ż╣żļżĶż”ż╦ż╩ż├żŲżżżļĪŻż│ż╬ż┐żß┐¶1000±śż╬ź╚źķź¾źĘĪ╝źąźŌźĖźÕĪ╝źļżõ┐¶100±śż╬źĄźųź┴źŃź¾ź═źļźŌźĖźÕĪ╝źļż“╗╚ż”ĪŻżĘż½żŌ╔ŌŲ░Š«┐¶┼└▒ķōQż╚żżż”╣Ō╗@┼┘ż╩╝ŖōQżŌĄßżßżķżņżļĪŻ

Ų▒╝꿎Stratix-5źĘźĻĪ╝ź║ż“źčź’Ī╝źĻź▀ź├ź╚ż╬More than Moore×æēäż╚░╠Åø¤²ż▒żŲżżżļĪŻ3,680Ė─ż╬ŠĶōQ▀_ż╦▓├ż©Īó100╦³░╩æųż╬éb═²ź©źņźßź¾ź╚ż“┼ļ║▄Īó50Mźėź├ź╚░╩æųż╬RAMż╩ż╔żŌĮĖ└čżĘż┐ĪŻż│ż╬28nmż╬FPGAżŪżŽĪóźĮźšź╚ź”ź©źóźĒźĖź├ź»ż╦▓├ż©ĪóŲ▒╝ęż╬FPGAż“ASICż╦żĮż╬ż▐ż▐═Ņż╚ż╗żļHardCopyźųźĒź├ź»ż“┴╚ż▀╣■ż¾ż└ĪŻź│ź╣ź╚╗\▓├ż“═▐ż©żļż┐żßż╦ICµ£öüż╬źšźļź▐ź╣ź»ź╗ź├ź╚ż“╗╚ż’ż║ĪóØi└ż┬Õż╬40nmźŪźČźżź¾ż½żķźßź┐źļźņźżźõĪ╝ż“Š»żĘT┘ćż╣żļż└ż▒żŪż╣żÓżĶż”ż╩ź▐ź╣ź»ź╗ź├ź╚ż╦╩čż©ż┐ĪŻ2011ŃQż╬ŗī1╗═╚Š┤³ż╦źĄź¾źūźļż“Įą▓┘ż╣żļ═Į─ĻżŪżóżļĪŻ

└▀╝Ŗź─Ī╝źļżŌźėźŪź¬└▀╝Ŗż╬źšźņĪ╝źÓź’Ī╝ź»żõĪóMatLab/SimulinkźŌźŪźļż“┼ļ║▄żĘż┐DSPźėźļź└Ī╝ź─Ī╝źļĪóź▐ź╚źĻź├ź»ź╣▒ķōQżõźĄźżź¾ź│źĄźżź¾▒ķōQż╩ż╔ż╬╔ŌŲ░Š«┐¶┼└▒ķōQIPź│źóż╩ż╔żŌ├ō┴TżĘżŲżżżļĪŻźŽźżź©ź¾ź╔ż╬DSPżŪ╣Į└«żĘżŲżżż┐źņĪ╝ź└Ī╝źĘź╣źŲźÓżõLTEź½Ī╝ź╔Īó╣ŌÅ]źĘźĻźóźļI/Oż╩ż╔ż“FPGAżŪ─¾ČĪż╣żļż│ż╚żŪź│ź╣ź╚Ī”Š├õJ┼┼╬üż“═▐ż©żŲ└Łē”ż“æųż▓żļźĘź╣źŲźÓż“╣Į├█żŪżŁżļż╚żĘżŲżżżļĪŻ

źČźżźĻź¾ź»ź╣ż╬FPGAżŪSoC│½╚»ź─Ī╝źļż“Ų³╬®Š╩¾ż¼╚»Ūõ

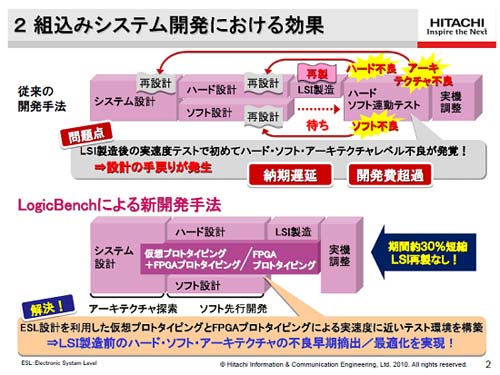

FPGAżŽĪóICż“▒■├ōĄĪ▀_ż╦─Š└▄╗╚ż”ż╚żżż”żĶżĻżŌĪóźĘź╣źŲźÓLSIżóżļżżżŽSoCż“║Ņżļż┐żßż╬źŽĪ╝ź╔ź”ź©źóĖĪŠ┌ż╦╗╚ż”ż┐żßż╬źųźņź├ź╔ź▄Ī╝ź╔┬Õż’żĻż╚żżż”╗╚ż’żņöĄż“żĘżŲżŁż┐ĪŻźóźļźŲźķż╬źķźżźąźļżŪżóżļźČźżźĻź¾ź»ź╣ż╬Virtex-6ż“┼ļ║▄żĘż┐ĪóźĘź╣źŲźÓLSI└▀╝ŖĖĪŠ┌├ōż╬│½╚»ź─Ī╝źļVirtualTurbo-IIIż“Ų³╬®Š╩¾─╠┐«ź©ź¾źĖź╦źóźĻź¾ź░ż¼╚»ŪõżĘż┐ĪŻż│ż╬ź─Ī╝źļż“╗╚ż©żąĪó└▀╝ŖżĘż┐SoCż¼ĖĮ╝┬ż╦Ų░ż»ż½ż╔ż”ż½ż╬└▀╝ŖĖĪŠ┌ż“╣įż”ż│ż╚ż¼żŪżŁżļĪŻ

Ų³╬®Š╩¾─╠┐«ż¼─¾ČĪż╣żļSoCĖĪŠ┌źĘź╣źŲźÓ

źĘź╣źŲźÓ└▀╝Ŗż¼Į¬ż’żĻRTLźņź┘źļż“Įą╬üż╣żļż╚ż╣ż░ż╦ĪóźĮźšź╚ź”ź©źó└▀╝Ŗż╚źŽĪ╝ź╔ź”ź©źó└▀╝ŖĪ╩ź═ź├ź╚źĻź╣ź╚ż½żķر═²└▀╝Ŗż╩ż╔Ī╦ż╦öĪżļŚlż└ż¼ĪóźŽĪ╝ź╔Ī”źĮźšź╚ż╬Č©─┤ĖĪŠ┌żõLSIźŽĪ╝ź╔ź”ź©źóövŽ®ŗ╩¼ż╬ĖĪŠ┌ĪóMatLab/SimuLinkż“ż─ż½ż├ż┐źŌźŪźļ▓ĮżõźĘź▀źÕźņĪ╝źĘźńź¾żŌ▓─ē”żŪżóżļĪŻSystemCźĘź▀źÕźņĪ╝źĘźńź¾ż╦żĶżļ▓Š„[źūźĒź╚ź┐źżźįź¾ź░żŪżŽĪóCPUźŌźŪźļżõźßźŌźĻĪ╝źŌźŪźļĪó╝■╩šéb═²źŌźŪźļĪóźąź╣źŌźŪźļĪó╝■╩šI/OźŌźŪźļż╩ż╔żŽż╣żŪż╦├ō┴TżĘżŲżóżĻĪóźżź¾ź┐Ī╝źšź¦Ī╝ź╣źŌźŪźļż└ż▒ż“VirtualTurbo-IIIż“╗╚żżFPGAźūźĒź╚ź┐źżźįź¾ź░żŪĖĪŠ┌ż╣żņżążĶżżĪŻ

ż│ż╬VirtualTurbo-IIIżŽ▒■├ōż╦żĶż├żŲź▓Ī╝ź╚┐¶ż¼żŌż├ż╚ØŁ═ūż╩╗■żŽĪóż╦Virtex-6 LX760ż“4Ė─żóżļżżżŽ2Ė─┼ļ║▄żĘż┐FPGAźŌźĖźÕĪ╝źļż“╝{▓├ż╣żļĪŻ4Ė─ż╬Šņ╣ńżŽ╣ŌÅ]ż╬ź╣źżź├ź┴ICż“╗╚żżFPGAż“└▄¶öżĘżŲżżżļĪŻż▐ż┐Īó2Ė─FPGAż╚DDR3źßźŌźĻĪ╝źŌźĖźÕĪ╝źļż“2Ė─ż╚FMCź│ź═ź»ź┐ź½Ī╝ź╔ż“┼ļ║▄żĘż┐FPGAźŌźĖźÕĪ╝źļżŽĮj═Ų╬╠źßźŌźĻĪ╝żõ╣ŌÅ]źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╬ĖĪŠ┌ż╦╗╚ż”ĪŻ