FPGAż╬─Ńź│ź╣ź╚Č\ĮčĪó╗■╩¼│õ3╝ĪĖĄźŪźąźżź╣ż╬ä▌Tabulaż¼Ų³╦▄ź¬źšźŻź╣ż“│½└▀

Xilinx(źČźżźĻź¾ź»ź╣)ż╬FPGAĪóVertexźĘźĻĪ╝ź║ż“╗žÄ¦Īó3╝ĪĖĄźßźŌźĻĪ╝ż╬Matrix SemiconductorĪ╩San Diskż¼2005ŃQż╦āA╝²Ī╦ż╬CEOż“ē»żßĪó│ū┐Ę┼¬ż╩źŪźČźżź¾żŪć@ż“żŽż╗ż┐źßźŌźĻĪ╝źßĪ╝ź½Ī╝ż╬Mostek╝ężŪź╣ź▐Ī╝ź╚(ĖŁżż)ź©ź¾źĖź╦źóż╚Ō}żążņż┐ĪóDennis SegersĢ■╬©żżżļä▌Tabula╝ę(╗▓╣═½@╬┴1)ż¼Ų³╦▄ź¬źšźŻź╣ż“│½└▀żĘż┐ĪŻ

Tabula╝ęĪ╩ź┐źėźÕźķż╚╚»▓╗Ī╦ż¼└▀╬®żĄżņż┐ż╬żŽ2003ŃQĪŻź▒źżźŪź¾ź╣╝ęĪ╩Cadence Design Systems)╝ężŪCTOĪ╩║Ū╣ŌČ\Įč└šŪżŪvĪ╦ż“ē»żßżŲżżż┐Steve TeigĢ■ż¼ÅŚČ╚żĘĪó2006ŃQż╦Dennis SegersĢ■ż“CEOż╚żĘżŲĘ▐ż©Ų■żņż┐ĪŻµ£ż»┐ʿʿżźóĪ╝źŁźŲź»ź┴źŃż╬FPGAĪóABAXźĘźĻĪ╝ź║ż“ĮążĘż┐ż╬żŽ2010ŃQżŪżóżļĪŻż│ż╬40nmźŪźČźżź¾ż╬FPGAż¼Ų▒╝ę║ŪĮķż╬×æēäż╚ż╩ż├ż┐ĪŻ

Ų▒╝꿎ä▌╣±ź½źĻźšź®źļź╦źó䔟Ąź¾ź┐ź»źķźķ(źżź¾źŲźļ╝ęż╬żóżļ├Ž░Ķ)ż╦╦▄╝ęż“╣Įż©Īó“£Č╚µ^ż¼ż▐ż└100ć@äėż╚żżż”Š«żĄż╩ź┘ź¾ź┴źŃĪ╝┤ļČ╚ż╦ż╣ż«ż╩żżĪŻż│żņż▐żŪź┘ź¾ź┴źŃĪ╝źŁźŃźįź┐źļĪ╩VCĪ╦ż½żķ┼ĻŲ■żĄżņż┐½@ČŌżŽ3övż╦┼Žż├żŲ╣ń╝Ŗ1▓»600╦³ź╔źļż╦ż╩ż├ż┐ż¼Īó║ŻŃQż╦ż╩ż├żŲżĄżķż╦1▓»800╦³ź╔źļż“╝{▓├Įą½@żĄż╗żļż│ż╚żŪ╦▄│╩┼¬ż╦źėźĖź═ź╣ż“╬®ż┴æųż▓ż┐ĪŻż│ż╬½@ČŌż“╗╚żżŲ³╦▄ź¬źšźŻź╣ż“└▀╬®żĘż┐ĪŻä▌╣±ż╬VCżŽźėźĖź═ź╣╬®ż┴æųż▓ż▐żŪż╦┐¶övż╦┼Žż├żŲ½@ČŌż“─¾ČĪż╣żļż¼ĪóŃ~╦ŠżŪżŽż╩żżż╚Ė½żļż╚Įą½@ż“éāż┴└┌żļĪŻTabulażŽ║ŻŃQż¼4övų`ż╬Įą½@ż└ż╚żżż”ż│ż╚żŪżóżļż½żķĪóä▌╣±ż╬VCżŽŃ~╦Šż╚Ė½żŲżżżļĪŻ

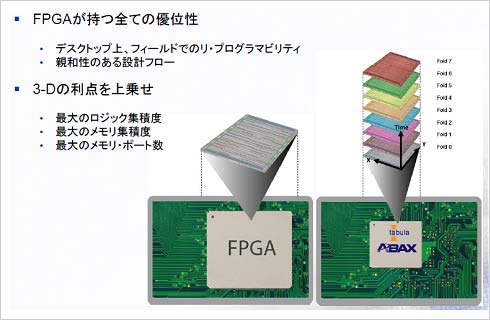

ż│ż╬ABAXżŽĪó╗■╩¼│õ3╝ĪĖĄFPGAż╚żżż”Č\Įčż¼┐ʿʿżĪŻż│żņż▐żŪż╬FPGAż╬║ŪĮjż╬╠õ¼öżŽź┴ź├źūĀC└čż¼ĮjżŁż»ż╩ż├żŲżĘż▐ż”ż│ż╚ż└ż├ż┐ĪŻFPGAżŽŪ█└■└▄¶öŠ╩¾ż“SRAMżŪ╝┬ĖĮż╣żļŚlż└ż½żķĪóź┴ź├źūĀC└čż¼ĮjżŁż»ż╩ż├żŲżĘż▐ż”ż╬żŽ┼÷ż┐żĻØiĪŻż│ż╬ż┐żßźūźĒź╗ź╣ż╦żŽ╚∙║┘▓Įż“═ūĄßżĘżŲżżż┐ĪŻTSMCż╩ż╔ż╬źšźĪź”ź¾ź╔źĻż¼│½╚»ż╣żļ║ŪĮķż╬└Ķ├╝źūźĒź╗ź╣żŽŠ’ż╦FPGAźßĪ╝ź½Ī╝ż¼ŠW├ōżĘżŲżŁż┐ĪŻźūźĒź╗ź╣ź╔źķźżźążŽFPGAż╚żżż©żļĪŻ▐köĄĪó╣Ō▓┴ż╩║Ū└Ķ├╝ż╬╚∙║┘▓ĮČ\ĮčĪóĮjżŁż╩ź┴ź├źūĀC└čĪóż╚żżż”ż│ż╚ż“▓├╠Żż╣żļż╚ź│ź╣ź╚żŽ╣ŌżżĪŻ

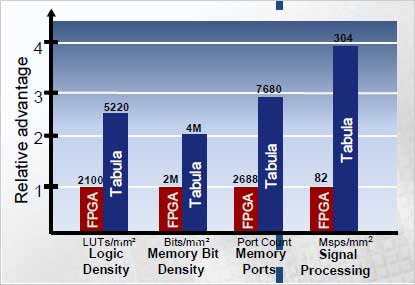

ABAXżŽĪóFPGAżŪżóżĻż╩ż¼żķźĻź│ź¾źšźŻź«źÕźóźķźųźļ╣Įļ]ż╦ż╩ż├żŲżżżļĪŻČ╦żßżŲ╣ŌÅ]ż╬╗■╩¼│õż“ŠW├ōżĘżŲövŽ®æä╠ŽżõLUTĪ╩źļź├ź»źóź├źūźŲĪ╝źųźļĪ╦┐¶ż“╗\żõż╣ż╬żŪżóżļĪŻ╗■╩¼│õż╬┐¶ż“╬Ńż©żą3╩¼│õż╩żķ═²éb┼¬ż╦żŽ3Ū▄ż╬ĮĖ└č┼┘ż╬FPGAż“╝┬ĖĮżŪżŁżļĪŻŠ}Įńż╚żĘżŲĪó╬Ńż©żą2100Ė─ż╬LUTźĒźĖź├ź»ż“╝┬╣įżĘż┐ĖÕĪó║ŪĮķż╬źĒźĖź├ź»ż“µ£żŲŪ“└Lż╦╠ßżĘĪó╝Īż╦╩╠ż╬2100Ė─ż╬LUTźĒźĖź├ź»ż“╝┬╣įż╣żļĪŻ║ŲżėźĒźĖź├ź»ż“Ū“└Lż╦╠ßżĘĪó3övų`ż╬LUTźĒźĖź├ź»ż“╝┬╣įż╣żļĪŻ

┐▐1ĪĪ╗■╩¼│õż╦żĶż├żŲövŽ®æä╠Žż“ŖW▓┴ż╦æųż▓żļABAXĪĪĮąųZĪ¦Tabula

╠Ž╝░┼¬ż╦┐▐ż“Į±ż»ż╚┐▐1ż╬żĶż”ż╦╗■┤ų┼¬ż╩3╝ĪĖĄżŪźĒźĖź├ź»┐¶ż“╗\żõżĘżŲżżżļż│ż╚ż╦ż╩żļĪŻź┴ź├źūĀC└迎Š«żĄż╩ż▐ż▐żŪż╣żÓĪŻ▒ķōQż╣żļźĒźĖź├ź»ż╬╣Į└«żõźŪźĖź┐źļövŽ®ż╦żĶż├żŲ═ź░╠└ŁżŽ░█ż╩żļż¼Īó┐«ęÄż“źĄź¾źūźĻź¾ź░ż╣żļżĶż”ż╩╗■┤ų╝┤ż“╣═╬ĖżĘż┐┐«ęÄĮĶ═²ż╦żŽ░Ą┼▌┼¬ż╩═ź░╠└Łż¼żóżļ(┐▐2)ĪŻTabula╝ęŲ³╦▄ź¬źšźŻź╣ż╬źĘź╦źóĪ”ź▐Ī╝ź▒źŲźŻź¾ź░Ī”źŪźŻźņź»ź┐Ī╝żŪżóżļ╣ė░µ▓ĒĢ■ż╦żĶżļż╚ĪóĪųFPGAżŽ─╠Š’ĪóövŽ®ż╬10~15%µć┼┘żĘż½Ų░║ŅżĄż╗żŲżżż╩żżż┐żßĪó╗■╩¼│õżŪŠ»żĘż║ż─övŽ®ż“╣Į└«żĘżŲżżż»ż│ż╚ż¼▓─ē”ż└Īūż╚żĘżŲżżżļĪŻ║ŪĮj▓─ē”ż╩╩¼│õæä╠ŽżŽ8╩¼│õµć┼┘ż└ż╚żżż”ĪŻź┴ź├źūĀC└迎“£═Ķż╬źŽźżź©ź¾ź╔FPGAż╬┐¶╩¼ż╬1żŪż╣żÓĪŻż│ż╬ż┐żß▓┴│╩żŽĪó┐¶╩¼ż╬1żŪż╣żÓż│ż╚ż╦ż╩żļĪŻ

┐▐2ĪĪFPGAżĶżĻżŌövŽ®æä╠ŽĪó└Łē”ż“╗\▓├żŪżŁżļĪĪĮąųZĪ¦Tabula

ż│ż╬öĄ╝░ż╬Š▄║┘żŽĖņżķż╩żżż¼Īóżżż½ż╦╣ŌÅ]ż╦└┌żĻü÷ż©ĪóźĒźĖź├ź»▒ķōQżóżļżżżŽLUTż“│õżĻ┼÷żŲĪó▒ķōQżĄż╗żļż½ĪóżĮż╬źóźļź┤źĻź║źÓżŪżóżĒż”ĪŻź▐źļź┴ź╣źņź├ź╔źūźĒź╗ź├źĄż╬ź╣ź▒źĖźÕĪ╝źĻź¾ź░ĄĪē”ż╚żĶż»ō¶żŲż¬żĻĪóż╔ż╬źĖźńźųż“ż╔ż”│õżĻ┼÷żŲżļż½Īóż╦ź╬ź”źŽź”ż¼żóżļĪŻ

ż│ż╬┐ʿʿżFPGAż╬┴└ż”▌xŠņżŽĮjæä╠ŽźŽźżź©ź¾ź╔ż╬źŲźņź│źÓ▌xŠņĪŻ─╠┐«ź╚źķźšźŻź├ź»ż╬╗\Įjż╦×┤żĘżŲŠ»żĘżŪżŌöv└■ż“ģ╬ż»ż╣żļż│ż╚ż¼ĄßżßżķżņżŲż¬żĻĪó▐k╚╠Š├õJŪvż¼▓╗╠mż½żķ▓ĶćĄĪó▒ŪćĄĪóżĘż½żŌżĶżĻæz£½ż╩▒Ū楿žż╚═ūĄßż¼¶öż»Ė┬żĻĪóĮjæä╠Žż╩FPGAż¼ĄßżßżķżņżļĪŻ╣ė░µĢ■ż╦żĶżļż╚ĪóNTTż½żķ┤╦▄╗┼══ż¼═┐ż©żķżņżŲżŌĪóźŪźČźżź¾╩čśŗżŽ100övż╦żŌĄ┌żųż│ż╚ż¼żóżļż╚żżż”ĪŻż└ż½żķźūźĒź░źķźÓ▓─ē”żŪ└@├ō┼¬ż╩źŪźąźżź╣ż╚żĘżŲFPGAżĘż½ż╩żżĪŻźŲźņź│źÓ░╩│░ż╦żŌ╩³┴„▒Ū楥Ī▀_/ź▐źļź┴źšźĪź¾ź»źĘźńź╩źļźūźĻź¾ź┐Ī╝ĪóCTź╣źŁźŃź╩Ī╝/MRI┼∙ż╬░Õ┬äĄĪ▀_ż╩ż╔ż╬▒■├ōż“┴└ż”ĪŻ

FPGAżŽ░cÖ┌ĄĪ▀_żŪżŌ╗╚ż’żņżŲżżżļĪŻķ]ŠĮźŲźņźėż╩ż╔ż╬ź┐źżź▀ź¾ź░źĖź¦ź═źņĪ╝ź┐żŽASIC┼∙żŪ║Ņ×æżŪżŁż╩żżĪŻż╚żżż”ż╬żŽĪóźŲźņźėż╬źżź¾ź┴źĄźżź║ż¼░Ńż”ż╚ASICż└ż╚ź╝źĒż½żķ└▀╝ŖżĘ─ŠżĄż╩ż▒żņżąż╩żķż╩żżż½żķż└Īóż╚╣ė░µĢ■żŽĖ└ż”ĪŻ┤╦▄╣Įļ]ż“ASICĪó╩čśŗ▓─ē”ż╩╗┼══ż“FPGAĪóż╚żżż”ĪóASIC+FPGAż╬źĘź╣źŲźÓżŪ║Ņż├żŲż¬ż▒żąFPGAż╬źūźĒź░źķźÓż“╩čśŗż╣żļż└ż▒żŪ┐ʿʿżźżź¾ź┴źĄźżź║ż╬źŲźņźėż╦żŌ×┤▒■żŪżŁżļĪŻż│ż│ż╦║ŪĮjż╬░Ų°PżŪżóżļ─Ńź│ź╣ź╚Č\Įčż¼▓├ż’żļż╚źėźĖź═ź╣ź┴źŃź¾ź╣ż¼╣Łż¼ż├żŲż»żļĪŻTabulaż╬ABAXżŽż▐żĄż╦FPGAż╬─Ńź│ź╣ź╚Č\ĮčżŪżóżļĪŻ

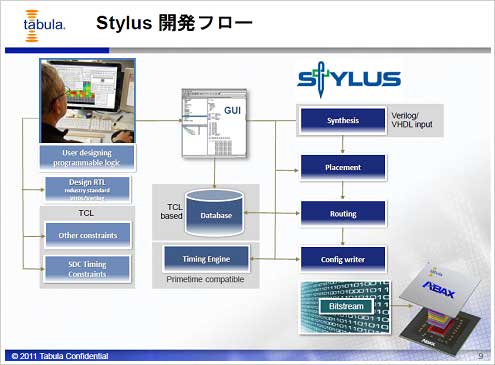

┐▐3ĪĪABAXż╬│½╚»ź─Ī╝źļStylusĪĪĮąųZĪ¦Tabula

FPGAż╬żĶż”ż╩źūźĒź░źķźÓźŪźąźżź╣żŽĪó│½╚»ź─Ī╝źļż╬Įą═Ķ╔įĮą═Ķż¼źėźĖź═ź╣└«Ė∙ż╬ź½ź«ż“É█żļĪŻTabulażŽ│½╚»ź─Ī╝źļStylusż“ź»źķź”ź╔ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż“─╠żĖżŲ─¾ČĪż╣żļĪŻRTLżŪż╬źĘź╣źŲźÓ└▀╝Ŗż“Į¬ż©ż┐ĖÕĪóStylusż“╗╚ż”ż╚ĪóRTLźŪĪ╝ź┐ż╬╣ń└«ĪóŪ█ÅøĪ”Ū█└■Īóconfigźķźżź┐Ī╝ż“ĘążŲźėź├ź╚ź╣ź╚źĻĪ╝źÓż“Įą╬üż╣żļ(┐▐3)ĪŻ“£═Ķż╬FPGAż╬RTLźŪĪ╝ź┐ż½żķ░╩æTż╬ĮĶ═²ż“Stylusż¼╣įż”ż╚żżż”Ślż└ĪŻź»źķź”ź╔ż“ŠW├ōż╣żļż╬żŽĪóźµĪ╝źČĪ╝ż╦żĶż├żŲ│½╚»ź─Ī╝źļż╬źąĪ╝źĖźńź¾ż¼ż▐ż┴ż▐ż┴żŪĘQ╝ęż┤ż╚ż╦źąĪ╝źĖźńź¾ż“┬Ęż©żļŠ}┤ųż¼Įj╩čż└ż½żķżŪżóżļĪŻź»źķź”ź╔ż“ŠW├ōż╣żņżąż╔ż╬źµĪ╝źČĪ╝żŪżŌ║Ū┐Ęż╬źąĪ╝źĖźńź¾ż“ź└ź”ź¾źĒĪ╝ź╔żŪżŁżļĪŻ╚ŠŲ│öüźßĪ╝ź½Ī╝Ŗõż╬╔ķ├┤żŽĮjżŁż»Ę┌žōżĄżņżļĪŻTabulażŽż│ż╬│½╚»ź─Ī╝źļż“╠Ą╬┴żŪ─¾ČĪż╣żļż╚żĘżŲżżżļĪŻ

╗▓╣═½@╬┴

1. ╣ź─┤ż╩┼┼╗ęŗēäĪ”─_┼┼┤ļČ╚ż╬»éōQż╚Īó┐Ę╩╣ż╦Įķ┼ąŠņżĘż┐ÅRų`ż╬╚ŠŲ│öüTabula╝ę (2011/05/23)