AMDżŌARMźóĪ╝źŁźŲź»ź┴źŃż“║╬├ōĪóCortex-A57ź│źóżŪźŽźżź©ź¾ź╔CPUż“╣Į└«

IntelĖ▀┤╣ĄĪż╬X86źóĪ╝źŁźŲź»ź┴źŃżŪ╣Ō└Łē”ż“╝{ĄßżĘżŲżŁż┐AMDż¼ż╚ż”ż╚ż”öĄ┐╦ż“╩čśŗż╣żļĪŻARMźóĪ╝źŁźŲź»ź┴źŃżŌŲ│Ų■ż╣żļż╬żŪżóżļĪŻAMDżŽźŽźżź©ź¾ź╔ż╬CPUż╚APU 3ĄĪ¹|ż“╚»╔ĮĪ󿔿┴SeattleĪ╩źĘźóź╚źļĪ╦ż╚żżż”ź│Ī╝ź╔ź═Ī╝źÓż“¤²ż▒żķżņż┐×æē俎ARMźóĪ╝źŁźŲź»ź┴źŃż“║╬├ōż╣żļĪŻ

┐▐1ĪĪGPUź│źóż“512Ė─ĮĖ└čżĘż┐APUĪųBerlinĪūĪĪĮąųZĪ¦AMD

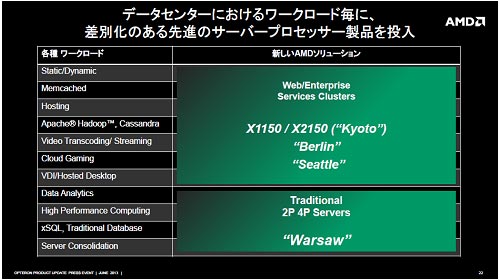

╚»╔ĮżĄżņż┐3ĄĪ¹|ż╬źūźĒź╗ź├źĄżŽĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõź©ź¾ź┐Ī╝źūźķźżź║Ī”źĄĪ╝źąĪ╝Ė■ż▒ĪŻARMźóĪ╝źŁźŲź»ź┴źŃż“║╬├ōżĘż┐Seattleż╦▓├ż©Īóx86ź┘Ī╝ź╣ż╬CPUż¬żĶżėAPUĪ╩źóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄĪ╦ż╬BerlinĪ╩ź┘źļźĻź¾Ī╦Īó“£═ĶĘ┐x86ż╬2źĮź▒ź├ź╚/4źĮź▒ź├ź╚ż╬źĄĪ╝źąĪ╝ż╦Ė■ż▒1ź’ź├ź╚Ī╩WĪ╦┼÷ż┐żĻż╬└Łē”ż¼═źżņż┐WarsawĪ╩ź’źļźĘźŃź’Ī╦ż¼żóżļĪŻ3ĄĪ¹|ż╚żŌ2014ŃQż╦Įą▓┘ż“═Į─ĻżĘżŲżżżļĪŻ

║ŻżõAMDżŽĪóCPUż╦ź░źķźšźŻź├ź»ź╣źūźĒź╗ź├źĄGPUź│źóż“ĮĖ└čżĘż┐źūźĒź╗ź├źĄż“APUż╚─Ļ▒IżĘżŲż¬żĻĪ󟎟żź©ź¾ź╔ż╬źĘź╣źŲźÓż╦żŌAPUż“╗╚ż├żŲżżż»ĪŻż│ż│żŪżŽGPUż“ĮĖ└čżĘżŲżżż╩żżźūźĒź╗ź├źĄż“CPUż╚Ō}ż¾żŪżżżļĪŻ3ĄĪ¹|ż╚żŌCPUż“─¾ČĪż╣żļż¼ĪóBerlinĪ╩┐▐1Ī╦żŽCPUż¬żĶżėAPUżŌ─¾ČĪż╣żļĪŻ║ŻŃQĮą▓┘ż“═Į─ĻżĘĪóż╣żŪż╦ź┘ź¾ź┴ź▐Ī╝ź»źŲź╣ź╚ż“Į¬ż©żŲżżżļ┐ĘĘ┐źūźĒź╗ź├źĄżŪżóżļOpeteron XźĘźĻĪ╝ź║Ī╩ź│Ī╝ź╔ć@KyotoĪ╦ż╚╚µż┘ĪóBerlinżŽGPUź│źóż╬┐¶ż“Kyotoż╬128Ė─ż½żķ512Ė─żžż╚╗\żõżĘż┐ĪŻ

ARMż╬64źėź├ź╚RISCźūźĒź╗ź├źĄCortex-A57ż╬8ź│źóż“ĮĖ└čżĘż┐SeattleżŽĪóOpteron XźĘźĻĪ╝ź║ż╚╚µż┘Īó1Wżóż┐żĻ2Ī┴4Ū▄ż╬└Łē”ż“─¾ČĪż╣żļż╚żĘżŲżżżļĪŻż│ż╬×æē俎2GHzż╬ź»źĒź├ź»żŪŲ░║ŅżĘĪó128Gźąźżź╚ż╬DRAMż“źĄź▌Ī╝ź╚ż╣żļĪŻżĄżķż╦ĪóSeattleż╬ĖÕ┘MĄĪ¹|ż╦żŽ16ź│źóż“ŲŌē┼ż╣żļ═Į─Ļż└ĪŻ

ARMźūźĒź╗ź├źĄź│źóżŽĪó32źėź├ź╚ż╦ż│ż└ż’żĻĘ╚┬ė┼┼ÅBĖ■ż▒ż╬─ŃŠ├õJ┼┼╬üż“źŽĪ╝ź╔ĀCż½żķżŌźĮźšź╚ĀCż½żķżŌ╝{ĄßżĘżŲżŁż┐ĪŻĘ╚┬ė┼┼ÅBżŪäėżż├Ž░╠ż“žéżßżļż╚ĪóĘ╚┬ėż½żķź▐źżź│ź¾żõ┴╚ż▀╣■ż▀ÅUżžż╚╝Īŗīż╦╣Ō└Łē”ż╬╩¼╠Ņżž┐╩ĮążĘżŲżżżŁż┐ĪŻżĮżĘżŲ║ŪżŌźŽźżź©ź¾ź╔ż╩źūźĒź╗ź├źĄź│źóż╚żĘżŲ64źėź├ź╚ż╬Cortex-A57ż“║“ŃQ╚»╔ĮżĘż┐ĪŻARMż╬äėż▀żŽĪó─ŃŠ├õJ┼┼╬üż╚Īóäė╬üż╩ź©ź│źĘź╣źŲźÓż└ĪŻ

ARMż╬źūźĒź╗ź├źĄź│źóż“ŠW├ōżĘżŲSoCżõAPUż“└▀╝Ŗż╣żļŠņ╣ńż╦żŽĪóAMBAżõAXIż╩ż╔ARMż¼│½╚»żĘż┐ŲŌŗźąź╣ż“╗╚ż”ż│ż╚ż¼żŪżŁżļĪŻARMż╬ź©ź│źĘź╣źŲźÓżŪżŽĪóż│ż╬ŲŌŗźąź╣╗┼══ż¼Įo│½żĄżņżŲż¬żĻĪóżĮż╬źūźĒź╚ź│źļż╦“£ż├żŲźĮźšź╚ź”ź©źó│½╚»żŪżŁżļż┐żßĪóź©ź│źĘź╣źŲźÓż╬īÖ├ōż╦żĶż├żŲ└▀╝Ŗ┤³┤ųż“ø]Į╠żŪżŁżļĪŻ

ź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐Ė■ż▒źšźĪźųźĻź├ź»żŪżóżļFreedom Fabricż“ź┴ź├źūæųż╦żŌĮĖ└čżĘżŲż¬żĻĪó┐¶╗hĪó┐¶╦³Ė─╩┬š`ż╦Ų░║ŅżĄż╗żļź╣źčź│ź¾ż╬CPUźµź╦ź├ź╚ż╚żĘżŲżŌ╗╚ż©żļĪŻŲ▒╗■ż╦“£═Ķż╬10Gbpsż╬Ethernetźżź¾ź┐Ī╝źšź¦Ī╝ź╣żŌĮĖ└čżĘżŲżżżļĪŻAMDżŽĪóSeattleż“2014ŃQŗī1╗═╚Š┤³ż½żķĮą▓┘żĘżŲżżż»ĪŻ

┐▐2ĪĪżĄż▐żČż▐ż╩▒■├ōż╦╗╚żż╩¼ż▒żŲżżż»ĪĪĮąųZĪ¦AMD

ż│żņżķ3ĄĪ¹|ż╬źūźĒź╗ź├źĄż“Īó“£═Ķż╬źĄĪ╝źąĪ╝ż╦▓├ż©Ī󟔟¦źųźĄĪ╝źąĪ╝żõĪó┤ļČ╚Ė■ż▒ż╬źĄĪ╝źėź╣ź»źķź╣ź┐ż╩ż╔żĄż▐żČż▐ż╩ź’Ī╝ź»źĒĪ╝ź╔Ī╩┐▐2Ī╦ż╦Ė■ż▒żŲżżżļĪŻ