1ź┴ź├źūMEMS CMOS ICż╬ź»źĒź├ź»╚»Ö┌▀_(d©ó)ż“SiLabsż¼×æēä▓Į

Silicon Laboratories╝꿎ĪóCMOS ICż╚MEMS┐ČŲ░╗ęż“źŌź╬źĻźĘź├ź»ż╦ĮĖ└čżĘż┐ź¬źĘźņĪ╝ź┐ż“?y©żn)æēä▓ĮżĘż┐ĪŻMEMSźķź╣ź╚ż╬źūźĒź╗ź╣żŪ×æļ]Īó┐ČŲ░╗ęż╚żĘżŲSiGeŪ÷╦ņż“├ōżżż┐ż│ż╚żŪSiżĶżĻżŌĄĪ│Ż┼¬?ji©Żng)ė┼┘ż¼ä?d©░ng)ż»ĪóŠå╬õÄźŠåÕXżõŠūĘŌż╦żŌäė(d©░ng)żżż┐żßĪóĪ▐20ppmż╬╝■āS┐¶ŖW─Ļ└Łż“10ŃQ┤ų╩▌Š┌ż╣żļĪŻ

┐▐1ĪĪSiGe MEMS┐ČŲ░╗ęż“1ź┴ź├źūż╦ĮĖ└čżĘż┐CMOSź¬źĘźņĪ╝ź┐ĪĪĮąųZ:ĪĪSiliconLabs

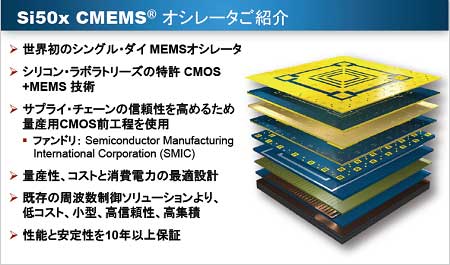

SiliconLabsż╬ż│ż╬┐Ę×æē俎Īóż│żņż▐żŪŲ▒╝ęż¼Ęeż├żŲżżż╩ż½ż├ż┐ź▄źĻźÕĪ╝źÓźŠĪ╝ź¾ż“┴└ż├ż┐╚»┐Č▀_(d©ó)żŪżóżļĪŻŲ▒╝꿎CMEMSż╚Ō}ż¾żŪżżżļĪŻCMOSæųż╦MEMSŗ╩¼ż“ĮĖ└čż╣żļČ\ĮčØŖß׿“Ų▒╝꿎╩▌Ń~żĘżŲż¬żĻĪóCMOS ICĘ┴└«░╩æTż╬źūźĒź╗ź╣ż╦ż─żżżŲżŽ£½żķż½ż╦żĘż╩żżĪŻ┐▐1ż╬║Ūæų┴žż¼MEMS┐ČŲ░╗ęź▐ź╣ź»ż“╔ĮżĘżŲżżżļĪŻż┐ż└żĘĪóźšźĪź”ź¾ź╔źĻSMICż╬║YØŹźūźĒź╗ź╣żŪ×æļ]żĘżŲżżżļĪŻźūźķź╣ź┴ź├ź»źčź├ź▒Ī╝źĖż╦╔§Ų■ż╣żļĪŻż│ż╬ż┐żß─Ńź│ź╣ź╚żŪ║Ņżļż│ż╚ż¼żŪżŁĪó1╦³Ė─ĻP(gu©Īn)Ų■ż╣żļŠņ╣ńż╬├▒▓┴żŽ0.44ź╔źļż╚żżż”ĪŻ

ż│żņż▐żŪż╬2ź┴ź├źūż╬MEMSź¬źĘźņĪ╝ź┐żŪżŽĪóź▄ź¾źŪźŻź¾ź░ź’źżźõĪ╝żŪMEMSź┴ź├źūż╚CMOS┐«ęÄ(gu©®)ĮĶ═²ź┴ź├źūż“└▄¶öżĘżŲżżż┐ĪŻMEMSČ”┐Č▀_(d©ó)ż╬ź▄ź¾źŪźŻź¾ź░ź’źżźõĪ╝żŽĪóź╬źżź║ż╬▒Ųūxż“£pż▒żõż╣ż»ĪóźĘź░ź╩źļźżź¾źŲź░źĻźŲźŻż¼╝Õżżż╚żżż”╠õ¼öż¼żóż├ż┐ż╚ĪóSiliconLabs╝ęź┐źżź▀ź¾ź░ŗ╠ńźĖź¦ź═źķźļź▐ź═źĖźŃĪ╝żŪźąźżź╣źūźņźĖźŪź¾ź╚ż╬Mike PetrowskiĢ■(hu©¼)żŽĮęż┘żļĪŻ

ż▐ż┐Īó“£═Ķż╬┐ÕŠĮ╚»┐Č▀_(d©ó)żŽż│żņż▐żŪ100ŃQŖZż»żŌ╗╚ż’żņżŲżŁż┐ż¼Īóź╗źķź▀ź├ź»źčź├ź▒Ī╝źĖż╦╝²ż▐ż├żŲż¬żĻĪóź│ź╣ź╚ż“▓╝ż▓żļż│ż╚ż¼žMżĘżżĪŻżĘż½żŌĪó┐ÕŠĮżŽĀCöĄ(sh©┤)Ė■ż╬ź½ź├ź╚ż“┬ō(li©ón)┘Iż╣żļż│ż╚ż╦żĶż├żŲča(b©│)┼┘░═┘T└Łż╬Š»ż╩żżĀCż“ź½ź├ź╚żĘżŲżżż┐ż¼ĪóżĮżņżŪżŌ╝■āS┐¶ż╬ča(b©│)┼┘╩č▓Įż¼ß×═ŲšJ(r©©n)░Žż“«Ćż©żļż┐żßĪóžĢča(b©│)ŌÅż╦Ų■żņż┐żĻĪóča(b©│)┼┘▌öĮ■ż“żĘż┐żĻżĘżŲżżż┐ĪŻ

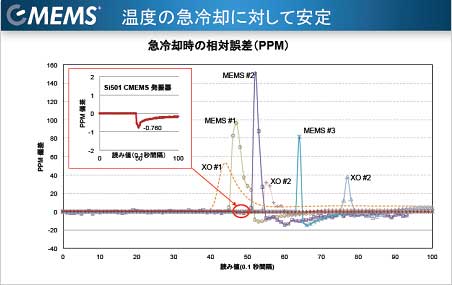

CMOSövŽ®ż╦źŌź╬źĻźĘź├ź»ż╦MEMS┐ČŲ░╗ęż“ĮĖ└čżŪżŁżļż╚żżż”ż│ż╚żŽĪóča(b©│)┼┘ź╗ź¾źĄżõźßźŌźĻżŌĮĖ└čżŪżŁżļż╚żżż”┴T╠ŻżŪżóżļĪŻż│ż╬×æēäżŪżŽĪóča(b©│)┼┘ź╗ź¾źĄż½żķż╬ča(b©│)┼┘ż“ĖĪē¶(m©©ng)żĘĪóżĮżņż╦“£ż”╝■āS┐¶ż“æ]ż┴Š├ż╣ż┐żßĪóżĮż╬▌öĮ■ĘĖ┐¶ż“źŪźĖź┐źļ╔įĦ╚»└ŁźßźŌźĻż╦ĄŁ▓▒żĘżŲż¬ż»ĪŻż│ż╬ż┐żßICźčź├ź▒Ī╝źĖż╬│░ż½żķĖ½żļż╚Īó╝■āS┐¶ż¼ż╔ż╬ča(b©│)┼┘ż╦×┤żĘżŲżŌŖW─ĻżŪ╩č▓Įż¼Š»ż╩żżĪŻ┐▐2żŽ-40ż½żķ+85ĪŅż╬╝■āS┐¶ż╬ča(b©│)┼┘╩č▓Įż“╔ĮżĘżŲżżżļĪŻ125Ė─ż╬źĄź¾źūźļż“źŲź╣ź╚żĘż┐żŌż╬żŪĪó╝┬╬ü├═ż“┐ā(j©®)żĘżŲżżżļĪŻ×æēä╩▌Š┌├═żŽĪ▐20ppmż╚ź▐Ī╝źĖź¾żŽ╣ŁżżĪŻĘą╗■╩č▓Įż╦żŌäė(d©░ng)ż»Īó1000Ų³┴Ļ┼÷ż╬▓├Å]╗Ņ┘xżŪżŌ╩č▓ĮżŽ1ppm░╩▓╝ż╚Š»ż╩żżĪŻ

┐▐2ĪĪ╝■āS┐¶ż╬ča(b©│)┼┘╩č▓Įż¼Š»ż╩żżĪĪĮąųZĪ¦SiliconLabs

ź¬źĘźņĪ╝ź┐żŽĄĪ│Ż┼¬ż╩┐ČŲ░ż“ŠW(w©Żng)├ōż╣żļż¼ĪóØŁ═ū░╩æųż╦äė(d©░ng)żżĄĪ│Ż┼¬ż╩┐ČŲ░ż╦żŌ┬čż©żķżņż╩ż▒żņżąż╩żķż╩żżĪŻżĮż│żŪĪóSiżĶżĻżŌäė(d©░ng)┼┘ż╬╣ŌżżSiGeŪ÷╦ņż“╗╚żżĪóMEMS┐ČŲ░╗ęż“Ę┴└«żĘż┐ĪŻ┐ÕŠĮ┐ČŲ░╗꿎Īó┐▐3ż╬żĶż”ż╦2┼└żŪܦż©żŲżżżļż¼Īó║Żövż╬MEMS┐ČŲ░╗꿎4┼└żŪ▓ĪżĄż©żŲżżżļĪŻż│ż╬ż┐żßĪóŠūĘŌżõŠåŚ„ż╩ča(b©│)┼┘╩č▓Įż╦×┤żĘżŲżŌ┐▐4ż╬żĶż”ż╦╩č▓Įż¼Č╦żßżŲŠ»ż╩żżĪŻż│ż╬ż│ż╚żŽĄĪ│Ż┼¬ż╦Č╦żßżŲäė(d©░ng)żżż│ż╚ż“┐ā(j©®)żĘżŲżżżļĪŻ

![┐▐3ĪĪ4┼└żŪܦż©żļĄĪ│Żäė(d©░ng)┼┘ż╬╣Ōżż╣Įļ]ĪĪĮąųZSiliconLabs](/archive/editorial/technology/img/TFC130703-01c.jpg)

┐▐3ĪĪ4┼└żŪܦż©żļĄĪ│Żäė(d©░ng)┼┘ż╬╣Ōżż╣Įļ]ĪĪĮąųZSiliconLabs

┐▐4ĪĪŠå╬õż╬╩č▓ĮżŽ1ppm░╩▓╝ĪĪŠåÕXżŌŲ▒══ĪĪĮąųZSiliconLabs

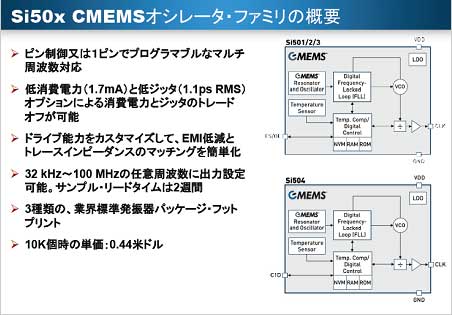

żĄżķż╦ż│ż╬┐Ę×æē俎Īó╝■āS┐¶ż“źūźĒź░źķźÓżŪ32kHzĪ┴100MHzż╬šJ(r©©n)░ŽŲŌżŪśOĮy(t©»ng)ż╦╩čż©żķżņżļĪŻżĮż╬ż┐żßż╦ź▐źļź┴źūźņź»ź╣żĄżņż┐1źįź¾ż“├ō┴TżĘżŲżżżļĪŻ×æē俎Īó┼┼Ė╗źįź¾Īó└▄├Žźįź¾Ī󟻟Ēź├ź»Įą╬üźįź¾ż╦źūźĒź░źķźÓźįź¾ż╬╣ń╝Ŗ4źįź¾ż“┤╦▄┼¬ż╦ŠW(w©Żng)├ōż╣żļ(┐▐5)ĪŻ

┐▐5ĪĪMEMS┐ČŲ░╗ęż“ĮĖ└čżĘż┐CMOS IC┐Ę×æēäĪĪĮąųZĪ¦SiliconLabs

╝■āS┐¶ż╬źūźĒź░źķź▀ź¾ź░żŽźšźĪĪ╝źÓź”ź©źóżŪżŌźµĪ╝źČĪ╝źūźĒź░źķźÓżŪżŌż╔ż┴żķżŪżŌ▓─ē”ż└ĪŻż│ż╬ż┐żßźĻĪ╝ź╔ź┐źżźÓżŽČ╦żßżŲø]ż»Īó┐ÕŠĮż╚żŽ░ŃżżĪ󟥟¾źūźļż“═ūĄßżĄżņżŲż½żķ2ĮĄ┤ųżŪĮą▓┘żŪżŁżļĪŻż▐ż┐ĪóźµĪ╝źČĪ╝ż¼źūźĒź░źķźÓż╣żļż┐żßż╬ź─Ī╝źļżŌ─¾ČĪż╣żļĪŻ

ż│żņż▐żŪż╬2ź┴ź├źūMEMSövŽ®ż╚╚µż┘żļż╚ĪóŲ░║Ņ┼┼╬«ż¼1.7mAż╚1ĘÕ─ŃżżĪŻ┼┼Ė╗┼┼░ĄżŽ1.71VĪ┴3.63VżŪżóżļż┐żßĪóŠ├õJ┼┼╬üżŽ┐¶mWżĘż½ż╩żżĪŻż▐ż┐Ī󟻟Ēź├ź»╚»Ö┌▀_(d©ó)ż╦─_═ūż╩źĖź├ź┐Ī╝ź╬źżź║żŽ1.1psĪ╩RMSĪ╦µć┼┘żŪżóżļż¼ĪóPetrowskiĢ■(hu©¼)żŽĪųMEMSČ\Į迎─ŃźĖź├ź┐Ī╝ż“įu(p©¬ng)żõż╣żżż╬żŪź»źĒź├ź»╚»Ö┌▀_(d©ó)ż╦Ė■żżżŲżżżļĪūż╚Įęż┘żļĪŻ