AlteraĪó14nm FinFETźūźĒź╗ź╣ż╬Stratix 10Č\Įčż“£½żķż½ż╦

Alteraż╬║Ū┐ĘFPGA/SoCżŪżóżļĪóStratix 10ż╬Č\Įčż╚╝┬└Łē”ż¼£½żķż½ż╦ż╩ż├ż┐ĪŻAlterażŽStratix 10ż“2013ŃQ10ĘŅż╦źĻźĻĪ╝ź╣żĘżŲżżż┐ż¼Īóż│ż╬ż█ż╔żĮż╬└Łē”ż╬╝┬╬ü├═ż╚żĮż╬╬ó¤²ż▒ż╚ż╩żļČ\Įčż╦ż─żżżŲ╚»╔ĮżĘż┐ĪŻ

┐▐1ĪĪStratix 10ż╬└Łē”ż╚╬ó¤²ż▒żļźŲź»ź╬źĒźĖĪ╝ĪĪĮąųZĪ¦Altera

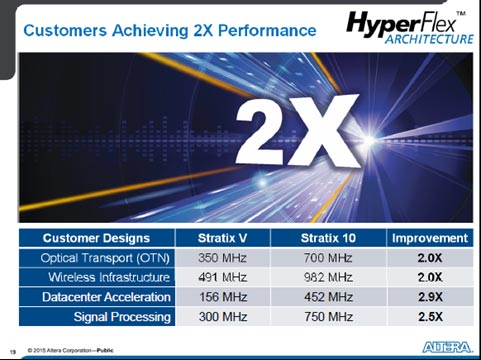

Stratix 10żŽ14nm FinFETźūźĒź╗ź╣żŪ×æļ]żĄżņżļFPGA & SoCĪŻIntelż¼źšźĪź”ź¾ź╔źĻż╦ż╩ż├żŲżżżļĪŻĖĮ└ż┬Õż╬Stratix 5ż╚╚µż┘żŲĪóź│źóż╬└Łē”żŽ2Ū▄░╩æųżŪżóżļż│ż╚ż“Ė„ź╚źķź¾źĘĪ╝źążõź’źżźõźņź╣┤├ŽČ╔ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬źóź»ź╗źķźņĪ╝ź┐Īó┐«ęÄĮĶ═²ż╩ż╔ż╬▒■├ōżŪ╝┬Š┌żĘż┐(┐▐2)ĪŻź│źóż╬└Łē”ż└ż▒żŪżŽż╩ż»ĪóŠ├õJ┼┼╬üżŽ║ŪĮjżŪ70%żŌ║’žōżĘĪóź╗źŁźÕźĻźŲźŻżŌ│╬╬®żĘż┐ĪŻ╔ŌŲ░Š«┐¶┼└▒ķōQ└Łē”żŽ║ŪĮj10TFLOPSĪóż╚GPUĪ╩ź░źķźšźŻź├ź»źūźĒź╗ź├źĄĪ╦╩┬ż▀ż“╝┬ĖĮżĘżŲżżżļĪŻ

┐▐2ĪĪ└Łē”żŽ2Ū▄░╩æųĪĪĮąųZĪ¦Altera

ż│żņżķż╬└Łē”ż“╝┬ĖĮż╣żļż┐żßĪóIntelż╬14nm FinFETż╦▓├ż©Īó2.5╝ĪĖĄICČ\ĮčżŌŠW├ōĪ󿥿ķż╦ź»źĻźŲźŻź½źļźčź╣ż╦źņźĖź╣ź┐ż“└▀ż▒Īóźčźżźūźķźżź¾┼¬ż╦źŪĪ╝ź┐ż“┼Š┴„żĄż╗żļHyperFlexźóĪ╝źŁźŲź»ź┴źŃż“║╬├ōżĘż┐ĪŻ

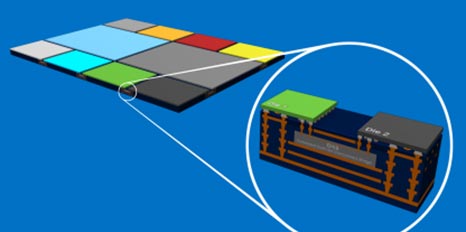

Intelż╬2.5╝ĪĖĄICżŽĪó“£═Ķż╬2.5D ICż╚żŽ░ŃżżĪóTSVż“╗╚ż’ż║ż╦╩┐ĀCæųż╦ź┴ź├źūż“╩┬ż┘żļSiPĪ╩Silicon in PackageĪ╦żŪżóżļĪŻ“£═Ķż╬2.5Dż└ż╚ĪóźĘźĻź│ź¾źżź¾ź┐ź▌Ī╝źČż╬æųż╦SoCżõźßźŌźĻĪóFPGAż╩ż╔╩Ż┐¶ż╬ź┴ź├źūż“ĮĖ└čżĘĪóźżź¾ź┐ź▌Ī╝źČż╬Ū█└■ż╦TSVż“Ņ~╗╚żĘż┐(╬Ńż©żąĪóXilinxĪ©╗▓╣═½@╬┴1)ĪŻ

AlterażŽż│ż╬SiPČ\Įčż“ĪóźžźŲźĒźĖź╦źóź╣3D SiPźżź¾źŲź░źņĪ╝źĘźńź¾ż╚Ō}żėĪó64źėź├ź╚ż╬ź▐źżź»źĒźūźĒź╗ź├źĄARM Cortex-A53ź│źóż“ŲŌē┼żĘż┐SoCż╦źßźŌźĻżõFPGAż╩ż╔ż“ĮĖ└čżĘżŲżżżļĪŻIntelżŽ“£═Ķż╬źĘźĻź│ź¾źżź¾ź┐ź▌Ī╝źČżõTSVż“╗╚ż’ż╩żżż│ż╬2.5DČ\Įčż“EMIBĪ╩Embedded Multi-die Interconnect BridgeĪ╦ż╚Ō}żų(╗▓╣═½@╬┴2)ĪŻEMIBżŪżŽĪóźĘźĻź│ź¾źżź¾ź┐ź▌Ī╝źČż╦┴Ļ┼÷ż╣żļź┴ź├źūż“ż░ż├ż╚Š«żĄż»żĘĪóŲ¾ż─ż╬ź┴ź├źūŲ▒╗╬ż“ż─ż╩ż░ż┐żßż╬Ū█└■ź┴ź├źūż╚żĘżŲĪóźūźĻź¾ź╚Ū█└■┤łż╦ļmżß╣■ż¾żŪżżżļ(┐▐3)ĪŻżżż’żą┤łŲŌē┼ź┴ź├źūČ\ĮčżŪżóżļĪŻż│ż╬źßźĻź├ź╚żŽĪóŪ█└■├ōź┴ź├źūż¼Š«żĄż»ĪóTSVżŌ╗╚ż’ż╩żżż┐żßĪó─Ńź│ź╣ź╚żŪ×æļ]żŪżŁżļż│ż╚ĪŻż┐ż└żĘĪóź┴ź├źūż“3Ė─ĮĖ└čż╣żļŠņ╣ńż╦żŽĪóŗī3ż╬ź┴ź├źūż╚└▄¶öż╣żļż┐żßż╬Ū█└■├ōź┴ź├źūż“żĄżķż╦┤łż╦ļmżß╣■żÓĪŻ

┐▐3ĪĪIntelż╬EMIBČ\ĮčĪĪź┴ź├źūŲ▒╗╬ż“ż─ż╩ż░Ū█└■ź┴ź├źūż“┤łż╦ļmżß╣■żÓĪĪĮąųZĪ¦Intel

HyperFlexźóĪ╝źŁźŲź»ź┴źŃżŽĪóŪ█└■ęÆūāż“žōżķż╣ż┐żßż╬Č\ĮčżŪżóżļĪŻ14nm FinFETČ\ĮčżŪżŽź╚źķź¾źĖź╣ź┐ż╬└Łē”żŽæųż¼żļżŌż╬ż╬ĪóŪ█└■ż“╚∙║┘▓ĮżŪżŁż║Ū█└■ęÆūāżŽĮjżŁż»žōżķż╩żżĪŻ14nmźūźĒź╗ź╣żŪżŽĪóŪ█└■ęÆūāż¼ź┴ź├źūµ£öüż╬ęÆūāż╬7Ī┴8│õż“žéżßżļż┐żßĪóż│ż╬ŗ╩¼ż“╣ŌÅ]▓Įż╣żļż│ż╚ż¼14nm LSIż╬╣ŌÅ]▓Įż╦ż─ż╩ż¼żļĪŻżĮż│żŪĪó└Łē”ż“ܦŪ█ż╣żļź»źĻźŲźŻź½źļźčź╣ż“£½żķż½ż╦żĘĪóżĮż╬ŗ╩¼ż╦źņźĖź╣ź┐ż“Ū█ÅøżĘżŲĪóźčźżźūźķźżź¾Ų░║Ņż“żĄż╗żļż│ż╚żŪĪó╝┬ä®┼¬ż╦Ū█└■ęÆūāż“╩¼│õżĘż┐ĪŻ

╬Ńż©żąĪó┐▐4ż╬żĶż”ż╦ĪóźĒźĖź├ź»övŽ®ż½żķźĒźĖź├ź»övŽ®ż▐żŪĪó“£═Ķż╬Č\Įčż╩żķ║Ū─╣3.5nsż½ż½żļż¼Īóż│ż╬HyperFlexżŪżŽ²ŗ├µż╦źņźĖź╣ź┐ż“Ų■żņżŲĪóęÆūāż“╩¼▓“ż╣żļĪŻHyperFlexżŪżŽ║Ū─╣żŪ1.2nsż╚Å]ż»ż╩żļż┐żßĪó╝■āS┐¶żŽ286MHz(3.5ns)ż½żķ833MHzĪ╩1.2nsĪ╦żžż╚æųż¼żļĪŻż╚żżż”ż╬żŽĪóźŪĪ╝ź┐ż“źĒźĖź├ź»ż½żķźņźĖź╣ź┐żžĪóźņźĖź╣ź┐ż½żķźņźĖź╣ź┐ĪóźņźĖź╣ź┐ż½żķźĒźĖź├ź»żžż╚┼Š┴„ż╣żļŠņ╣ńż╦żŽźčźżźūźķźżź¾┼¬ż╦┴„żĻ¶öż▒żļż│ż╚ż¼żŪżŁżļż½żķż└ĪŻ║ŪĮķż╬1źĄźżź»źļżŽ“£═Ķż╚Ų▒żĖżĶż”ż╦źņźżźŲź¾źĘżŽ╩čż’żķż║ęÆżżżŌż╬ż╬ĪóźĒźĖź├ź»ż½żķźĒźĖź├ź»żž║ŪĮķż╦┼■├ŻżĘż┐ĖÕżŽ│╩├╩ż╦Å]ż»ż╩żļĪŻ

![┐▐4ĪĪHyperFlexźóĪ╝źŁźŲź»ź┴źŃżŪźŪĪ╝ź┐┼Š┴„Å]┼┘ż“│╩├╩ż╦źóź├źūĪĪĮąųZĪ¦Altera](/archive/editorial/technology/img/TFC050609-01d.jpg)

┐▐4ĪĪHyperFlexźóĪ╝źŁźŲź»ź┴źŃżŪźŪĪ╝ź┐┼Š┴„Å]┼┘ż“│╩├╩ż╦źóź├źūĪĪĮąųZĪ¦Altera

║ŪŖZIntelżŽĪóAlteraż“āA╝²ż╣żļż│ż╚ż“»éżßż┐ż¼ĪóIntelż╦ż╚ż├żŲżŽAlteraż¼2ŃQØiż╦āA╝²żĘż┐EnpirionĪ╩╗▓╣═½@╬┴3Ī╦ż╬źčź’Ī╝ź▐ź═źĖźßź¾ź╚ICżŌ╠ź╬üĪŻIntelż╬ź▐źżź»źĒźūźĒź╗ź├źĄżŽĪó▒ķōQĮĶ═²ż¼ęÆż»żŲżŌżĶżżŠņ╣ńżŽśOŲ░┼¬ż╦┼┼Ė╗┼┼░Ąż“▓╝ż▓żļźŪźĖź┐źļ┼┼Ė╗ż“╗╚ż├żŲżżżļĪŻżĮżņżŌ10mVµć┼┘ż╬║┘ż½żż├▒░╠żŪ┼┼░Ąż“öUĖµż╣żļĪŻEnpirionż╬źčź’Ī╝ź▐ź═źĖźßź¾ź╚ICżŽĪóIntelż╬ź▐źżź»źĒźūźĒź╗ź├źĄ├ōż└ż▒żŪżŽż╩ż»ĪóFPGAż╬żĶż”ż╦─Ń┼┼░ĄÄźĮj┼┼╬«ż╬ICż“Ų░ż½ż╣ż┐żßż╦║Ū┼¼ż╩źŪźĖź┐źļPOL┼┼Ė╗żŪżóżĻĪóStratix 10żŪżŌEnpirionż╬ź┴ź├źūż╚┴╚ż▀╣ńż’ż╗żŲ╗╚ż”╝Ŗ▓Ķż╦ż╩ż├żŲżżżļĪŻ

║ŪĖÕż╦ź╗źŁźÕźĻźŲźŻż╦┤žżĘżŲżŌ┐©żņżĶż”ĪŻStratix 10ż╬ź╗źŁźÕźĻźŲźŻżŽSDMĪ╩ź╗źŁźÕźóźŪźąźżź╣ź▐ź═źĖźŃĪ╝Ī╦żŪ┤╔═²ż╣żļĪŻź╗źŁźÕźĻźŲźŻżŽ╝ńż╦3ż─ż╬Č\ĮčżŪ│╬╩▌ż╣żļĪŻ▐kż─żŽź╗ź»ź┐Ī╝ż┤ż╚ż╦Ū¦Š┌ż╚░┼ęÄ▓Įż“╗▄ż╣ĪŻŲ¾ż─ų`żŽ░█ż╩żļź┐źżźūż╬Ū¦Š┌ż“╗╚ż”ĪŻ3ż─ų`żŽPUFĪ╩Physically Unclonable FunctionĪ╦ĄĪē”żŪżóżļĪŻFPGAż╬ĘQź╗ź»ź┐Ī╝żŽĪóź│ź¾źšźŻź«źÕźņĪ╝źĘźńź¾ż╚źčĪ╝źĘźŃźļźĻź│ź¾źšźŻź«źÕźņĪ╝źĘźńź¾ż╬┤ųż╦Ū¦Š┌żĘĪóź╗ź»ź┐Ī╝┤ųż╬ź╗źŁźÕźĻźŲźŻż“│╬╩▌ż╣żļĪŻż▐ż┐Īó¾H┐¶ż╬Ū¦Š┌źŁĪ╝ż“Ė─╩╠ż╬╣Į└«övŽ®ż┤ż╚ż╦Ö┌└«żŪżŁżļĪŻ╬Ńż©żąĪóź╗ź»ź┐Ī╝Aż╬övŽ®źųźĒź├ź»żŪżŽĪó░█ż╩żļŲ¾ż─ż╬źĮĪ╝ź╣ż“╗╚ż├ż┐Ū¦Š┌ż¼żŪżŁżļĪŻPUFĄĪē”żŪżŽĪóźūźĒź╗ź╣Č\Įčż╬źąźķż─żŁż½żķÖ┌żĖżļ═┐¶ż“ŠW├ōżĘżŲĪóFPGAźŪźąźżź╣ż┤ż╚ż╦Ų╚śOż╬PUFż“Ęeż─ĪŻż│ż╬PUFż“FPGAż╬źļĪ╝ź╚źŁĪ╝ż“░┼ęÄ▓Įż╣żļĪŻ

░╩æųżŽFPGAŗ╩¼ż╦ż─żżżŲż╬ź╗źŁźÕźĻźŲźŻČ\ĮčżŪżóżļż¼ĪóCPUż╦żŽARMż“╗╚ż”ż┐żßĪóARM TrustZoneż“ź╗źŁźÕźĻźŲźŻźŠĪ╝ź¾ż╚żĘżŲŠW├ōżĘżŲżżżļĪŻStratix 10 FPGA & SoCż╬ESźĄź¾źūźļżŽ2014ŃQŗī4╗═╚Š┤³ż“═Į─ĻżĘżŲżżżļĪŻ

╗▓╣═½@╬┴

1. 28nmż╬FPGAżŽźżź¾ź┐ź▌Ī╝źČŠW├ōżŪTbpsż“╝┬ĖĮĪóź▐źļź┴ź│źóŲŌē┼żŪĮĶ═²+▓“└Ž├ōż╦ (2011/10/26)

2. Intel Custom Foundry EMIB

3. Alteraż¼╣ŌĖ·╬©┼┼Ė╗źßĪ╝ź½Ī╝ż╬Enpirionż“āA╝²żĘż┐═²Įyż╚żŽ? (2013/05/17)