IntelĪóCPUÄźFPGAÄź└ņ├ōASICż╬źžźŲźĒź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż“┐õ┐╩

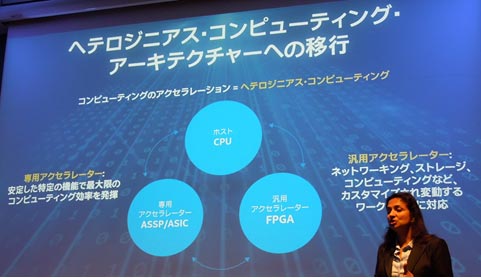

Intelż¼▐k║“ŃQAlteraż“āA╝²Īó╗▒▓╝ż╦┴╚ż▀╣■ż¾ż└ĖÕĪóĮķżßżŲż╚żŌżżż©żļCPUż╚FPGAż╬ź│źķź▄źņĪ╝źĘźńź¾ż╦ż─żżżŲ£½żķż½ż╦żĘż┐ĪŻIntelżŽźŪĪ╝ź┐ź½ź¾źčź╦Ī╝ż╦ż╩żļż│ż╚ż“║Yż▄ż”żĘżŲż¬żĻĪóź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż“▓├Å]ż╣żļ6ż─ż╬└«─╣╩¼╠Ņż“─ĻżßĪóżĮżņżķż╦×┤▒■żŪżŁżļźĮźĻźÕĪ╝źĘźńź¾ż╚żĘżŲĪóCPUż╚ASICĪóFPGAż½żķż╩żļ└@├ōż╬źžźŲźĒźĖź╦źóź╣ź│ź¾źįźÕĪ╝źŲźŻź¾ź░źóĪ╝źŁźŲź»ź┴źŃĪ╩┐▐1Ī╦ż“─¾░ŲżĘż┐ĪŻ

┐▐1ĪĪIntelż¼┐õ┐╩ż╣żļFPGAŠW├ōż╬źžźŲźĒźĖź╦źóź╣ź│ź¾źįźÕĪ╝źŲźŻź¾ź░

Intelż¼»éżßż┐6ż─ż╬└«─╣╩¼╠Ņż╚żŽĪó1Ī╦5Gź’źżźõźņź╣Īó2Ī╦źņĪ╝ź└Ī╝ż¬żĶżėÆņȧ▒¦├ĶĪó3Ī╦ź═ź├ź╚ź’Ī╝ź»Īó4Ī╦ź»źķź”ź╔ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Īó5Ī╦ź╣ź▐Ī╝ź╚źĘźŲźŻĪó6Ī╦śOŲ░▒┐┼ŠĪóż“╗žż╣ĪŻżĮżņżŠżņĪó1Ī╦żŪżŽMIMO/┐«ęÄĮĶ═²/ź╗źŁźÕźĻźŲźŻ/ź═ź├ź╚ź’Ī╝ź»ĄĪē”Īó2Ī╦żŪżŽĪóźėĪ╝źÓźšź®Ī╝ź▀ź¾ź░/FFTż¬żĶżėźšźŻźļź┐/AIżõĄĪ│Ż│žØ{Īó3Ī╦żŪżŽź╣źżź├ź┴ź¾ź░/ź╗źŁźÕźĻźŲźŻ/ĖĪØhĄ┌żėźņź▌Ī╝ź╚Īó4Ī╦żŪżŽAI/źėź├ź░źŪĪ╝ź┐╩¼└Ž/źėźŪź¬ź╚źķź¾ź╣ź│Ī╝źŪźŻź¾ź░/NFV+SDN/ź╣ź╚źņĪ╝źĖźóź»ź╗źķźņĪ╝źĘźńź¾/ź╗źŁźÕźĻźŲźŻż╚DPIĪó5Ī╦żŪżŽź╗ź¾źĄźšźÕĪ╝źĖźńź¾/AIżõĄĪ│Ż│žØ{/IoTź╗źŁźÕźĻźŲźŻĪó6Ī╦żŪżŽź╗ź¾źĄźšźÕĪ╝źĖźńź¾/ AIżõĄĪ│Ż│žØ{/ĄĪē”ŖWµ£/ź│ź═ź»źŲźŻźėźŲźŻĪóż╩ż╔ż╬Č\Įčż“╗╚ż”ĪŻ

ż│ż”żżż├ż┐Č\Įčż“╝┬ĖĮż╣żļż”ż©żŪĪó║ŪżŌ└@├ō└Łż╬żóżļ▓“ż╚żĘżŲĪóIntelżŽźžźŲźĒźĖź╦źóź╣ź│ź¾źįźÕĪ╝źŲźŻź¾ź░źóĪ╝źŁźŲź»ź┴źŃż“─¾░ŲżĘż┐ĪŻĖĄĪ╣ź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓżŽĪóźŽĪ╝ź╔ź”ź©źóż“Č”─╠ż╦żĘżŲźĮźšź╚ź”ź©źóż“╩čż©żļż│ż╚ż╦żĶż├żŲĪóżżżĒżżżĒż╩▒■├ōĄĪ▀_ż“╝┬ĖĮż╣żļż┐żßż╬źŲź»ź╬źĒźĖĪ╝żŪżóżļĪŻż┐ż└żĘĪóźĮźšź╚ź”ź©źóż└ż▒żŪźŪĪ╝ź┐ĮĶ═²ż“ż╣żļż╚ż╔ż”żĘżŲżŌęÆż»ż╩żļĪŻżĮż╬ŗ╩¼żŽźóź»ź╗źķźņĪ╝ź┐ż╚żĘżŲźŽĪ╝ź╔ź”ź©źóżŪ╣Į└«ż╣żļĪŻżĮż╬źŽĪ╝ź╔ź”ź©źóżŪżŌ»éż▐ż├żŲżżżļźóźļź┤źĻź║źÓż“╗╚ż”Šņ╣ńż╦żŽ└ņ├ōASICż“╗╚żżĪóźóźļź┤źĻź║źÓż¼╗■┬Õż╚Č”ż╦╩čż’żĻżõż╣żżźŲź»ź╬źĒźĖĪ╝ż╦żŽFPGAż“╗╚ż”ĪŻ

┐▐2ĪĪIntel╝ęProgrammable Solution DivisionĪóCustomer Experience Group├┤┼÷╔¹╝ę─╣ż╬Rina RamanĢ■

FPGAż╬╗╚żżöĄż╚żĘżŲżŽĪóīŽ┤ųż╦═ŌŲ³ż╬ź’Ī╝ź»źĒĪ╝ź╔ż“═Į▒RżĘĪóFPGAż“┴╚ż▀ż½ż©żļż│ż╚żŪĮ└Ųż╦źĄĪ╝źąĪ╝ż╬ŠW├ōĖ·╬©ż“æųż▓żļż│ż╚ż¼żŪżŁżļż╚Ų▒╝ęProgrammable Solution DivisionĪóCustomer Experience Group├┤┼÷╔¹╝ę─╣ż╬Rina RamanĢ■(┐▐2)żŽĮęż┘żŲżżżļĪŻ

żĄżķż╦Ų▒Ģ■żŽĪóFPGAż“╗╚ż├ż┐ź│ź¾źįźÕĪ╝źŲźŻź¾ź░źóź»ź╗źķźņĪ╝źĘźńź¾ż╬╝┬╬Ńż╚żĘżŲĪóź╔źżź─ż╬SWARM64╝ęż¼źŪĪ╝ź┐ź┘Ī╝ź╣ż╬╣ŌÅ]▓Įż“▓╠ż┐żĘż┐╝┬╬ŃżõĪóÖ┌öü▓╩│žĖ”ē|ż╬ä▌Broad Instituteż¼ź▓ź╬źÓ▓“└Žż╦╗╚żżČ╦żßżŲø]╗■┤ųżŪ▓“└ŽżŪżŁż┐Ą£╬Ńż╩ż╔ż“Šę▓żĘż┐ĪŻ├µ╣±ż╬e-ź│ź▐Ī╝ź╣▓±╝ęźóźĻźąźążŌFPGAżŪźŪĪ╝ź┐ĮĶ═²ż“╣ŌÅ]▓ĮżĘż┐ż╚żżż”ĪŻ

źŪĪ╝ź┐ź╗ź¾ź┐ż╩ż╔ż╬ź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓźóź»ź╗źķźņĪ╝ź┐ż╦FPGAż“Ų│Ų■żĘżŲźšźņźŁźĘźųźļż╩źŽĪ╝ź╔ź”ź©źóż“į~├▒ż╦╣Į├█żŪżŁżļżĶż”ż╦ż╣żļż┐żßĪóIntelżŽPACĪ╩Programmable Acceleration CardĪ╦ź½Ī╝ź╔ż╚Ō}żųFPGAź▄Ī╝ź╔(┐▐3)ż“źĄź¾źūźļĮą▓┘żĘż┐ĪŻż│żņżŽĪóCPUż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣żŪżóżļPCI Express Gen3ż“8źņĪ╝ź¾┼ļ║▄żĘż┐źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“Ęeż┴ĪóżŌż”▐köĄż╦żŽ║ŪĮj40Gbpsż╬QSFPĪ╩Quad Small Form-factor PluggableĪ╦źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“×óż©ż┐FPGAź▄Ī╝ź╔żŪżóżļĪŻQSFPżŽĪóźŪĪ╝ź┐─╠┐«ż╦żĶż»╗╚ż’żņżļź█ź├ź╚źūźķź¼źųźļż╩Ī╩Ų░║ŅėX▌åżŪżŌź│ź═ź»ź┐ż“┘UģsżŪżŁżļĪ╦ź╚źķź¾źĘĪ╝źąĪŻ

┐▐3ĪĪFPGAżŪövŽ®ż“└▀╝ŖżĘż┐żķżĮż╬ż▐ż▐╗╚ż©żļIntelż╬PAC

ż│ż╬FPGAź½Ī╝ź╔ż“źŪĪ╝ź┐ź╗ź¾ź┐ż╬ź│ź¾źįźÕĪ╝ź┐ź▐źČĪ╝ź▄Ī╝ź╔ż╦║╣żĘ╣■żßżąĪóCPUż╬╔ķ▓┘ż“╗\żõż╣ż│ż╚ż╩ż»ź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż“╣ŌÅ]ż╦żŪżŁżļĪŻ╗╚├ōż╣żļFPGAżŽĪóArria 10 GXż╚żżż”1,150Kż╬źĒźĖź├ź»ź©źņźßź¾ź╚ż“ĮĖ└čżĘż┐×æēäĪŻ

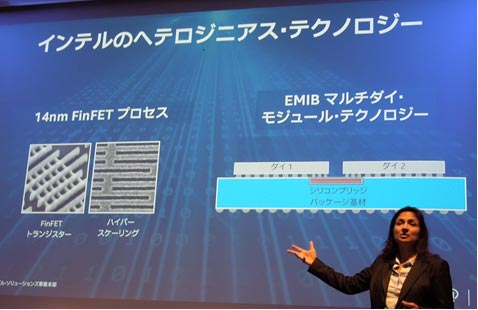

Arria 10źĘźĻĪ╝ź║żŽ20nmźūźĒź╗ź╣ż╬×æēäż└ż¼ĪóIntelżŽ9ĘŅż╦╚»╔ĮżĘż┐10nm FinFETźūźĒź╗ź╣ż╬FPGAżŪżóżļFalcon MesażŌ╝Ī└ż┬Õ├ōż╦£Žż©żŲżżżļĪŻż│ż╬┐ĘĘ┐FPGAżŽĪóźĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż“┤łż╦ļmżß╣■żÓEMIBĪ╩Embedded Multi-Die Interconnect BridgeĪ╦źčź├ź▒Ī╝źĖź¾ź░Č\ĮčĪ╩┐▐4Ī╦ż“╗╚ż”2.5D ICżŪżóżļĪŻźßźŌźĻżŽDRAMż“ź╣ź┐ź├ź»ż╦TSVżŪ─_ż═żļHBMĪ╩High Bandwidth MemoryĪ╦ż“źĄź▌Ī╝ź╚żĘżŲżżżļĪŻ

┐▐4ĪĪ10nmźūźĒź╗ź╣ż╬Falcon MesażŪżŽźĘźĻź│ź¾źųźĻź├źĖż╚Ō}żųźżź¾ź┐Ī╝ź▌Ī╝źČż“┤łż╦ļmżß╣■żÓ