CypressĪ󟻟ļź▐╗┼══NORźšźķź├źĘźÕż“źūźķź├ź╚źšź®Ī╝źÓ▓Į

Cypress SemiconductorżŽĪóśOŲ░┘Zź©źņź»ź╚źĒź╦ź»ź╣żžż╬NORźšźķź├źĘźÕż“źßźŌźĻ├▒öüż½żķź▐źżź│ź¾żŌĮĖ└čżĘż┐źßźŌźĻźĘź╣źŲźÓżžż╚źĮźĻźÕĪ╝źĘźńź¾╗žĖ■ż“äėżßżŲżżżļĪŻśOŲ░┘Z├ō²ŗżŪżŽ▓┐ż╚Ė└ż├żŲżŌ┐«═Ļ└Łż╚ŖWµ£└ŁżŽĪų└õ×┤Īūż└ż½żķżŪżóżļĪŻżżż’żąź┴ź├źūż╦┐«═Ļ└Łż╚ŖWµ£└Łż“┴╚ż▀╣■ż▀Īó╦³ż¼▐kĄ£Ė╬ż¼ÅŚżŁżŲżŌźšź¦źżźļ-ź╗Ī╝źšźĘź╣źŲźÓż“│╬╬®ż╣żļĪŻ

┐▐1ĪĪCypressźßźŌźĻ×æēäŗ╠ń├┤┼÷ź│Ī╝ź▌źņĪ╝ź╚EVPż╬Sam GehaĢ■

ĪųŠ”ēäć@ĪžSemper NORźšźķź├źĘźÕźßźŌźĻĪ┘żŽĪó┘Z║▄Ė■ż▒ż╬NORźšźķź├źĘźÕż“·t│½żĘżŲżżż»æųżŪż╬▐kż─ż╬źūźķź├ź╚źšź®Ī╝źÓżŪżóżļĪūż╚Ų▒╝ęźßźŌźĻ×æēäŗ╠ń├┤┼÷ź│Ī╝ź▌źņĪ╝ź╚EVPż╬Sam GehaĢ■(┐▐1)żŽĮęż┘żļĪŻż│ż╬Š”ēäż╬źßźŌźĻ═Ų╬╠ż╚żĘżŲżŽ512Mźėź├ź╚ż╚1Gźėź├ź╚ēäż½żķż▐ż║▌xŠņżžĮążĘżŲżżż»ĪŻ

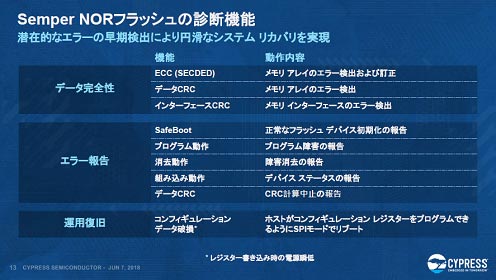

ź»źļź▐╗┼══żŪż╬NORźšźķź├źĘźÕż╬║ŪĮj(lu©░)ż╬źßźĻź├ź╚żŽĪó╔įĦ╚»└ŁżŪżóżļż│ż╚ż½żķź│Ī╝ź╔żõźŪĪ╝ź┐ż╬╩▌┘Tż╚Ų▒╗■ż╦║t╗■ż╬╬®ż┴æųż¼żĻż¼żŪżŁżļż│ż╚żŪżóżļĪŻżĄżķż╦ź»źļź▐╗┼══ż╚żżż”ż│ż╚żŪISO26262ĄĪē”ŖWµ£╗┼══ż╬ASIL-BĄ┌żėASIL-Dż╦ØŹĄ“żĘżŲżżżļż│ż╚żŽĖ└ż”ż▐żŪżŌż╩żżĪŻĖ╬ŠŃźŌĪ╝ź╔ż╬äŅ║▀┼¬ĖČ░°ż╬┴ß┤³ÜżéāĄĪē”żŌżóżļĪŻź╗źŁźÕźĻźŲźŻż╦żŽ╬®ż┴æųż¼żĻż╬SafeBootĄĪē”ż“×óż©ĪóCRCĪ╩Įõöv∙N─╣ĖĪØhĪ¦Cyclic Redundancy CheckĪ╦ż╦żĶż├żŲ▓■żČż¾żĄżņżŲżżż╩żżż½ż╔ż”ż½ż“│╬Ū¦ż╣żļĄĪē”żŌżóżļĪŻź╗źŁźÕźóż╩ŗ▓░ż“└▀ż▒ż┐ź╗ź»ź┐Ī╝╩▌ĖŅĪóźšź¦źżźļĪ”ź╗Ī╝źšĄĪē”ż“Ęeż─ź╗Ī╝źšźĻź╗ź├ź╚övŽ®ż╩ż╔ĄĪē”ŖWµ£övŽ®ż“Į╝╝┬żĄż╗ż┐(┐▐2)ĪŻēä䮟ņź┘źļżŽppbżŪżóżĻĪóź╝źĒźŪźŻźšź¦ź»ź╚ż└Īóż╚GehaĢ■żŽĖņżļĪŻ

┐▐2ĪĪĮ╝╝┬żĄż╗ż┐ÜżéāĄĪē”ĪĪĮąųZĪ¦Cypress Semiconductor

źšźķź├źĘźÕźßźŌźĻØŖŃ~ż╬ź”ź©źóźņź┘źĻź¾ź░Ī╩Ų▒żĖź╗źļż“▓┐┼┘żŌĮ±żŁ┤╣ż©żŲżżżļż╚Öæ╠┐ż¼═ĶżŲ╗╚ż©ż╩ż»ż╩żļż│ż╚ż“ķcż▒żļż┐żßż╦ĪóĮ±żŁ┤╣ż©żļź╗źļż“żŪżŁżļż└ż▒Čč┼∙ż╦ż╣żļĄĪē”Ī╦żŌĘeż┴Ī󿥿ķż╦źßźŌźĻź╗źļźóźņźżż“ź│ź¾źšźŻź«źÕźóźķźųźļż╦╩¼│õżŪżŁżļEnduraFlexĄĪē”żŌżóżļĪŻż│żņżŽźßźŌźĻźóźņźżż“╩Ż┐¶ż╬źčĪ╝źŲźŻźĘźńź¾ż╦╩¼│õżĘĪóźčĪ╝źŲźŻźĘźńź¾ż┤ż╚ż╦╣Ō┬čĄū└Łżõ─╣┤³╩▌┘Tż╦║Ū┼¼▓Įż╣żļĪŻ

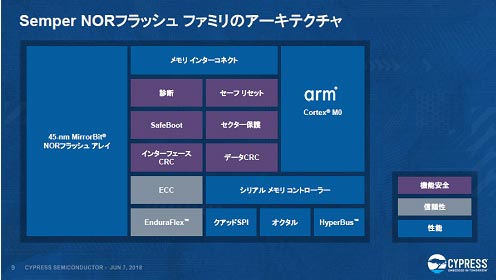

┤╦▄źóĪ╝źŁźŲź»ź┴źŃżŽ┐▐3ż╦┐āż╣żĶż”ż╦ĪóNORźšźķź├źĘźÕźßźŌźĻź╗źļźóźņźżż╦▓├ż©Īóarmż╬Cortex-M0ź▐źżź│ź¾żŪĄĪē”ŖWµ£żõź╗źŁźÕźĻźŲźŻĄĪē”ż“öUĖµż╣żļĪŻźżź¾ź┐źšź¦Ī╝ź╣żŽźĘźĻźóźļźżź¾ź┐źšź¦Ī╝ź╣ż“4Ė─╩┬š`ż╦żĘż┐ź»źóź├ź╔SPIż╚8Ė─╩┬š`ż╬ź¬ź»ź┐źļSPIĪóHyperBusźżź¾ź┐źšź¦Ī╝ź╣żŌĘeż─ĪŻ│░ŗ├╝╗ęż“žōżķż╣ż┐żßĪóØŖż╦ź»źļź▐żŪżŽŪ█└■╦▄┐¶ż╬║’žōżŽØŁ┐▄ż└ĪŻż│ż╬ż┐żßźĘźĻźóźļźżź¾ź┐źšź¦Ī╝ź╣żŪŪ█└■╦▄┐¶(źįź¾┐¶)ż“žōżķżĘżŲżżżļĪŻ

┐▐3ĪĪ┤╦▄övŽ®ż“źūźķź├ź╚źšź®Ī╝źÓ▓ĮĪĪźµĪ╝źČĪ╝ż╬═ūĄßż╦żĶż├żŲ╗╚ż’ż╩żżövŽ®żŌĮążŲż»żļĪĪĮąųZĪ¦Cypress Semiconductor

ż│ż╬NORźšźķź├źĘźÕż¼źūźķź├ź╚źšź®Ī╝źÓż└ż╚żżż”ż╬żŽĪóż│ż╬övŽ®źųźĒź├ź»ż“źŌźĖźÕĪ╝źļöĄ(sh©┤)╝░ż╦żĘżŲżżżļż½żķż└ĪŻźµĪ╝źČĪ╝ż╬╗┼══ż╦▒■żĖżŲ╗╚ż’ż╩żżövŽ®żŌ┼ļ║▄żĘżŲż¬ż»ż│ż╚żŪź│ź╣ź╚ź└ź”ź¾ż“┐▐ż├żŲżżżļĪŻ╬Ńż©żąĪ󟻟óź├ź╔SPIż└ż▒żŪØ▓╩¼ż╚źµĪ╝źČĪ╝ż╦żŽź¬ź»ź┐źļSPIżŽ╗╚ż’ż║ż╦żĮż╬ż▐ż▐ż╦żĘżŲż¬ż»ĪŻź┴ź├źūĀC└迎╠ĄŠGż╦ż╩żļżĶż”ż╦Ė½ż©żļż¼ĪóövŽ®└▀╝Ŗż╬Š}┤ųżõ╗■┤ųż“╣═ż©żļż╚ż│ż╬öĄ(sh©┤)ż¼ź│ź╣ź╚żŽ▓╝ż¼żļĪŻTATż╬ø]Į╠ż╦żŌż╩żļĪŻ╣ŌÅ]└Łż¼═▀żĘżżźµĪ╝źČĪ╝ż╦żŽHyperBus╗┼══żŪŲ╔ż▀Įąż╗żąź»ź’ź├ź╔SPIż¼102MB/sż╬ż╚ż│żĒĪó400MB/sż╦╣ŌÅ]▓ĮżŪżŁżļĪŻ

45nmźūźĒź╗ź╣żŪĪóź╗źļŗ╩¼żŽÖ┌═Ķ2źėź├ź╚/ź╗źļ╣Į└«żŪżóżļMirrorBitČ\Įčż“╗╚ż├żŲżżżļĪŻźßźŌźĻ═Ų╬╠żŽĪó512Mźėź├ź╚ż½żķ1Gźėź├ź╚ż╬ź┴ź├źūż“└▀╝ŖżĘżŲż¬żĻĪó2Gźėź├ź╚Īó4Gźėź├ź╚ż╦żŽź╣ź┐ź├ź»╣Į└«żŪ├ō┴Tż╣żļĪŻ

512Mźėź├ź╚ēäż“╝ń═ūĖ▄ĄęĖ■ż▒ż╦źĄź¾źūźļĮą▓┘żĘżŲż¬żĻĪóæä│╩ØŹĄ“ēäż╬źĄź¾źūźļĮą▓┘żŽ2018ŃQŗī4╗═╚Š┤³ż“═Į─ĻżĘżŲżżżļĪŻ24ź▄Ī╝źļBGAż╚16ēäSOICĪó8├╝╗ęż╬WSONźčź├ź▒Ī╝źĖżŪż╬╬╠ŠÅ│½╗ŽżŽ2019ŃQŗī1╗═╚Š┤³ż“═Į─ĻżĘżŲżżżļĪŻ