XilinxĪóśOŲ░▒┐┼ŠĖ■ż▒ż┐SoCż╬źĒĪ╝ź╔ź▐ź├źūż“£½żķż½ż╦

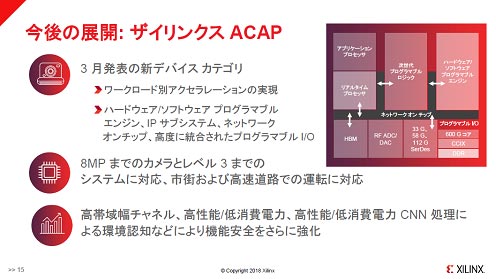

Xilinxż¼śOŲ░┘Zź©źņź»ź╚źĒź╦ź»ź╣ż╦żĖż’żĖż’ż╚ŠĶżĻĮążĘżŲżżżļĪŻ2014ŃQżŽż▐ż└14╝ęż╬29źŌźŪźļż╦żĘż½Ų■żĻ╣■żßż╩ż½ż├ż┐ż¼Īó2017ŃQż╦żŽ26╝ę96źŌźŪźļż╦╣Łż▓Īó2018ŃQżŽ29╝ę111źŌźŪźļż╦┐®żż╣■żßżļż╚Ė½╣■ż¾żŪżżżļĪŻFPGAż╚żżż├ż┐źŽĪ╝ź╔ź”ź©źó└ņ├ōövŽ®ż“║ŅżļźŪźąźżź╣ż╬║ŪĮj(lu©░)ż╬ØŖ─╣żŽź│ź¾źįźÕĪ╝źŲźŻź¾ź░ē”╬üżŪżóżĻĪóśOŲ░▒┐┼Šż╬رöüŪ¦╝▒ż╦░ę╬üż“╚»Ä¦ż╣żļĪŻ3ĘŅż╦╚»╔ĮżĘż┐┐ĘźóĪ╝źŁźŲź»ź┴źŃACAPż╬Š▄║┘ż“ż│ż╬ż█ż╔£½żķż½ż╦żĘż┐ĪŻ

┐▐1ĪĪź»źļź▐ż╦┼ļ║▄ż╣żļ£å│ąź╗ź¾źĄżŽ¾Hż»ż╩żļĪĪĮąųZĪ¦Xilinx

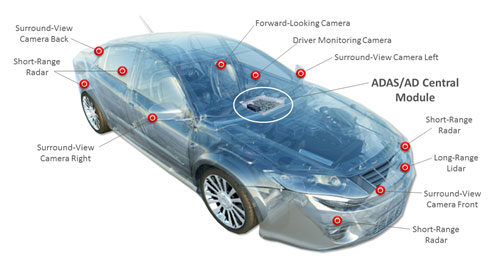

Xilinxż¼┴└ż”ADASżŪżŽĪóźšźĒź¾ź╚ź½źßźķźŌźĖźÕĪ╝źļż½żķż╬▒Ū楿½żķØiöĄ(sh©┤)ż╬رöüż“ŠĶ├ō┘ZĪóź╚źķź├ź»ĪóśO┼Š┘ZĪó┐═ż╩ż╔ż“Ė½╩¼ż▒żļż┐żßż╬▒ķōQż╦FPGAżõSoCż“╗╚ż”ĪŻżĮż╬ź╗ź¾źĄżŽź½źßźķż└ż▒żŪżŽż╩ż»ĪóźņĪ╝ź└Ī╝żõLiDARż╩ż╔żŌżóżļĪŻżĘż½żŌĪóżĮż╬┐¶żŽ¾Hżż(┐▐1)ĪŻźĄźķź”ź¾ź╔ź½źßźķż╦żŽØiĖÕ║ĖīÜż╦║Ū─Ń4±śĪóżĮżņż╚żŽ╩╠ż╦ØiöĄ(sh©┤)ż“Ė½żļż┐żßż╬└ņ├ōź½źßźķĪó╝■░Ž╗═ā║ż½żķ╝■░Žż╦żóżļرöüż“ĖĪĮąż╣żļż┐żßż╬ŖZš{(di©żo)▀`źņĪ╝ź└Ī╝4Ė─ĪóżĮżĘżŲØiöĄ(sh©┤)100m└Ķż▐żŪĖ½żķżņżļLiDARżŌżżżļĪŻż│ż╬ż┐żßĪóżĮżņżķż╬ź╗ź¾źĄźŪĪ╝ź┐ż“╠Jż═żŲźŪĪ╝ź┐ż“ĮĶ═²ż╣żļź╗ź¾źĄźšźÕĪ╝źĖźńź¾ż¼’Lż½ż╗ż╩ż»ż╩żļĪŻż│ż│ż╦żŌFPGAż╩ż╔ż╬źĒźĖź├ź»ż¼ØŁ═ūż╦ż╩żļĪŻ

źĄźķź”ź¾ź╔źėźÕĪ╝żŽ4±śż╬ź½źßźķ▒Ū楿“╣ń└«żĘżŲź░źķźšźŻź├ź»ź╣żŪ╔ĮĖĮż╣żļźĘź╣źŲźÓĪŻ│©▓Ķ楿“ż─ż╩ż░ż┐żßż╬▒ķōQż╦żŌFPGAżŽ╗╚ż©żļĪŻø]š{(di©żo)▀`źņĪ╝ź└Ī╝żŽ24GHzµć┼┘ż╬ØŹź▀źĻāSż“╗╚żżĪóżĮż╬╚┐╝oāSż½żķرöüż╬Ń~╠Ąż“ĖĪĮąż╣żļĪŻź»źļź▐ż╬ØiĖÕż╬╗═ā║ż╦żŽĪóź╔źķźżźąĪ╝ż½żķĘx│čż╦ż╩żļż┐żßż│ż╬ź╗ź¾źĄż¼ØŁ═ūĪŻż┐ż└żĘĪó«Ć▓╗āSź╗ź¾źĄż“╗╚ż”Š}żŌżóżļĪŻż▐ż┐LiDARżŽźņĪ╝źČĪ╝Ė„ż“╗╚ż├żŲżĮż╬╚┐╝oż½żķرöüĖĪĮąż╚š{(di©żo)▀`ż“▒Rżļź╗ź¾źĄżŪżóżļĪŻź▌źĻź┤ź¾ź▀źķĪ╝ż“╗╚ż├żŲ┘Zż╬╝■░Žż“ź░źļź░źļĖ½┼Žż╣żĶżĻżŌĪóØiöĄ(sh©┤)ż╬£å╠Ņż“100źßĪ╝ź╚źļż▐żŪäPżążĘĪó¾H┐¶ż╬ź╗ź¾źĄż“╗╚ż”öĄ(sh©┤)ż¼ŖWµ£└Łż¼╣Ōż▐żļĪŻ

¾Hż»ż╬ź╗ź¾źĄż½żķż╬┐«ęÄ(gu©®)źŪĪ╝ź┐ż“┴T╠Żż╬żóżļŠ╩¾ż╦╩č┤╣ż╣żļż┐żßż╬ĮĶ═²ż╦FPGAż“żŽżĖżßż╚ż╣żļźĒźĖź├ź»żõźūźĒź╗ź├źĄż“╗╚ż”ĪŻFPGAŖõż½żķĖ½żŲĪóĮĖ└č┼┘ż¼╣Ōż»ż╩żĻźĘź╣źŲźÓ▓Įż¼äėż»ż╩żņżąż╩żļż█ż╔Īóµ£żŲż“└ņ├ōż╬źŽĪ╝ź╔ź’źżźõĪ╝ź╔övŽ®żŪ╣Į└«ż╣żļż│ż╚żŽź│ź╣ź╚┼¬ż╦Ė½╣ńż’ż╩ż»ż╩żļĪŻżĮż│żŪĪóźĮźšź╚ź”ź©źóżŪźšźņźŁźĘźųźļż╦×┤▒■ż╣ż┘żŁĄĪē”ż╚ĪóźŽĪ╝ź╔ź”ź©źóżŪ╣ŌÅ]ĮĶ═²ż╣ż┘żŁĄĪē”ż“└▐żĻ╣■żÓØŁ═ūż¼ĮążŲż»żļĪŻż│ż╬ż┐żßĪó╣ŌĮĖ└čFPGAżŽSoCż╦ŖZż┼żżżŲżżż»ĪŻ

Xilinxż╬╣ŌĮĖ└čFPGAżŽSoCż╚ż╩żĻĪóSoCż╬├µż╦╩čśŗ(g©░u)▓─ē”ż╩źĒźĖź├ź»Ī╩FPGAĪ╦ż╬ż█ż½ż╦ĪóźĮźšź╚ź”ź©źóżŪ╩čśŗ(g©░u)▓─ē”ż╩CPUĪ󿥿ķż╦źßźŌźĻż╩ż╔żŌĮĖ└čżĘżŲżżżļż¼Īóżóżļµć┼┘»éż▐ż├ż┐ĄĪē”ż╩żķ└ņ├ōövŽ®ż╚żĘżŲĮĖ└čżĘżŲż¬ż»Š}żŌżóżļĪŻ

┐▐2ĪĪ3ĘŅż╦─¾░ŲżĘż┐┐ĘźóĪ╝źŁźŲź»ź┴źŃż╬SoCĪĪĮąųZĪ¦Xilinx

żĮż│żŪXilinxżŽĪó╩Ż┐¶ż╬└ņ├ōövŽ®Ī╩IPźĄźųźĘź╣źŲźÓź│źóĪ╦ż“ź└źżź╩ź▀ź├ź»ż╦└┌żĻü÷ż©żķżņżļDFXĪ╩Dynamic Function eXchangeĪ╦ż╚żżż”ĄĪē”ż“└▀ż▒żļĪŻż│żņżŽĪó╬Ńż©żąśOŲ░▒┐┼Šż╬ėXČĘż╦żĶż├żŲĪó╣ŌÅ]╠OŽ®┴÷╣į├µż╚Īó├¾┘ZŠņżŪż╬śOŲ░┴÷╣įż╬░Ńżżż“ź└źżź╩ź▀ź├ź»ż╦└┌żĻü÷ż©żļż│ż╚ż¼żŪżŁżļż╚żżż”ĄĪē”ż└ĪŻ╗■┤ų┼¬ż╩¾H─_▓ĮźŽĪ╝ź╔ź”ź©źóövŽ®ż“ż│ż╬SoC░╩│░ż╦ĮĖ└čż╣żļżĶżĻżŽźĘź╣źŲźÓż“Š«Ę┐ż╦żŪżŁżļĪŻ

ż▐ż┐ĪóOTAĪ╩Over the AirĪ╦żŪżŽźĮźšź╚ź”ź©źóż╬źóź├źūźŪĪ╝ź╚ż└ż▒żŪżŽż╩ż»źŽĪ╝ź╔ź”ź©źóż╬ĄĪē”ż╬źóź├źūźŪĪ╝ź╚żŌ▓─ē”ż╦ż╣żļĪŻżĄżķż╦żŽ┐ĘĄĪē”ż╬╝{▓├żõAIźóźļź┤źĻź║źÓż╩ż╔ż╬śŗ(g©░u)┐ĘĪ󿥿ķż╦żŽź▀ź├źĘźńź¾ź»źĻźŲźŻź½źļż╩ĄĪē”(╬Ńż©żąź╗źŁźÕźĻźŲźŻźóźļź┤źĻź║źÓż╬śŗ(g©░u)┐ĘĪ╦ż╦żŌ×┤▒■żŪżŁżļżĶż”ż╦ż╣żļż╚żĘżŲżżżļĪŻ