XilinxĪó«Ć╣ŌĄķ2.5D-LSIż╬µ£╦Ųż“£½żķż½ż╦

XilinxżŽĪó╣Ō┼┘ż╩LSIżŽµ£żŲFPGAżŪ┴╚żÓż╬żŪżŽż╩ż»ĪóźĮźšź╚ź”ź©źóź┘Ī╝ź╣ż╬ź▐źļź┴ź│źóCPUżõĪóź└źżź╩ź▀ź├ź»ż╦║Ų╣Į└«▓─ē”ż╩źŽĪ╝ź╔ź”ź©źóź©ź¾źĖź¾ĪóAI└ņ├ō┐õébövŽ®ĪóDSPĪóDDR RAMĪó╝■╩šövŽ®ĪóI/Oż╩ż╔ż“ĮĖ└čż╣żļĪų«Ć╣ŌĄķLSIĪūACAPĪ╩Adaptive Compute Acceleration PlatformĪ¦┼¼▒■Ę┐▒ķōQ▓├Å]źūźķź├ź╚źšź®Ī╝źÓĪ╦ż╬┴└żżż“£½żķż½ż╦żĘż┐ĪŻ

┐▐1ĪĪXilinx╝ęCEOż╬Victor PengĢ■

ż│żņżŽĪó╝┬äóĘ┴▌åæųżŽźĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż“├ōżżż┐2.5╝ĪĖĄLSIżĮż╬żŌż╬żŪżóżļż¼Īóż│żņż½żķż╬Įjæä╠ŽLSIż╬öĄĖ■ż╚żĘżŲĪóCPUż╚DSPĪóAIź©ź¾źĖź¾ĪóżĮżĘżŲFPGAż“ĮĖ└čż╣żļż│ż╚żŪż█ż╚ż¾ż╔µ£żŲż╬ĄĪē”ż“╝┬ĖĮżŪżŁżļżĶż”ż╦ż╩żļĪŻ└@├ōżŪżóżĻż╩ż¼żķźūźĒź░źķźÓ▓─ē”ż╩╣ŌÅ]ź©ź¾źĖź¾ż╚ż╩żļĪŻż│ż╬╣ŌĄķż╩╚ŠŲ│öüż“│½╚»żĘż┐ż╬żŽĪóżŌżŽżõFPGAż╬▓±╝ężŪżŽż╩ż»ĪóźŪĪ╝ź┐Ū·╚»ż╦×┤▒■żŪżŁżļ▓±╝ęż“╗žĖ■ż╣żļż┐żßż└Īóż╚║ŻŃQż╬żŽżĖżßż╦CEOż╦┼×ŪżżĘż┐Victor PengĢ■(┐▐1)żŽĮęż┘ż┐ĪŻ

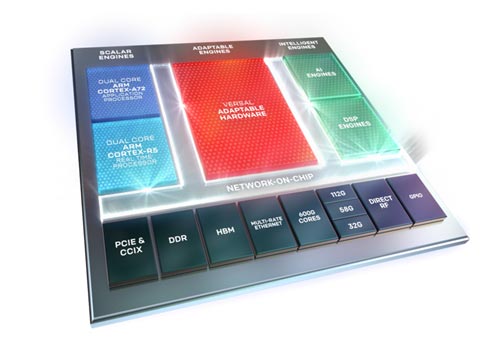

─¾░ŲżĄżņż┐ACAPż╦ĮĖ└迥żņżļövŽ®źųźĒź├ź»Ī╩┐▐2Ī╦ż“Šę▓żĘżĶż”ĪŻĮjżŁż╩źųźĒź├ź»żŽ4ż─żóżļĪŻ▐kż─żŽź╣ź½źķĪ╝ĮĶ═²ź©ź¾źĖź¾ż╚Ō}żųĪóżżż’żµżļCPUżŪżóżļĪŻż│ż│ż╦żŽArm Cortex-A72źóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╚ĪóArm Cortex-R5źĻźóźļź┐źżźÓź│ź¾ź╚źĒĪ╝źķż“┼ļ║▄żĘżŲżżżļĪŻżżż’żąźĮźšź╚ź”ź©źóźūźĒź░źķź▀ź¾ź░żŪź½ź╣ź┐ź▐źżź║ż╣żļĪóżõżõ╣ŌĄķż╩CPUżŪżóżļĪŻż│ż╬LSIµ£öüż“öUĖµż╣żļövŽ®ż¼Cortex-R5żŪżóżļĪŻ

┐▐2ĪĪXilinxż¼─¾░ŲżĘż┐2.5D-ICż╬ACAPĪĪĮąųZĪ¦Xilinx

żĮżĘżŲĪóVARSALż╚Ō}żų┼¼├ōĘ┐źŽĪ╝ź╔ź”ź©źóź©ź¾źĖź¾żŽĪó└ņ├ōż╬▒ķōQövŽ®ż“║Ņżļż┐żßż╬źŽĪ╝ź╔ź”ź©źóövŽ®żŪżóżļĪŻż│ż│żŽFPGAż“┤╦▄ż╚ż╣żļ└ņ├ōIPövŽ®żŪżóżļż¼Īó║ŪĮj3Ė─ż╬└ņ├ōövŽ®ż“═ĮżßFPGAżŪ╣Į└«żĘżŲż¬żŁĪóŲ░║Ņ├µż╦żĮż╬└ņ├ōövŽ®ż“└┌żĻü÷ż©żļż│ż╚żŪź└źżź╩ź▀ź├ź»ż╩║Ų╣Į└«övŽ®ż“╝┬ĖĮż╣żļż╚żżż”Ślż└ĪŻż│ż╬IPżŽĪóŠ«żĄż╩ĄĪ│Ż│žØ{ż╬źóźūźĻź▒Ī╝źĘźńź¾żõ║ŲŠW├ō▓─ē”ż╩źĒźĖź├ź»ż╩ż╔ż“ź┐źżźÓźĘź¦źóźĻź¾ź░ż╬żĶż”ż╦Įń╝Ī└┌żĻü÷ż©żŲżżż»ĪŻŠņĀCż╦▒■żĖżŲźóź└źūźŲźŻźųż╦└┌żĻü÷ż©żņżążĶżżż┐żßĪóźóź└źūźŲźŻźųĪ╩┼¼▒■Ę┐Ī╦źŽĪ╝ź╔ź”ź©źóź©ź¾źĖź¾ż╚Ō}ż¾żŪżżżļĪŻż┴ż╩ż▀ż╦VARSALż╚żżż”Ō}żėć@żŽĪó¾H══└Łż“┴T╠Żż╣żļVersatileż╚└@├ō└Łż“┴T╠Żż╣żļUniversalż“╣ńż’ż╗ż┐ļ]ĖņżŪżóżļĪŻ

įÆż─ų`ż¼DSPĪ╩źŪźĖź┐źļ┐«ęÄĮĶ═²Ī╦ź©ź¾źĖź¾żŪżóżļĪŻDSPżŽĪó└čŽ┬▒ķōQ└ņ├ōż╬ź▐źżź»źĒźūźĒź╗ź├źĄż└ż¼Īó╣Ō┼┘ż╩źŌźŪźļż“┐¶├═▒ķōQż╣żļż╬ż╦╗╚ż”ż│ż╚ż¼¾HżżĪŻ─╠┐«┤├ŽČ╔ż╬źŌźŪźÓż╬źóźļź┤źĻź║źÓż“╝ŖōQżĘż┐żĻĪóśO╩¼└ņ├ōż╦æ]ż┴╬®żŲż┐źŌźŪźļż“╝ŖōQżĘż┐żĻż╣żļż┐żßĪó32źėź├ź╚Ī╩├▒╗@┼┘Ī╦ż╩żżżĘ64źėź├ź╚Ī╩Ū▄╗@┼┘Ī╦ż╬żĶż”ż╦╗@┼┘ż╬╣Ōżż╔ŌŲ░Š«┐¶┼└▒ķōQż¼▓─ē”żŪżóżļż└ż▒żŪżŽż╩ż»Īóź½ź╣ź┐ź▐źżź║żĄżņż┐źŪĪ╝ź┐źčź╣ż“─ŃżżźņźżźŲź¾źĘżŪŠĢ┼┘ż╬║┘ż½żżöUĖµż¼▓─ē”ż└ż╚żĘżŲżżżļĪŻ

╗═ż─ų`ż¼┐õéb└ņ├ōż╬AIź©ź¾źĖź¾żŪżóżļĪŻAIż╬┐õébż╚╣Ō┼┘ż╩┐«ęÄĮĶ═²ż╦Ė■żżż┐Īó╣Ōź╣źļĪ╝źūź├ź╚żŪ─ŃźņźżźŲź¾źĘĪó╣Ōżż┼┼╬üĖ·╬©ż“ØŖ─╣ż╚żĘżŲżżżļĪŻXilinxżŽźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╬┐õébźūźķź├ź╚źšź®Ī╝źÓż“Š}²Xż▒żŲżżżļ├µ╣±Deephi╝ęż“║ŻŃQż╬7ĘŅż╦āA╝²żĘżŲż¬żĻĪóXilinxżŽāA╝²░╩Øiż½żķż│ż╬ź╣ź┐Ī╝ź╚źóź├źū(2016ŃQ└▀╬®)ż╦Įą½@żĘżŲżżż┐ĪŻżĘż½żŌDeephiżŽ┐õébźóź»ź╗źķźņĪ╝ź┐ż“FPGAżŪ╝┬äóżĘżŲżżż┐ż╬żŪĪó┐ʿʿżACAPż╦żŌśO─śż╦ŲDżĻ╣■żÓż│ż╚ż¼żŪżŁż┐ĪŻCaffeżõTensorFlowż╩ż╔ż╬źšźņĪ╝źÓź’Ī╝ź»żŪ│žØ{żĘż┐źŪĪ╝ź┐ż“ż│ż╬AIź©ź¾źĖź¾żŪź│ź¾źčźżźļżĘżŲSoCż╦╝┬äóżŪżŁżļĪŻ

AIź©ź¾źĖź¾żŽĪó╩┬š`ĮĶ═²ż╣żļŠņ╣ńż╦żŽSIMDĪ╩Single Instruction Multiple DataĪ╦╠┐╬ßżŪ╣įš`▒ķōQż“╣įżżĪóVLIW╠┐╬ßżŪź╣ź▒źĖźÕĪ╝źĻź¾ź░öUĖµż╣żļĪŻAIź©ź¾źĖź¾ŲŌż╬ĘQ¹|ź┘ź»ź╚źļźūźĒź╗ź├źĄź│źóżŽźßźŌźĻż╚ź╗ź├ź╚ż╦ż╩ż├żŲż¬żĻ(┐▐3)ĪóĄĪ│Ż│žØ{żŪżŽż│ż╬Š«żĄż╩ź┘ź»ź╚źļźūźĒź╗ź├źĄż╚źßźŌźĻż╬×┤ż╬övŽ®żŪ╣Į└«żĄżņĪó«Ć╩┬š`żŪ▒ķōQżĘżŲżżż»ĪŻ

┐▐3ĪĪĮĖ└čżĘż┐AIź©ź¾źĖź¾ż╬IPź│źóĪĪĮąųZĪ¦Xilinx

╝■╩šövŽ®ż╚żĘżŲĪóźżź¾ź┐źšź¦Ī╝ź╣żŪżŽPCIeż╬Gen4Ī▀16żõĪóAXI-DMAż╩ż╔ż“┼ļ║▄żĘżŲżżżļĪŻźßźŌźĻż╚żĘżŲżŽDDR4-3200żõLPDDR4-4266ż╩ż╔ż╬DRAMżõĪóDRAMźóźņźżź┴ź├źūż“3╝ĪĖĄICż╚żĘżŲ└▄¶öżĄżņż┐HBMĪ╩High Bandwidth MemoryĪ╦ż“┼ļ║▄żŪżŁżļĪŻżĄżķż╦100Gbpsż╬ź▐źļź┴źņĪ╝ź╚ż╬źżĪ╝źĄź═ź├ź╚żõ░┼ęÄ▓Įź©ź¾źĖź¾żŌ┼ļ║▄żŪżŁżļĪŻżŌż┴żĒż¾Īó32Gbpsż╩żżżĘ58Gbpsż╬╣ŌÅ]źżź¾ź┐źšź¦Ī╝ź╣PAM4żŌ├ō┴Tż╣żļĪŻ║Ū╣ŌÅ]ż╬112GbpsżŌ├ō┴Tż╣żļż¼ż│żņżŽ7nmźūźĒź╗ź╣żŪ╝┬ĖĮż╣żļ═Į─Ļż╚ż╩ż├żŲżżżļĪŻ

żĄżķż╦Īó║ŻĖÕż╬5Gź’źżźõźņź╣─╠┐«Ė■ż▒ż╬źŌźŪźÓżõ╝Ī└ż┬ÕGPSĖ■ż▒ż╬RF-ADC/DACĪóźŪźĖź┐źļźóź├źūź│ź¾źąĪ╝ź┐ż╚ź└ź”ź¾ź│ź¾źąĪ╝ź┐żŌŲŌē┼żĘż┐RFźĘź░ź╩źļź┴ź¦Ī╝ź¾IPżŌØŹ×óż╣żļĪŻżĮżĘżŲĪóĘQövŽ®źųźĒź├ź»ż“ż─ż╩ż░Ū█└■żŽźąź╣öĄ╝░żŪżŽż╩ż»Īóź╣źżź├ź┴żŪ└┌żĻü÷ż©żļżĶż”ż╩NoCĪ╩Network on ChipĪ╦öĄ╝░ż“ŲDżļĪŻż│ż╬NoCż╬IPżŽŲ╚śOż╦│½╚»żĘż┐żŌż╬ĪŻ├▒ż╩żļźĻźįĪ╝ź┐ż“┤▐żÓż╬żŪżŽż╩ż»ĪóźžźŲźĒż╩ź©ź¾źĖź¾µ£öüż╬źóĪ╝źėź╚źņĪ╝źĘźńź¾Ī╩źŪĪ╝ź┐Ēö╣ńż“┼D═²ż╣żļ╗┼┴╚ż▀Ī╦ż¼▓─ē”ż╩╣Įļ]ż╦ż╩ż├żŲżżżļĪŻ

║ŪŠ«Øó╦Ī7nmźūźĒź╗ź╣żŪ×æļ]ż╣żļż│ż╬ACAPżŽĪó║Ū╣ŌĄķż╬övŽ®ż“ĮĖ└čżĘżŲż¬żĻĪóĖ▄Ąęż╬═ūĄßż╦▒■żĖżŲövŽ®ż“└┌żĻ╩¼ż▒Ī󿥿ķż╦║ŲŠW├ōżŪżŁżļźšź®Ī╝ź▐ź├ź╚ż“ŲDżļĪŻ