SamsungĪóDRAMźóźņźżż“12ĮŚTSVżŪ└č┴žĪó24GBż╬HBMż“ż▐żŌż╩ż»╬╠ŠÅżž

SamsungżŽĪó12ĮŚż╬DRAMźóźņźżź┴ź├źūż“└č┴žżĘĪóTSVĪ╩Through Silicon ViaĪ╦żŪ└▄¶öżĘż┐24GBż╬HBMźŪźąźżź╣ż“│½╚»Ī󟎟żź©ź¾ź╔▌xŠņĖ■ż▒ż╦ż▐żŌż╩ż»╬╠ŠÅż╣żļż╚╚»╔ĮżĘż┐ĪŻTSVżŪĘĻż“żóż▒ż┐┴Ē┐¶żŽ6╦³Ė─░╩æųż╦├Żż╣żļż╚żĘżŲżżżļĪŻ

┐▐1ĪĪSamsungż¼│½╚»żĘż┐HBMźßźŌźĻżŽ12ĮŚż“TSVżŪ└▄¶öĪĪĮąųZĪ¦Samsung

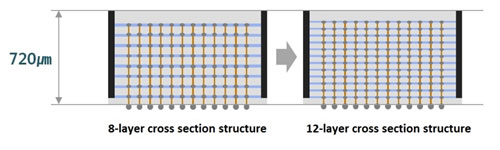

ż│żņż▐żŪżŽ8ĮŚż╬DRAMź┴ź├źūż“TSVżŪż─ż╩żżż└HBM2×æē俎żóż├ż┐ż¼Īó12ĮŚżŽż│żņż¼ĮķżßżŲż╚żżż”ĪŻ12ĮŚ─_ż═żŲźŌĪ╝źļź╔żŪźčź├ź▒Ī╝źĖź¾ź░żĘżŲżŌźčź├ź▒Ī╝źĖż╬Ė³żĄżŽĪó“£═Ķż╬8ĮŚ╣Į└«ż╚Ų▒żĖ720µmż╦ż╚ż╔żßż┐(┐▐1)ĪŻ╬╠ŠÅ├µż╬HBM2×æē俎1ĮŚż¼8Gźėź├ź╚ż╬źßźŌźĻ═Ų╬╠żŪ8ĮŚ─_ż═ż┐8GBż└ż├ż┐ż¼Īó║Żöv│½╚»żĘż┐HBMżŽ1ĮŚż¼16Gźėź├ź╚ż╬źßźŌźĻżŪ12ĮŚ─_ż═żŲ24GBż╚ż╩żļĪŻ

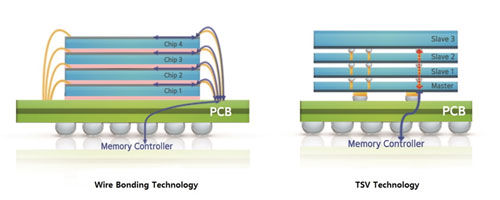

ż│ż╬źßźŌźĻź╗źļźóźņźżżŽĪó║Ū▓╝┴žż╬źóźņźżż“ĘążŲĪóźūźĻź¾ź╚övŽ®┤łż╬╬óŖõż╦╝┬äóż╣żļźßźŌźĻź│ź¾ź╚źĒĪ╝źķż╦ż─ż╩ż░(┐▐2)ĪŻź’źżźõź▄ź¾ź╔żŪ└▄¶öż╣żļŠņ╣ńż╦╚µż┘ĪóŪ█└■ĘąŽ®ż¼ż░ż¾ż╚ø]ż»ż╩żĻźßźŌźĻżŽ╣ŌÅ]ż╦źóź»ź╗ź╣żŪżŁżļżĶż”ż╦ż╩żļĪŻźßźŌźĻźóźņźżżžż╬źóź»ź╗ź╣żŽź│ź¾ź╚źĒĪ╝źķż“─╠żĘżŲ╣įż”ĪŻ

┐▐2ĪĪDRAMź╗źļźóźņźżż“12ĮŚ└č┴žżĘźóź»ź╗ź╣żŽźūźĻź¾ź╚╚Ūż╬╬óĀCż╦└▀ż▒ż┐źßźŌźĻź│ź¾ź╚źĒĪ╝źķż½żķ╣įż”ĪĪĮąųZĪ¦Samsung

SamsungżŽźßźŌźĻżŪżŽżŌżŽżõźÓĪ╝źóż╬╦Īō¦ż¼└«żĻ╬®ż┐ż║Īó3DżŪĮĖ└č┼┘ż“æųż▓żļżĘż½ż╩żżż╚żĘżŲĪó3D-TSVČ\Įčż╦żĶżļDRAM│½╚»ż“┐╩żßżŲżżżļĪŻHBMöĄ╝░żŽźßźŌźĻ═Ų╬╠ż╚źóź»ź╗ź╣ż╣żļźąź¾ź╔╔²ż“╣Łż▓żļż╚żżż”Ų¾ż─ż╬Ė·▓╠ż¼żóżĻĪóż│żņż½żķż╬DRAMżŽHBMöĄ╝░ż╦Ė■ż½ż”żĶż”ż└ĪŻż▐ż║żŽźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż“├µ┐┤ż╚ż╣żļHPCĪ╩High Performance ComputingĪ╦ż╚AIźūźĒź╗ź├źĄ╝■żĻż╬źŽźżź©ź¾ź╔├ō²ŗż╦HBMż“╗╚ż”ĪŻż┐ż└żĘĪóSamsungżŽHBM2.5ż╩ż╬ż½HBM3ż╩ż╬ż½Īó£½żķż½ż╦żĘżŲżżż╩żżĪŻ

HBMżŪżŽźßźŌźĻź│ź¾ź╚źĒĪ╝źķż¼ź½ź«ż“É█żļĪŻHBMż╬źßźŌźĻź│ź¾ź╚źĒĪ╝źķż“└▀╝ŖżĘżŲżżżļźšźĪźųźņź╣ż╬Northwest Logicż“Rambusż¼āA╝²żĘżŲŠ}ż╦Ų■żņĪóHBMż“Rambusż¼╚╬ŪõżŪżŁżļżĶż”ż╦ż╩ż├ż┐ĪŻRambusżŽNorthwestż╬źßźŌźĻź│ź¾ź╚źĒĪ╝źķż“└▀╝ŖżĘĪó×æļ]żŽSamsungż╩ż╬ż½TSMCż╩ż╬ż½ĪóRambusż╬┴TĖ■ż╦ż½ż½ż├żŲżżżļĪŻ

╗▓╣═½@╬┴

1. Samsung Electronics Develops IndustryĪŪs First 12-Layer 3D-TSV Chip Packaging Technology