LatticeĪóź╗źŁźÕźĻźŲźŻĄĪē”ż“FPGAż╦│╩Ū╝ĪóźņźĖźĻź©ź¾ź╣ĄĪē”ż“┴╚ż▀╣■żÓ

├µŠ«Ę┐FPGA×æēäżŪĪóø]┤³ż╬│½╚»ż“┐õ┐╩żĘżŲżżżļLattice SemiconductorżŽĪóź╗źŁźÕźĻźŲźŻż“äė▓Įż╣żļźĮźĻźÕĪ╝źĘźńź¾ż“─¾ČĪż╣żļĪŻFPGAĪ╩×æēäć@MACH XO3DĪ╦żõżĮżņż“╗╚ż├ż┐źĘź╣źŲźÓżĮż╬żŌż╬ż“ź╗źŁźÕźóż╦ż╣żļ×æēäĪųSentryźĮźšź╚ź”ź©źóź╣ź┐ź├ź»Īūż╚ĪóĮą▓┘ż╣żļ╗■ż½żķźŪźąźżź╣żõźĘź╣źŲźÓż“ź╗źŁźÕźóż╦╝ķżļźĮźšź╚ź”ź©źó×æēäĪųSupplyGuardĪūż“źĻźĻĪ╝ź╣żĘż┐ĪŻż│żņżķżŽFPGA×æēäż╦┴╚ż▀╣■żÓĪŻ

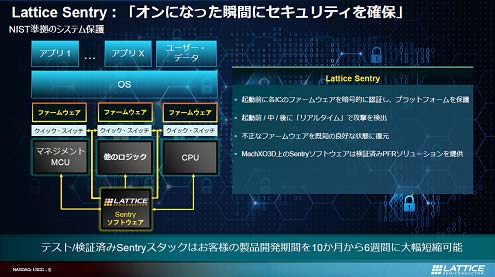

┐▐1ĪĪźĘź╣źŲźÓż“ź╗źŁźÕźóż╦ż╣żļFPGAż╦┼ļ║▄ż╣żļźĮźšź╚ź”ź©źóSentryĪĪĮąųZĪ¦Lattice Semiconductor

FPGAź┘ź¾ź└Ī╝żŽż│żņż▐żŪĪóźūźĒź░źķźÓżõĖĪŠ┌ż╬żĘżõż╣żĄż“─_£åżĘż┐│½╚»ź─Ī╝źļż“źĻźĻĪ╝ź╣żĘżŲżŁż┐ż¼ĪóLatticeżŽź╗źŁźÕźĻźŲźŻäė▓Įż╦żŌFPGAż¼Ń~Ė·żŪżóżļż│ż╚ż“┐āżĘż┐ĪŻŲ▒╝ęż╬LUTĪ╩Look-Up Table: ╝ń═ūż╩éb═²övŽ®ż“ĮĖżßż┐┤╦▄źųźĒź├ź»Ī╦ż╦╗╚ż’żņżŲżżżļźĒźĖź├ź»źŪźąźżź╣ż╬▐kż─MACH XO3DżŽĪó╔įĦ╚»└ŁźßźŌźĻź╣źżź├ź┴ż“┤╦▄ż╚żĘżŲż¬żĻĪóĮjżŁż╩ĀC└čż“žéżßżļSRAMżŪżŽż╩żżż┐żß2.5mm│čż╬WLCSPĪ╩Wafer-Level Chip Scale PackageĪ╦źčź├ź▒Ī╝źĖż╦║ŪĮj9400Ė─ż╬LUTż“ĮĖ└čżĘżŲżżżļĪŻ

ż│ż╬SentryźĮźšź╚ź”ź©źóź╣ź┐ź├ź»żŽĪóŲ▒╝ęż╬FPGA×æēäMACH XO3Dż╬├µż╦źūźĒź░źķźÓżĘżŲż¬żŁĪóźĘź╣źŲźÓż╬┼┼Ė╗ż“ź¬ź¾żĘźĘź╣źŲźÓż¼Ą░╠OżĘ╗Žżßżļż╚Ų▒╗■ż╦ż│ż╬FPGAż¼źĘź╣źŲźÓż“ź╗źŁźÕźóż╦ż╣żļĪ╩┐▐1Ī╦ĪŻFPGA×æēäż╬├µż╦ź╗źŁźÕźĻźŲźŻĄĪē”ż“┴╚ż▀╣■ż¾żŪżóżļż┐żßĪóźĘź╣źŲźÓŲŌż╬CPUżõöUĖµ├ōMCUĪóżĮż╬┬Šż╬źĒźĖź├ź»ż╩ż╔ĘQICż╬źšźĪĪ╝źÓź”ź©źóż╬░┼ęÄ▓ĮŠ╩¾ż“Ū¦Š┌żĘżŲżżż»ĪŻżĄżķż╦ĪóźĘź╣źŲźÓż¼ŲłĘŌżĄżņż┐żķźĻźóźļź┐źżźÓżŪżĮżņż“ĖĪĮąż╣żļĄĪē”żŌżóżļĪŻ▓├ż©żŲĪó╔į┘ćż╩źšźĪĪ╝źÓź”ź©źóż“┘Jē¶ż╬╬╔╣źż╩ėX▌åż╦╔³ĖĄż╣żļPFRĪ╩Platform Firmware ResilienceĪ╦ĄĪē”żŌżóżļĪŻ

ż│ż╬FPGAż╦żŽĪóźĘź╣źŲźÓż╬ÅŚŲ░╗■ż╦żĮżņż“ź╗źŁźÕźóż╦╝ķżļ╩▌ĖŅövŽ®ż╚żŌżżż”ż┘żŁRoTĪ╩Root of TrustĪ╦żõĪóNISTØŹĄ“ż╬░┼ęÄ▓ĮövŽ®ż“źūźĒź░źķźÓżĄżņżŲżżżļĪŻRoTżŽĪóźĘź╣źŲźÓż╬ÅŚŲ░╗■ż╦źšźĪĪ╝źÓź”ź©źóż╬┐«═Ļ└Łż¼│╬╩▌żĄżņżŲżżżļż½ż╔ż”ż½ż“▒R─ĻżĘ│╬Ū¦Īó╩▌┘TĪó─╠ē¶ż╣żļ╠“│õż“Ęeż─ĪŻźčźĮź│ź¾ż╬BIOSż╦ŖZżżĪŻż│żņżķż╬▒■┼·żŽnsĪ╩ź╩ź╬╔├Ī╦├▒░╠żŪ╣įż©żļż┐żßĪóźĘź╣źŲźÓż╬ÅŚŲ░żŽČ╦żßżŲÅ]żżż╚żżż©żĮż”ż└ĪŻ

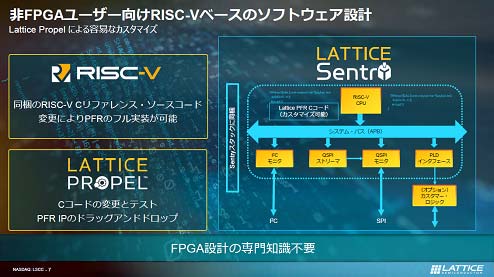

PFRövŽ®ż╬IPż“FPGAż╦┴╚ż▀╣■żÓż┐żßż╬źĮźšź╚ź”ź©źóź─Ī╝źļż╚żĘżŲ┘J┘Tż╬Lattice Propelż“╗╚ż©żąĪóCź│Ī╝ź╔żŪź½ź╣ź┐ź▐źżź║żŌżŪżŁżļĪŻRISC-Vź│źóżŌĮĖ└迥żņżŲż¬żĻĪóż│ż╬CPUż“─╠żĘżŲNIST SP 800-193ØŹĄ“ż╬PFRĪĪĪ╩┐▐2Ī╦ĄĪē”żŌCĖ└ĖņżŪ╝┬äóżŪżŁżļĪŻRISC-Vź│źóż“ĮĖ└čżĘż┐ż╬żŽĪóź╗źŁźÕźĻźŲźŻĄĪē”ż“│╬Ū¦Īó╩▌┘TĪó─╠ē¶ż╩ż╔ż╬źĘĪ╝ź▒ź¾ź╣ż╬öUĖµżõ┤╔═²ż“╣įż”ż┐żßż└ż╚żżż”ĪŻŪ¦Š┌ż“żŽżĖżßż╚ż╣żļź╗źŁźÕźóĄĪē”żŽFPGAźĒźĖź├ź»ż╦źūźĒź░źķźÓż╣żļĪŻź╗źŁźÕźĻźŲźŻövŽ®ż╬źĄźżź║żŽ6700Ė─ż╬LUTż╦┴Ļ┼÷ż╣żļż┐żßĪóMAX XO3DźšźĪź▀źĻż╬├µżŪżŌźĒźĖź├ź»źĄźżź║ż╬ĮjżŁż╩║ŪĮj9400LUTż“Ęeż─×æēäż¼Ė■ż»ĪŻ

┐▐2ĪĪż│żņż▐żŪFPGAż“źūźĒź░źķźÓżĘż┐ż│ż╚ż╬ż╩żżźµĪ╝źČĪ╝żŪżŌCĖ└ĖņżŪRISC-Vź│źóż“─╠żĘżŲFPGAż╦źūźĒź░źķźÓż╣żļż│ż╚ż¼żŪżŁżļĪĪĮąųZĪ¦Lattice Semiconductor

żŌż”▐kż─ĪóFPGAż“Įą▓┘żĘżŲż½żķĖÕż╦FPGAż“ź▄Ī╝ź╔ż╦┴╚ż▀Īó░┼ęÄ▓ĮĮĶ═²żõĮć@ż“Į¬ż©żŲż½żķźĘź╣źŲźÓż╦┴╚ż▀╣■ż▀Īó┤░└«żĄż╗żļż▐żŪż╬źĄźūźķźżź┴ź¦Ī╝ź¾µ£öüż╦┼ŽżĻźŪźąźżź╣ż“╝{└ūżŪżŁĪóĄČļ]żõ╩Ż×æż╩ż╔ż╬╩▌ĖŅż“╣įż”ĄĪē”ż“Ęeż─źĮźšź╚ź”ź©źóż¼SupplyGuardż└Ī╩┐▐3Ī╦ĪŻżżż’żąźĄźūźķźżź┴ź¦Ī╝ź¾ż╬źņźĖźĻź©ź¾ź╣ż╬ż┐żßż╬╩▌ĖŅźĄĪ╝źėź╣ż╚żżż©żļĪŻ╬╠ŠÅ╣®Šņż½żķĮą▓┘ĖÕż╦źĘź╣źŲźÓż╬└▀ÅøĪó▒┐├ōĪóŪč┤■ż▐żŪż╬źķźżźšźĄźżź»źļµ£öüż╦┼Žż├żŲżŌĄĪē”ż╣żļĪŻ

┐▐3ĪĪĮą▓┘ĖÕż╬źĘź╣źŲźÓż╬ź╗źŁźÕźĻźŲźŻż“┤╔═²ż╣żļSupplyGuardĪĪĮąųZĪ¦Lattice Semiconductor

ż│żņżķŲ¾ż─ż╬źĮźšź╚ź”ź©źóż“ĪóFPGAźŽĪ╝ź╔ź”ź©źóż╦┴╚ż▀╣■żÓż│ż╚żŪĪóź└źżź╩ź▀ź├ź»ż╩ź╚źķź╣ź╚ż“ų`╗žż╣ż╚żĘżŲżżżļĪŻ▒┐├ōż╬²ŗ├µżŪ│░ŗż½żķŲłĘŌżĄżņżŲżŌĮų╗■ż╦ĖĪĮążĘ×┤▒■ż╣żļż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩żļĪŻżĮżņżŽź▐źżź│ź¾ź┘Ī╝ź╣żŪż╬ź╣ź┐źŲźŻź├ź»ż╩ź╗źŁźÕźĻźŲźŻżŪżŽż╩ż»Īó╣ŌÅ]×┤▒■▓─ē”ż╩FPGAżŪż╬ź└źżź╩ź▀ź├ź»ż╩NISTØŹĄ“ż╬PFRż¼╔nŲ»ż╣żļż│ż╚ż“┴T╠ŻżĘżŲżżżļĪŻ