IntelĪóŗī3└ż┬Õż╬Xeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄż“źĮźĻźÕĪ╝źĘźńź¾─¾ČĪ

IntelżŽĪó║ŪĮj40CPUź│źóż“ĮĖ└čżĘż┐ŗī3└ż┬Õż╬Xeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄż“╚»╔ĮżĘż┐Ī╩┐▐1Ī╦ĪŻź»źķź”ź╔żõźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ĪóHPCż╩ż╔ż╦Ė■ż▒ż┐źŽźżź©ź¾ź╔źūźĒź╗ź├źĄż└ĪŻØi└ż┬Õż╬XeonźūźĒź╗ź├źĄż╚╚µż┘żŲ║ŪĮj1.46Ū▄ż╬└Łē”Ė■æųż└ż╚żĘżŲżżżļĪŻżõżŽżĻ1.74Ū▄ż╬┐õéb▒ķōQż“Ęeż─AIĪ╩źŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░Ī╦└ņ├ōż╬źūźĒź╗ź├źĄż“ĮĖ└čżĘĪ󿥿ķż╦źßźŌźĻ╩▌ĖŅżõ░┼ęÄ▓Įźóź»ź╗źķźņĪ╝ź┐ż“ĮĖ└čĪóź╗źŁźÕźĻźŲźŻż“äė▓ĮżĘż┐ż│ż╚ż¼ź┴ź├źūż╬ØŖ─╣ĪŻ

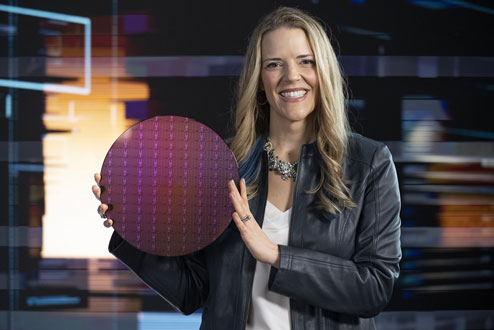

┐▐1ĪĪIntelż¼│½╚»żĘż┐ŗī3└ż┬Õż╬Xeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄĪĪźĘźĻź│ź¾ź”ź¦Ī╝źŽż“Ęeż├żŲżżżļż╬żŽIntel╝ęźŪĪ╝ź┐źūźķź├ź╚źšź®Ī╝źÓź░źļĪ╝źūĪĪXeon/źßźŌźĻź░źļĪ╝źūżŪź│Ī╝ź▌źņĪ╝ź╚VPż╬Lisa SpelmanĢ■ĪĪĮąųZĪ¦Intel Corp.

ż│żņż▐żŪżŌIntelżŽĪ󟎟żź©ź¾ź╔ż╬CPUżŪżóżļXeonźūźĒź╗ź├źĄż“źĄĪ╝źąĖ■ż▒ż╦Įj╬╠ż╦Įą▓┘żĘżŲżŁż┐ĪŻż│ż╬CPUż“źĄĪ╝źąż╦┼ļ║▄żĘż┐ź»źķź”ź╔źūźĒźąźżź└żŽ800╝ęż“«Ćż©żļż╚żĘżŲżżżļĪŻCPUź│źó┐¶żŪĖ└ż©żąĪó2013ŃQ░╩═ĶĪó╩Å╝ŖżŪ10▓»Ė─ż╦żŌæųżļż╚żżż”ĪŻżĄżķż╦Īóź┴ź├źūż“╩┬š`└▄¶öżĘżŲ│╚─ź└Łż“└▀ż▒żķżņżļź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄżŽĪó╩Å╝ŖżŪ5000╦³Ė─░╩æųĮą▓┘żĘżŲżŁż┐ĪŻ

║ŻövĪóźūźĒź╗ź├źĄż└ż▒żŪżŽż╩ż»ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŪż╬ź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż╦ØŁ═ūż╩FGPAż╬Agilex┐Ę×æēäżõ3¹|╬Óż╬źßźŌźĻ┐Ę×æēäĪ╩Å]┼┘ż╬Įńż½żķĪóOptaneźčĪ╝źĘź╣źŲź¾ź╚źßźŌźĻ200źĘźĻĪ╝ź║ĪóOptane SSDż╬P5800XĪó144┴žQLC NANDźšźķź├źĘźÕż╬ź╣ź╚źņĪ╝źĖSSDĪ╦ĪóżĮżĘżŲ│░ŗż╚ż╬─╠┐«źżź¾ź┐Ī╝źšź¦Ī╝ź╣żŪżóżļPCIe 4.0żŪ200GbEż╬źżĪ╝źĄź═ź├ź╚ź┴ź├źū┐Ę×æēäE810-2CQDA2żŌĪóź┴ź├źūź╗ź├ź╚ż╚żĘżŲ├ō┴TżĘĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒źĮźĻźÕĪ╝źĘźńź¾ż╚żĘżŲ─¾ČĪż╣żļĪ╩┐▐2Ī╦ĪŻż│żņż╦żĶż├żŲĪóźĘź╣źŲźÓźņź┘źļżŪż╬źĮźšź╚ź”ź©źóż“║Ū┼¼▓ĮżŪżŁżļż╚żĘżŲżżżļĪŻ

┐▐2ĪĪIntelżŽ┐Ę×æēäXeonż╦▓├ż©żŲFPGAż╚źßźŌźĻĪóź╣ź╚źņĪ╝źĖĪó─╠┐«Ethernetź┴ź├źūżŌź┴ź├źūź╗ź├ź╚ż╚żĘżŲźĮźĻźÕĪ╝źĘźńź¾─¾ČĪż╣żļĪĪĮąųZĪ¦Intel Corp.

ż│ż╬ŗī3└ż┬ÕXeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄĪ╩ź│Ī╝ź╔ć@Ice LakeĪ╦żŽĪó║ŪĮķż╬10nmźūźĒź╗ź╣ż“▓■╬╔żĘż┐żŌż╬ż└ż╚żĘżŲżżżļĪŻż┐ż└żĘĪóŗī11└ż┬ÕCoreźūźĒź╗ź├źĄżŪ╗╚ż’żņż┐SuperFinFETČ\ĮčĪ╩╗▓╣═½@╬┴1Ī╦żŽ╗╚ż├żŲżżż╩żżż╚żżż”ĪŻż▐ż┐Č\Įč┼¬ż╦└Łē”ż“æųż▓żķżņż┐ż╬żŽĪóSunny Coveż╚ć@¤²ż▒żķżņż┐CPUź│źóż╬ź▐źżź»źĒźóĪ╝źŁźŲź»ź┴źŃż“▓■╬╔żĘż┐ż│ż╚ż╦żĶżļĪŻ╬Ńż©żąĪóźóź”ź╚ź¬źųź¬Ī╝ź└Ī╝╝┬╣į╠┐╬ßż╬šJ░Žż““£═Ķż╬224Ė─ż½żķ532Ė─ż╦╗\żõżĘż┐żĻĪóźņźĖź╣ź┐źšźĪźżźļ┐¶ż“┼D┐¶ż╚Š«┐¶┼└▒ķōQżŪČ”ż╦╗\żõżĘż┐żĻżĘż┐ż╩ż╔ż¼żóżļĪŻ

AI└ņ├ōż╬źūźĒź╗ź├źĄżĮż╬żŌż╬żŽĪóŗī2└ż┬Õż╬8280Ī╩ź│Ī╝ź╔ć@Cascade LaceĪ╦ż╚╚µż┘ż┐└Łē”ż“╚»╔ĮżĘżŲżżżļĪŻ▓ĶćĄŪ¦╝▒Mobilenet-v1ż└ż╚źĻźóźļź┐źżźÓ┐õébżŪ1.59Ū▄Īóźąź├ź┴┐õébżŪ1.66Ū▄Īó▓ĶćĄ╩¼╬Óż╬ResNet-50-v1.5żŪżŽżĮżņżŠżņ1.52Ū▄Īó1.56Ū▄Ī󿥿ķż╦śO─śĖ└ĖņĮĶ═²ż╬BERT-largeżŪżŽżĮżņżŠżņ1.45Ū▄Īó1.74Ū▄ż╚ĮĶ═²╗■┤ųż¼╣ŌÅ]▓ĮżĘż┐Ī╩┐▐3Ī╦ĪŻż┐ż└żĘĪóŲŌŗ╣Įļ]ż╦┤žżĘżŲżŽ£½żķż½ż╦żĘżŲżżż╩żżĪŻ

┐▐3ĪĪAI└ņ├ōźūźĒź╗ź├źĄż╬└Łē”żŌæųż▓ż┐ĪĪĮąųZĪ¦Intel Corp.

3╚ųų`ż╬ØŖ─╣żŪżóżļź╗źŁźÕźĻźŲźŻż╬äė▓Įż╦┤žżĘżŲżŽĪó3ż─ż╬Č\Įčż“Ų│Ų■żĘż┐ĪŻ1ż─żŽĪóSGXĪ╩źĮźšź╚ź”ź©źóź¼Ī╝ź╔ź©ź»ź╣źŲź¾źĘźńź¾ź║Ī╦ż╚Ō}żųĄĪē”żŪĪóOSżõVMĪ╩▓Š„[ź▐źĘź¾Ī╦ź▐ź═Ī╝źĖźŃĪ╝ż╬└╚╝Õ└Łż“ż─ż½żņżŲżŌźóźūźĻź▒Ī╝źĘźńź¾źŪĪ╝ź┐ż“╝ķżĻĪóźĮźšź╚ź”ź©źóżžż╬ŲłĘŌż╦×┤ż╣żļ╦╔Ėµż¼żŪżŁżļĪŻż▐ż┐Īó2ż─ų`żŽĪóźßźŌźĻōļ░Ķµ£öüż“░┼ęÄ▓Įż╣żļż│ż╚żŪĪóż┐ż╚ż©ŲłĘŌżĄżņżŲżŌźŪĪ╝ź┐ż“Ų╔żßż╩ż»ż╣żļ╩▌ĖŅż“└▀ż▒ż┐ĪŻ3ż─ų`żŽ░┼ęÄ▓Įż╚▓“Ų╔▓Įż╣żļż┐żßż╬źóź»ź╗źķźņĪ╝źĘźńź¾▒ķōQ╠┐╬ßż“CPUź│źóż╦└▀ż▒ż┐ż│ż╚ż└ĪŻ512źėź├ź╚ż╚ĮjżŁż╩┐¶ż╬░┼ęÄ▓Į▒ķōQż“╣įż”╠┐╬ßżõĪóź┘ź»ź╚źļAESĪ╩Advanced Encryption StandardĪ╦╠┐╬ßż╚ĘÕæųż▓ż╩żĘź┘ź»ź╚źļŠĶōQ╠┐╬ßĪó│╚─źSHAĪ╩Secure Harsh AlgorithmĪ╦ż╩ż╔ż“╝{▓├żĘżŲżżżļĪŻż│żņż╦żĶżĻ░┼ęÄ▓Į▒ķōQż“CPUż¼╝┬╣įżĘżõż╣ż»ż╩żļĪŻ

║Żöv╚»╔ĮżĄżņż┐Xeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄż╬ź┴ź├źūź╗ź├ź╚ż“╗╚ż├ż┐źĄĪ╝źąż“Ų▒Ų³ĪóSupermicro Computer╝ęż¼╚»╔ĮżĘżŲżżżļĪ╩╗▓╣═½@╬┴2Ī╦ĪŻDISHż╬ź©ź├źĖ┤├ŽČ╔Ė■ż▒żõĮj║ÕĮj│žż╦Ū╝żßżŲżżżļż╚żżż”ĪŻ

╗▓╣═½@╬┴

1. Intelż╬11└ż┬ÕźūźĒź╗ź├źĄĪó╚∙║┘▓ĮżĶżĻżŌFinFETż╚¾H┴žŪ█└■ż╦╣®╔ū (2020/09/04)

2. Performance Begins Now X12