Š«Ę┐Īó─ŃŠ├õJ┼┼╬üż╬FD-SOIż╦żĶżļ10╦³ź▓Ī╝ź╚ż╬FPGAż“Latticeż¼Įą▓┘

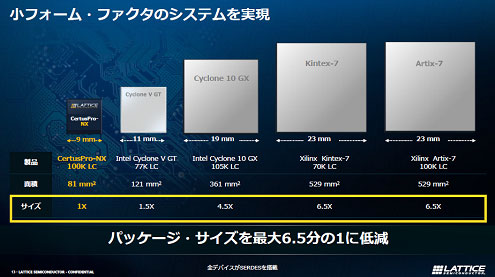

10╦³ź▓Ī╝ź╚ż╬├µæä╠ŽFPGAż╩ż¼żķĪóźčź├ź▒Ī╝źĖĀC└čż¼81mm2żĘż½ż╩żż×æēäĪųCertusPro-NXĪūż“Lattice Semiconductorż¼źĄź¾źūźļĮą▓┘ż“│½╗ŽżĘż┐ĪŻSamsungż╬28nm FD-SOIĪ╩Fully Depleted Silicon on InsulatorĪ╦źūźĒź╗ź╣ż“╗╚ż├żŲżżżļż┐żßĪóSRAMź┘Ī╝ź╣ż╬FPGAż╩ż¼żķźĮźšź╚ź©źķĪ╝╬©ż¼1/100 FITż╚ż½ż╩żĻŠ«żĄżżĪŻ

┐▐1ĪĪźšź®Ī╝źÓźšźĪź»ź┐ż¼ż╚ż╦ż½ż»Š«żĄżżFPGAĪĪĮąųZĪ¦Lattice Semiconductor

XilinxżõIntelĪ╩ĄņAlteraĪ╦ż¼Įj(lu©░)æä╠Žż“╝{Ąßż╣żļFPGAż╦×┤żĘżŲĪóŠ«├µæä╠Žż╬FPGAżŪ▒M╔ķż╣żļLatticeżŽĪóż│żņż▐żŪż╬ź│ź¾ź┌źŲźŻź┐ż╬─¾ČĪż╣żļ×æēäżĶżĻżŌ░Ą┼▌┼¬ż╦Š«żĄżż×æēäĪ╩┐▐1Ī╦ż“ĮążĘż┐ĪŻFPGAżŽźŽĪ╝ź╔ź”ź©źóżŪ┴╚żÓźĒźĖź├ź»ż“żõż┐żķż╚Įj(lu©░)żŁż»ż╣żļż╦żŽżŌżŽżõ╠Ą═²ż¼ĮążŲżŁżŲżżżļĪŻXilinxżõIntelżŽĮj(lu©░)æä╠Ž▓Įż╦×┤żĘżŲĪóFPGAövŽ®ż“ĮĖ└čżĘż╩ż¼żķCPUżõźßźŌźĻżŌ┼ļ║▄żĘżŲźĮźšź╚ź”ź©źóżŪź½ź╣ź┐ź▐źżź║ż╣żļŗ╩¼ż╚źŽĪ╝ź╔ź”ź©źóżŪź½ź╣ź┐ź▐źżź║ż╣żļFPGAż╬╬ŠöĄ(sh©┤)ż“ĮĖ└čżĘż┐SoCż“─¾ČĪżĘżŲżŁżŲżżżļĪŻ

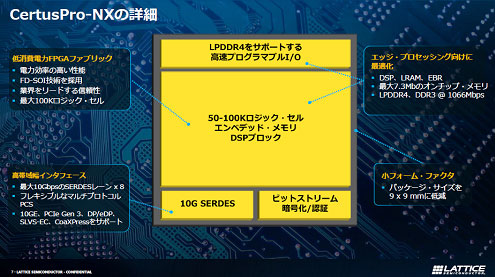

ż│żņż╦×┤żĘżŲLatticeżŽĪóFPGAż“├µ┐┤ż╚żĘż╩ż¼żķżŌź█ź╣ź╚CPUżžż╬ż─ż╩ż«ż╚ż╩żļ╣Ł┬ė░Ķ╔²źżź¾ź┐Ī╝źšź¦źżź╣ż╬SERDESĪ╩─Šš`╩┬š`╩č┤╣Ī╦└ņ├ōövŽ®ż“ĮĖ└čżĘĪó10Gbpsż╬PCIeż“źĄź▌Ī╝ź╚żĘżŲżżżļĪ╩┐▐2Ī╦ĪŻSERDESżŽĪóź▐źļź┴źūźĒź╚ź│źļż“źūźĒź░źķźÓżŪżŁżļżĶż”ż╦ż╩ż├żŲżżżļĪŻźĘź╣źŲźÓż╬╣ŌÅ]▓Įż“ܦ▐qż╣żļż┐żßż╦LPDDR4ż“źĄź▌Ī╝ź╚ż╣żļ╣ŌÅ]ż╬źūźĒź░źķź▐źųźļI/OżŌĮĖ└čżĘżŲżżżļĪŻżĄżķż╦źūźĒź░źķź▐źųźļż╩źĒźĖź├ź»ŗ╩¼ż╦żŽ║ŪĮj(lu©░)7.3Mźėź├ź╚ż╬SRAMż“ĮĖ└čżĘĪóźņźżźŲź¾źĘż╬ø](m©”i)żżźŪĪ╝ź┐ĮĶ═²ĪóØŖż╦AIĮĶ═²ż“▓─ē”ż╚żĘżŲżżżļĪŻ

┐▐2ĪĪ50kĪ┴100kż╬źĒźĖź├ź»ź╗źļż╦▓├ż©żŲĪóź█ź╣ź╚ż╚ż╬─╠┐«ż╦10Gbpsż╬PCIeż╦▓├ż©Īóź©ź├źĖĮĶ═²Ė■ż▒ż╬╣ŌÅ]I/OĪ󿥿ķż╦AIĮĶ═²├ōż╬DSPż╚EBRźąź├źšźĪźßźŌźĻĪó║ŪĮj(lu©░)7.3Mźėź├ź╚źßźŌźĻż“ĮĖ└čżĘżŲżżżļĪĪĮąųZĪ¦Lattice Semiconductor

ż▐ż┐ĪóśOŲ░┘ZżõŠÅČ╚├ōĪó─╠┐«źżź¾źšźķĖ■ż▒ż╩ż╔ź▀ź├źĘźńź¾ź»źĻźŲźŻź½źļż╩▒■├ōż╦Ė■ż▒ĪóźóźļźšźĪ└■ż╦żĶżļźĮźšź╚ź©źķĪ╝╬©Ī╩SERĪ╦ż“─┤ż┘ż┐ĪŻźóźļźšźĪ└■ż“FPGAźŪźąźżź╣ż╦2╗■┤ųŠ╚╝o(j©¼)żĘ¶öż▒ĪóżĮż╬SERż“Ēö╣ń┬Š╝ę2╝ęż╚Č”ż╦źŲź╣ź╚żĘż┐ĪŻĒö╣ń2╝꿎ĪóźĮźšź╚ź©źķĪ╝ż“ÅŚżĘż┐öv┐¶żŽ290övĪó107övż╚Č”ż╦100övż“«Ćż©ż┐ż¼ĪóLatticeż╬┐Ę×æē俎ź╝źĒżŪżóż├ż┐ĪŻśŗ(g©░u)ż╩żļźŲź╣ź╚ż╦żĶż├żŲĪóLatticeżŽ1/100 FITż╚żżż”─ŃżżSERż“ĄßżßżŲżżżļĪŻż│ż╬FITĪ╩Failure in TimeĪ╦ż╚żżż”┐¶ÖC(j©®)żŽĪó10ż╬9ŠĶĪ╩10▓»Ī╦ż╬ŗēäĪ”╗■┤ų┼÷ż┐żĻż╬Ė╬ŠŃ╬©ż“╔Įż╣├▒░╠żŪĪó╬Ńż©żąŗēä1000Ė─ż“100╦³╗■┤ųźŲź╣ź╚żĘżŲ╔į╬╔ż¼1Ė─ĮążļŠņ╣ńż“1FITż╚─Ļ▒IżĘżŲżżżļĪŻ

Latticeż╬SRAMź┘Ī╝ź╣ż╬FPGAż╬źóźļźšźĪ└■ż╦żĶżļĖ╬ŠŃ╬©ż¼─Ńżżż╬żŽĪóSOIČ\Įčż“╗╚ż├ż┐ż┐żßżŪżóżļĪŻFinFETż└ż╚źąźļź»ż“╗╚ż”ż┐żßĪó┼┼░Ąż╦żĶżļȧĒś┴žż¼įÆöĄ(sh©┤)Ė■ż╦Įą═ĶżļĪŻż│ż╬ż┐żßĪó╩³╝o(j©¼)└■ż╩ż╔ż╦żĶżļ┼┼╗ę-┘ć╣”×┤ż¼Ö┌ż▐żņżŲźėź├ź╚╚┐┼Šż“ÅŚż│ż╣▓─ē”└Łż¼╣Ōżżż¼ĪóSOIżŽ▓╝├Žż¼¤©▓Į╦ņż╩ż╬żŪȧĒś┴žżŽ╣Łż¼żķż║Īó┼┼╗ę-┘ć╣”×┤ż¼╚»Ö┌ż╣żļ▓─ē”└ŁżŽ─ŃżżĪŻSERż¼─Ńżżż│ż╚żŽĪóFD-SOIż╬║ŪĮj(lu©░)ż╬źßźĻź├ź╚ż╚żŌżżż©żļĪŻ

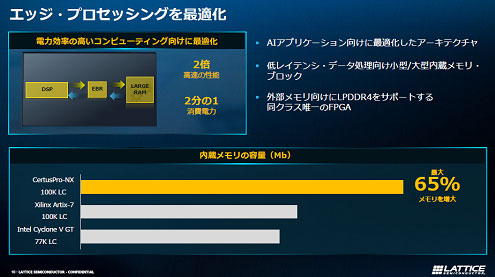

ĄĪē”ż╚żĘżŲżŽĪóAI├ōż╦║Ū┼¼▓ĮżĘż┐źóĪ╝źŁźŲź»ź┴źŃż“┬Ęż©ż┐Ī╩┐▐3Ī╦ĪŻMAC▒ķōQ└ņ├ōż╬DSPźųźĒź├ź»ż╦▓├ż©Īóźąź├źšźĪźßźŌźĻEBRĪ╩Embedded Block RAMĪ╦ż╚Īó║ŪĮj(lu©░)7.3Mźėź├ź╚ż╬Įj(lu©░)═Ų╬╠źßźŌźĻż“?y©żn)óż©żŲż¬żĻĪóĄĪ│Ż│žØ{żõźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ĮĶ═²ż“╣įż”ż╬ż╦Ė■żżżŲżżżļĪŻżĄżķż╦│░ŗż╬Įj(lu©░)═Ų╬╠╣ŌÅ]źßźŌźĻLPDDR4ż“źĄź▌Ī╝ź╚ż╣żļźūźĒź░źķźÓ▓─ē”ż╩źżź¾ź┐Ī╝źšź¦źżź╣ż“└▀ż▒ż┐ĪŻ

┐▐3ĪĪAIż╩ż╔ź©ź├źĖĮĶ═²ż╦┼¼żĘż┐źóĪ╝źŁźŲź»ź┴źŃżŪ╣ŌÅ]Ī”─ŃŠ├õJ┼┼╬üż“┴└ż”ĪĪĮąųZĪ¦Lattice Semiconductor

▒■├ōż╚żĘżŲĪó▓░│░ż╬─╠┐«┤├ŽČ╔żõśOŲ░┘ZĪó╣®Č╚├ōĪó╦╔Ä┼ż╩ż╔ż“„[─ĻżĘżŲż¬żĻĪó-40Ī┴+125°Cż╬╗╚├ōča(b©│)┼┘šJ(r©©n)░Žż╦×┤▒■ż╣żļĪŻż│żņżķż“„[─ĻżĘżŲĪóAIżõź▐źĘź¾źėźĖźńź¾ĪóśOŲ░┘Zż╩ż╔ż╬▒■├ōż“śŪ┐╩ż╣żļż┐żßĪóĘQ¹|ż╬źĮźšź╚ź”ź©źóź╣ź┐ź├ź»żŌ├ō┴TżĘżŲżżżļĪŻAIż╦żŽSensAIźĮźšź╚ź”ź©źóź╣ź┐ź├ź»żŪAIźĮźĻźÕĪ╝źĘźńź¾ż╬╝┬äóż“śŪ┐╩ż╣żļĪŻź▐źĘź¾źėźĖźńź¾żõśOŲ░▒┐┼Š┘Zż╦Ė■ż▒ż┐ADASĪóźėźŪź¬┤Ų£åż╩ż╔ż╦żŽmVisionźĮźšź╚ź”ź©źóź╣ź┐ź├ź»ż“┬Ęż©żŲżżżļĪŻżĮżĘżŲĪóIndustry 4.0żõśOŲ░▓Įż╬ż┐żßż╬źĮźšź╚ź”ź©źóź─Ī╝źļAutomateż“╗╚ż├żŲĪó═Įē¶(m©©ng)╩▌µ£ĄĪē”ż“?y©żn)óż©ż┐ź▐źļź┴ź┴źŃź¾ź═źļźŌĪ╝ź┐öU(ku©░)Ėµżõźżź¾źŲźĻźĖź¦ź¾ź╚ż╩ŠÅČ╚źĘź╣źŲźÓż“╣Į├█żĘżõż╣ż»żĘżŲżżżļż╚żżż”ĪŻ