NvidiaĪó║Ū┐ĘGPUÄźCPUÄźź═ź├ź╚ź’Ī╝ź»ź┴ź├źūżŪ└ż─c║Ūäėż╬ź│ź¾źįźÕĪ╝ź┐ż“║Ņżļ

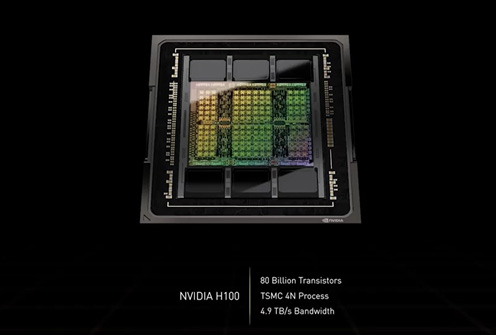

GPUĪ╩ź░źķźšźŻź├ź»ź╣źūźĒź╗ź├źĄĪ╦źßĪ╝ź½Ī╝ż╬źšźĪźųźņź╣╚ŠŲ│öüNvidiaż¼800▓»ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čĪóTSMCż╬4nmźūźĒź╗ź╣ź╬Ī╝ź╔Ī╩4NĪ╦żŪ×æļ]żĘż┐╝Ī└ż┬ÕGPUż╚ż╩żļNvidia H100Ī╩┐▐1Ī╦ż“│½╚»żĘż┐ĪŻ║ŻĮĄ│½╠¢żĄżņżŲżżżļGTCĪ╩GPU Technology ConferenceĪ╦2022ż╬┤─┤╣ų▒ķżŪĪóŲ▒╝ęCEOż╬Jensen HuangĢ■ż¼£½żķż½ż╦żĘż┐ĪŻźčź├ź▒Ī╝źĖź¾ź░ż╦żŌTSMCż╬CoWoSČ\Įčż“╗╚ż├ż┐ĪŻ

┐▐1ĪĪ800▓»ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čżĘż┐GPUĪĪĮąųZĪ¦Nvidia

źųźķź¾ź╔ć@ĪųHopperĪūż╚Ō}żųH100ź┴ź├źūż╬║ŪĮjż╬ØŖ─╣żŽĪó│╚─ź└Łż“Ęeż┐ż╗ĪóżĮż╬ż▐ż▐±ś┐¶ż“╗\żõż╗żļżĶż”ż╦ź»źķź”ź╔żõźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╩ż╔ż╬ITźżź¾źšźķż╦╣ńż’ż╗żŲ└▀╝ŖżĘżŲżżżļż│ż╚ż└ĪŻØŖż╦Īó80GBż╬źßźŌźĻ═Ų╬╠ĪóźßźŌźĻźąź¾ź╔╔²Īóź┴ź├źūŲŌĪ”ź┴ź├źū┤ųż“└▄¶öż╣żļź═ź├ź╚ź’Ī╝źŁź¾ź░ĪóNVLinkź┴ź├źūŲ▒╗╬ż╬źŪĪ╝ź┐źņĪ╝ź╚ż¼─Ń▓╝żĘż╩żżżĶż”ż╦└▀╝ŖżĘż┐ż╚żżż”ĪŻ

┐▐1żŪĖ½ż©żļżĶż”ż╦Śē┐¦ż╦«öż»ź┴ź├źūż╬æų▓╝ż╦6Ė─ż╬HBMĪ╩High Bandwidth MemoryĪ╦3źßźŌźĻż¼Ū█ÅøżĄżņżŲż¬żĻĪóż│ż╬H100ż¼║Ū┐Ęæä│╩ż╬HBM3ż“ĮķżßżŲ║╬├ōż╣żļ×æēäż╚ż╩żļĪŻ6Ė─1┴╚ż╬źßźŌźĻż╬I/O┬ė░Ķ╔²żŽ40 Tera-bits/sż╚Č╦żßżŲ╣ŁżżĪŻż┴ż╩ż▀ż╦ĖĮ║▀└ż─cż╬źżź¾ź┐Ī╝ź═ź├ź╚ź”ź¦źųż╬ź╚źķźšźŻź├ź»żŽĪóH100ź┴ź├źū20Ė─╩¼ż╦┴Ļ┼÷ż╣żļĪóż╚HuangĢ■żŽĮęż┘żŲżżżļĪŻż│ż╬╣Łżżźąź¾ź╔╔²żŪŗī5└ż┬Õż╬PCIeż“║╬├ōżĘż┐║ŪĮķż╬GPUżŪżŌżóżļż╚żżż”ĪŻ

ż│ż╬ź┴ź├źūżŽAIĪ╩ĄĪ│Ż│žØ{żõźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░Ī╦Ų░║Ņż╦żŽ║ŪĮjĖ┬ż╬╣═╬Ėż“żĘżŲżżżļĪŻ║ŻövĪó8źėź├ź╚╔ŌŲ░Š«┐¶┼└▒ķōQFP8ż╦żŌ×┤▒■Īó4 PetaFLOPSĪ╩Floating point Operations per SecondĪ╦ż╬└Łē”ż“įużŲżżżļĪŻPetażŽTeraż╬1000Ū▄żŪĪóGigaż╬100╦³Ū▄żŪżóżļĪŻż│żņż▐żŪż╬A100Ų▒══ĪóFP16ĪóFP32ĪóFP64ż╦żŌ×┤▒■Īó└Łē”żŽżĮżņżŠżņ2 PetaFLOPSĪó60 TeraFLOPSż╚ż╩ż├żŲżżżļĪŻ║Żövż╬Hopper H100ź┴ź├źūż╬└Łē”żŽĪó“£═ĶŲ▒╝ęż╬Ampere A100ż╬FP16ż╚╚µż┘żŲĪóFP8żŪ6Ū▄╣ŌżżĪŻ

▓├ż©żŲĪóAIż╬źŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░źŌźŪźļTransformerżŌ│½╚»Īó╝┬╣įż╣żļż┐żßż╬└ņ├ōź©ź¾źĖź¾Transformerź©ź¾źĖź¾żŌĮĖ└čżĘż┐ĪŻż│ż╬ź©ź¾źĖź¾żŽ┐Ęż┐ż╦╝{▓├żĘż┐FP8ż╚FP16ż╬┐¶├═▒ķōQĘ┴╝░ż“╗╚żżĪó╣Ō┼┘ż╩źĮźšź╚ź”ź©źóźóźļź┤źĻź║źÓż“┴╚ż▀╣ńż’ż╗żļż╚Īóż│żņż▐żŪ┐¶ĮĄ┤ųżŌż½ż½ż├żŲżżż┐żĶż”ż╩╦─Įjż╩źčźķźßĪ╝ź┐ż╬AIźŌźŪźļż“┐¶Ų³żŪ▒ķōQżŪżŁżļżĶż”ż╦ż╩żļĪŻź½ź╣ź┐źÓ╗┼══ż╬Hopper Tensor ź│źóżŽĪóAIż╬▒ķōQż“FP8ż╚FP16ż“ź└źżź╩ź▀ź├ź»ż╦└┌żĻü÷ż©żķżņżļĪŻFP8żŽ╗@┼┘ż¼»¤żżżŌż╬ż╬▒ķōQżŽÅ]żżĪŻFP16żŽ╗@┼┘ż¼2Ū▄╣Ōżżż¼ęÆżżĪŻźŌźŪźļż╬źčźķźßĪ╝ź┐▒ķōQżŪżĮżņżķż“ź└źżź╩ź▀ź├ź»ż╦└┌żĻü÷ż©żļż│ż╚żŪĪó╗@┼┘ż╚▒ķōQÅ]┼┘ż╬╬Š╬®ż“┐▐żļż│ż╚ż¼żŪżŁż┐ż╚żĘżŲżżżļĪŻ

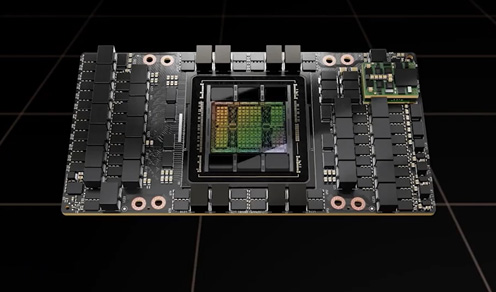

┐▐2ĪĪGPUź┴ź├źūH100ż“ź▄Ī╝ź╔ż╦╝┬äóżĘż┐źŌźĖźÕĪ╝źļĪĪĮąųZĪ¦Nvidia

800▓»ź╚źķź¾źĖź╣ź┐ż╬H 100 GPUź┴ź├źūżŽĪóTSMCż¼CoWoSĪ╩Chip on Wafer on SubstrateĪ╦ż╚Ō}żų 2.5Dźčź├ź▒Ī╝źĖż╚HBM3źßźŌźĻĪ󿥿ķż╦─Ļ┼┼░Ąźņź«źÕźņĪ╝ź┐ż“SXMż╚Ō}żųź╣Ī╝źčĪ╝ź┴ź├źūźŌźĖźÕĪ╝źļż╦ĮĖ└迥żņżŲżżżļĪ╩┐▐2Ī╦ĪŻCoWoSČ\Į迎Øi└ż┬Õż╬A100żŪżŌ╗╚ż’żņż┐ĪŻ

NvidiażŽźšźĪźųźņź╣╚ŠŲ│öüźßĪ╝ź½Ī╝żŪżóżĻż╩ż¼żķĪóź│ź¾źįźÕĪ╝ź┐ż▐żŪ║ŅżĻæųż▓żŲżżżļĪŻ║ŻövżŽDGX H100ż╚żżż”AIź│ź¾źįźÕĪ╝ź┐ż“┐āżĘż┐ĪŻ8Ė─ż╬H100 SXMźŌźĖźÕĪ╝źļż¼HGXź▄Ī╝ź╔æųż╦┼ļ║▄żĄżņĪó4Ė─ż╬NVLink ź╣źżź├ź┴ź┴ź├źūżŪGPUż“└▄¶öżĘżŲżżżļĪŻĘQNVLinkź╣źżź├ź┴ ź┴ź├źūż╦żŽ3.6TFLOPSż╬Sharpźżź¾ź═ź├ź╚ź’Ī╝ź»ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż¼ŲŌē┼żĄżņżŲżżżļĪŻż│żņżŽāA╝²żĘż┐Mellanoxż╬InfiniBand ź╣źżź├ź┴ż“ź┘Ī╝ź╣ż╦╚»£½żĄżņż┐żŌż╬ĪŻSharpżŽźąź¾ź╔╔²ż“Ė·╬©żĶż»3Ū▄ż▐żŪ╣Łż▓żļż│ż╚ż¼żŪżŁżļż╚żżż”ĪŻ

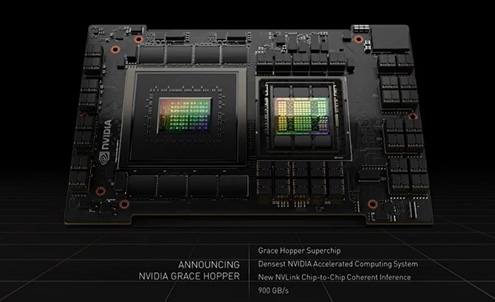

┐▐3ĪĪ Grace CPU Superchipż╚Ō}żążņżļGPUż“öUĖµż╣żļż┐żßż╬CPUĪĪĮąųZĪ¦Nvidia

DGX H100ż╦żŽ8Ė─ż╬GPUµ£öüż“öUĖµż╣żļż┐żßż╬CPUż¼ØŁ═ūż╚ż╩żļĪŻHuangĢ■żŽCPU×æēäż╚żĘżŲGrace CPU Superchipż╚ć@¤²ż▒ż┐CPUż“│½╚»Ī╩┐▐3Ī╦Īó2ź┴ź├źū╣Į└«żŪDGX H100ż“öUĖµż╣żļĪŻ│╚─ź└ŁżŌĘeż┐ż╗żŲżżżļż┐żßĪó2ź┴ź├źū╣Į└«żŪ║ŪĮj8Ė─ż╬H100 GPUż“öUĖµżĘż┐ż╬ż¼źĄĪ╝źąĪ╝DGX H100żŪżóżļĪŻ2Ė─ż╬CPUżŽĪó900GB/sż╬NVLinkżŪż─ż╩ż¼ż├żŲż¬żĻĪóźßźŌźĻźąź¾ź╔╔²1Terabyte/sż“╝┬ĖĮżĘżŲżżżļĪŻż│ż╬CPUż╦żŽ144Ė─ż╬ź│źóż¼ĮĖ└迥żņżŲżżżļĪŻ

GPUź┴ź├źū┤ųż“└▄¶öż╣żļż╬żŽĪó2Ė─ż╬ź═ź├ź╚ź’Ī╝ź»źŌźĖźÕĪ╝źļĪŻż│żņżŽĪóżĮżņżŠżņ4ż─ż╬400Gbps CX7 IBż½Īó400GbpsźżĪ╝źĄź═ź├ź╚ź’Ī╝ź»ź┴ź├źūż“×óż©żŲżżżļĪŻConnect X-7żŽź═ź├ź╚ź’Ī╝ź»ź╣źżź├ź┴żŪżóżĻĪó400 Gbit/sżŪGPUź┴ź├źū┤ųż“└▄¶öż╣żļĪŻCX-7ź┴ź├źūżŽTSMCż╬7nmźūźĒź╗ź╣żŪ║Ņżķżņż┐80▓»ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čżĘżŲżżżļĪŻ

AIź│ź¾źįźÕĪ╝ź┐ĪóDGX H100ż╦żŽ8Ė─ż╬GPUź▄Ī╝ź╔ż¼└▄¶öżĄżņżŲż¬żĻĪóżĮżņżķżŽNVLinkź╣źżź├ź┴żŪ└▄¶öżĄżņżŲżżżļĪŻAI└Łē”ż╚żĘżŲĪó32Peta FLOPSż╚Č├░█┼¬ż╩╣ŌżĄżŪżóżĻĪó┼ļ║▄żĄżņż┐HBM3źßźŌźĻżŽ640GBż╦żŌĄ┌żųĪŻżĮż╬źßźŌźĻźąź¾ź╔╔²żŽ24 TeraBytes/sż╚╣ŁżżĪŻ

ż│ż╬DGX H100ź│ź¾źįźÕĪ╝ź┐ż╦żŽ│╚─ź└Łż¼żóżĻĪóNVLinkżŪżŽ║ŪĮj32±śż╬DGXż“└▄¶öżŪżŁżļĪŻż│ż│ż╦NVLink ź╣źżź├ź┴źĘź╣źŲźÓż“ŠW├ōż╣żļż╚Īó▐kż─ż╬ĄĮjż╩32ź╬Ī╝ź╔ż╬256 GPU DGX PODż╦ź╣ź▒Ī╝źļźóź├źūżŪżŁżļĪŻ20.5 Tera źąźżź╚źßźŌźĻż╬HBM3ż╚Īó768 Terabyte/sż╬źßźŌźĻźąź¾ź╔╔²ż╚żżż”ż╚żŲż─żŌż╩żżĄĮjż╩źĘź╣źŲźÓż╦ż╩żļĪŻż┴ż╩ż▀ż╦źżź¾ź┐Ī╝ź═ź├ź╚µ£öüż╬źąź¾ź╔╔²ż¼100Terabyte/s ż└ż╚żżż”ĪŻż│ż”żĘżŲżŪżŁż┐DGX PODż╬AI└Łē”żŽĪó1 Exa FLOPSż╦żŌż╩żļĪŻ

żĄżķż╦Īóż│ż╬DGX PODż“18±ś└▄¶öżĘż┐ź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐EosĪ╩źżź¬ź╣Ī╦ż“äh▓┴żĘżŲż▀żļż╚ĪóAI└Łē”żŽĪó18.4ExaFLOPSż╚ż╩żĻĪóŲ³╦▄ż╬ź╣źčź│ź¾Īų╔┘▀tĪūż╬4Ū▄ż╬└Łē”ż╦ż╩żļĪŻEosżŪżŽĪó576±śż╬DGXĪó4608Ė─ż╬H100 GPUż¼┼ļ║▄żĄżņżŲżżżļĪŻ

╗▓╣═½@╬┴

1. "NVIDIA H100 Tensor Core GPU Architecture", Nvidia Whitepaper