LatticeĪóźĘź╣źŲźÓż╬Īųźņź┤Īū▓Įż╦Ė■ż▒ż┐┐ĘFPGA×æēäż╚O-RAN▒■├ōź╣ź┐ź├ź»

5Gż╬┐ʿʿż┤├ŽČ╔Č\ĮčO-RANż╦Ė½żķżņżļżĶż”ż╦źĘź╣źŲźÓż“╩¼│õż╣żļźŪźŻź╣źóź░źĻź▓Ī╝źĘźńź¾ż¼┐╩ż¾żŪżżżļĪŻż│żņż▐żŪżŽ▓┐żŪżŌż½ż¾żŪżŌµ£żŲ┼²╣ń▓Įż╣żļ’łĖ■ż╦żóż├ż┐ż¼ĪóżĮżņżķż“╩¼│õżĘĪó└@├ō└Łż“Ęeż┐ż╗żŲĖ▄Ąęż¼└ņ├ōĄĪż“║ŅżņżļżĶż”ż╦ż╣żļĪųźņź┤Īūż╬żĶż”ż╩╚»„[ż└ĪŻżĮżņż╦Ė■ż▒ż┐FPGA×æēäż“Latticeż¼źĻźĻĪ╝ź╣ĪóO-RANźĮźĻźÕĪ╝źĘźńź¾ź╣ź┐ź├ź»żŌ├ō┴TżĘż┐ĪŻ

┐▐1ĪĪ╩Ż╗©ż╩źĘź╣źŲźÓż“╩¼│õżĘżŲį~├▒ż╦ĪĪĮąųZĪ¦Lattice Semiconductor

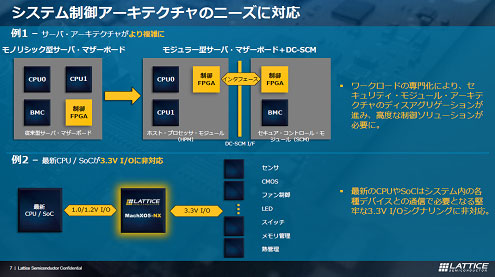

╗ęČĪż╦┐═Ążż╬ż¬żŌż┴żŃżŪżóżļĪųźņź┤ĪūżŽ║YØŹ┼¬ż╩└@├ō└Łż╬żóżļ▒·õüż“┬Ęż©ż┐Š«żĄż╩ŗēäż└ĪŻż│żņż“╗╚ż├żŲ╗ęČĪżŽĪóŲ╚śOż╬źŌź╬Ī╩└ņ├ōēäĪ╦ż“║ŅżĻæųż▓żļĪŻźĘź╣źŲźÓżŽżóż▐żĻż╦żŌ╩Ż╗©ż╦Īó└ņ├ōźĘź╣źŲźÓżŽ╣Ō▓┴ż╦ż╩żĻż╣ż«żļ’łĖ■ż¼żóżļż┐żßĪóźņź┤ż╬żĶż”ż╩└@├ō└Łż╬żóżļźĄźųźĘź╣źŲźÓż╦╩¼│õż╣żļż│ż╚żŪ─Ńź│ź╣ź╚ż╦żĘżŲĪó¾Hż»ż╬┤ļČ╚ż¼╗▓Ų■żŪżŁżļźĘź╣źŲźÓ║ŅżĻżžż╚╩čż’żĻż─ż─żóżļĪŻ

╬Ńż©żąĪóź╗źŁźÕźĻźŲźŻż╬żĘż├ż½żĻżĘż┐CPUż“1ź┴ź├źūżŪ║ŅżĒż”ż╚ż╣żļż╚ź┴ź├źūĀC└čż¼╗\▓├żĘĪó└@├ō└ŁżŽ╝║ż’żņżŲżĘż▐ż”ĪŻż│ż╬ż┐żßĪóźĘź╣źŲźÓż╬CPUź▄Ī╝ź╔ż╚ź╗źŁźÕźĻźŲźŻź▄Ī╝ź╔ż╦╩¼│õż╣żņżąĪ╩┐▐1Ī╦ĪóżĮżņżŠżņ└@├ō└Łż¼╗\żĘĪóźėźĖź═ź╣ż╚żĘżŲżŌżĮżņżŠżņż“╚╬ŪõżĘżõż╣ż»ż╩żļĪŻ

żĮż╬▐kż─ż╬źŪźŻź╣źóź░źĻź▓Ī╝źĘźńź¾ż╬╝┬╬Ńż¼5G┤├ŽČ╔ż╬O-RANĪ╩Open Radio Access NetworkĪ╦źĘź╣źŲźÓż└ĪŻż│żņż▐żŪEricssonżõNokiaĪó▓┌░┘ż╩ż╔ĄĮj─╠┐«┤ļČ╚ż¼└ż─cż╬─╠┐«ź¬ź┌źņĪ╝ź┐ż╦Ū╝Ų■żĘżŲżŁż┐ĪŻźĘź╣źŲźÓŲ░Ė■ż“ē¶żļż│ż╚ż¼╔įįu┴Tż╩NECżõ╔┘╗╬─╠ż╬żĶż”ż╩Ų³╦▄└¬żŽµ£ż»žøż¼╬®ż┐ż╩ż½ż├ż┐ĪŻżĘż½żĘĪóźóź¾źŲź╩ŖZż»ż╬RFźµź╦ź├ź╚Ī╩RUĪ╦ż╚ĪóRFźšźĒź¾ź╚ź©ź¾ź╔ż╦ŖZżżź┘Ī╝ź╣źąź¾ź╔ż╬╩¼Ügźµź╦ź├ź╚Ī╩DUĪ╦Īó├µ▒¹ż╬▒ķōQźµź╦ź├ź╚Ī╩CUĪ╦ż╬įÆż─ż╦╩¼│õżĘĪóżĮżņżŠżņż“O-RANźżź¾ź┐Ī╝źšź¦źżź╣żŪż─ż╩ż«Īóźżź¾ź┐Ī╝źšź¦źżź╣ż“║YØŹ▓Įż╣żļż│ż╚żŪĪóŲ³╦▄└¬żŌØ▓╩¼└’ż©żļżĶż”ż╦ż╩żļĪŻż─ż▐żĻ─╠┐«ź¬ź┌źņĪ╝ź┐żŽĪóNECż╬RUż╚╔┘╗╬─╠ż╬DUĪóNokiaż╬CUż“╗╚ż├żŲ5G┤├ŽČ╔ż“║Ņżļż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩żļĪŻż│żņż¼O-RANČ\Įčż╬ŠÅČ╚┼¬ż╩źżź¾źčź»ź╚żŪżóżļĪŻ

Lattice SemiconductorżŽĪóż│ż╬żĶż”ż╩źĘź╣źŲźÓ╩¼│õż╬źŪźŻź╣źóź░źĻź▓Ī╝źĘźńź¾ż╦FPGAż╬┐Ę▌xŠņż“Ė½ż─ż▒ż┐ĪŻ┐▐1ż╬æų┐▐ż╬╬ŃżŪżŽĪóź╗źŁźÕźĻźŲźŻż“┴╚ż▀╣■ż¾ż└CPUź▄Ī╝ź╔ż“ĪóCPUż└ż▒ż╬ź▄Ī╝ź╔ż╚Īóź╗źŁźÕźĻźŲźŻż└ż▒ż╬ź▄Ī╝ź╔ż╦╩¼│õżĘĪóżĮżņżŠżņż“FPGAżŪż─ż╩ż░ż╬żŪżóżļĪŻź╗źŁźÕźĻźŲźŻź▄Ī╝ź╔ż╦żŽźĄźżźąĪ╝ŲłĘŌż“┤╔═²Ī”┤Ų£åż╣żļź▐źżź│ź¾żõ░┼ęÄ▓ĮövŽ®Īó░┼ęÄ▓ĮĖ░ż╬╩▌┘TźßźŌźĻż╩ż╔ż“┼ļ║▄żĘĪóŪ¦Š┌ż╚░┼ęÄż╬╬ŠĀCż½żķź╗źŁźÕźóż╦ż╣żļĪŻż▐ż┐Īó▓╝┐▐żŪżŽ║Ū┐Ęż╬─Ń┼┼░ĄĪ╩1V/1.2Vż╩ż╔Ī╦ż╬CPUżõSoCż“CMOSź╗ź¾źĄżõLEDöUĖµĪóÕX┤╔═²ż╩ż╔3.3VÅUż╬ICż“ż─ż╩ż░ż┐żßż╬źżź¾ź┐Ī╝źšź¦źżź╣ż╚żĘżŲż╬FPGAövŽ®ż“┐āżĘżŲżżżļĪŻ

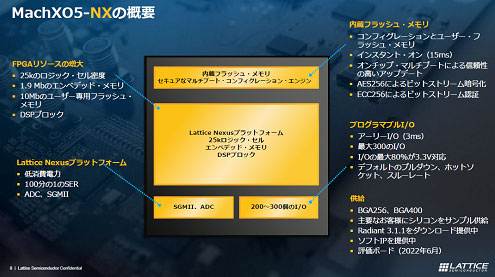

Laticeż¼ż│ż╬ż█ż╔źĄź¾źūźļĮą▓┘żĘ╗Žżßż┐MachX05-NX×æē俎Īó┐▐1żŪ┐āżĘż┐żĶż”ż╩├ō²ŗż╦Ė■ż»żĶż”ż╦Īó┐▐2ż╬övŽ®źųźĒź├ź»żŪ┐āż╣ĄĪē”ż“ĮĖ└čżĘżŲżżżļĪŻFPGAŗ╩¼ż“25kźĒźĖź├ź»ź╗źļż╚Īó1.9Mźėź├ź╚ż╬źßźŌźĻĪó10Mźėź├ź╚ż╬źµĪ╝źČĪ╝└ņ├ōźšźķź├źĘźÕźßźŌźĻĪóDSPźųźĒź├ź»ż╚żĘżŲ└@├ō└Łż“Ęeż┐ż╗Ī󿥿ķż╦ź╗źŁźÕźóż╩ŲŌē┼źšźķź├źĘźÕźßźŌźĻżŌĮĖ└čżĘż┐ĪŻżĄżķż╦└@├ōI/Oż“200Ī┴300Ė─ż╚ĪóADź│ź¾źąĪ╝ź┐żõź«ź¼źėź├ź╚╣ŌÅ]źżź¾ź┐Ī╝źšź¦źżź╣SGMIIĪ╩Serial Gigabit Media Independent InterfaceĪ╦ż╩ż╔żŌĮĖ└čżĘżŲż¬żĻĪó└@├ō└Łż¼╣ŌżżĪŻ

┐▐2ĪĪ┐Ę×æēäż╬MachX05-NXż╬ĄĪē”źųźĒź├ź»┐▐ĪĪĮąųZĪ¦Lattice Semiconductor

LatticeżŽźšźĪźųźņź╣╚ŠŲ│öüźßĪ╝ź½Ī╝ż└ż¼Īóź┴ź├źūżŽ28nmźūźĒź╗ź╣ż╬FD-SOIĪ╩Fully Depleted Silicon on InsulatorĪ╦Č\ĮčżŪ×æļ]żĄżņżŲżżżļĪŻż│ż╬ż┐żßźóźļźšźĪ└■ż╦żĶżļźĮźšź╚ź©źķĪ╝╬©SERż¼“£═ĶēäĪ╩źąźļź»CMOSĪ╦ż╬1/100ż╚─Ńżżæųż╦ĪóŠ├õJ┼┼╬üżŌ─ŃżżĪŻ

LatticeżŽĪóO-RANĖ■ż▒ż╬źĮźĻźÕĪ╝źĘźńź¾ź╣ź┐ź├ź»żŌŲ▒╗■ż╦╚»╔ĮżĘż┐ĪŻLatticeż╬FPGAż“╗╚żżĪóź█ź╣ź╚ż╚ż╬PCIeźĄźųźĘź╣źŲźÓżõĪó░┼ęÄ▓Įż╬źūźĒź╗ź├źĄżõövŽ®ż“┤▐żÓźĄźųźĘź╣źŲźÓż╩ż╔ż╦▓├ż©ĪóźóźūźĻź▒Ī╝źĘźńź¾źĮźšź╚ź”ź©źóżŌ▓├ż©ż┐źĮźĻźÕĪ╝źĘźńź¾ż╚ż╩ż├żŲżżżļĪŻż│żņż▐żŪżŌźŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒ż╦ź╝źĒź╚źķź╣ź╚ź╗źŁźÕźĻźŲźŻż“─¾ČĪżĘżŲżŁż┐ż╚żżż”ĪŻź╝źĒź╚źķź╣ź╚ż╚żŽĪóIDż“ńRŪ¦żŪżŁżļż▐żŪżŽż╔ż╬źŪĪ╝ź┐żŌ┐«├ōżĘż╩żżż╚żżż”╣═ż©ż╬╗┼┴╚ż▀żŪżóżļĪŻż│ż╬╗┼┴╚ż▀ż╦żĶżļŪ¦Š┌ż╚Īó░┼ęÄ▓Įż╬╬ŠĀCżŪź╗źŁźÕźĻźŲźŻż“│╬╩▌żĘżŲżżżļĪŻ