MicronĪó1”┬ nmź╬Ī╝ź╔ż╬64Gźėź├ź╚ż╬DDR5x-DRAMż“źĄź¾źūźļĮą▓┘

ä▌Micron Technologyż¼1”┬ nmźūźĒź╗ź╣ź╬Ī╝ź╔żŪ×æļ]żĘż┐64Gźėź├ź╚ż╬DDR5x-DRAMż╬źĄź¾źūźļĮą▓┘ż“│½╗ŽżĘż┐ĪŻMicronż¼Įęż┘żļ1”┬ nmźūźĒź╗ź╣ź╬Ī╝ź╔żŽĪó13nm░╩▓╝ż╬źūźĒź╗ź╣ź╬Ī╝ź╔ż└ż╚żżż”ĪŻ12Ī┴13nmż╚ż╬Ė½öĄżŌżóżļĪŻźĻźĮź░źķźšźŻźčź┐Ī╝ź╦ź¾ź░ż╬╝┬ĖĮż╦żŽĪóķ]┐╗ź▐źļź┴źčź┐Ī╝ź¾ź╦ź¾ź░ż“├ōżżżŲż¬żĻĪóEUVżŽ├ōżżżŲżżż╩żżĪŻ×æļ]żŽż▐ż║┼ņ╣ŁćŖ╣®ŠņżŪ╣įż”ĪŻ

┐▐1ĪĪMicronĪó1”┬ nmź╬Ī╝ź╔ż╬64Gźėź├ź╚DDR5x-DRAMż“źĄź¾źūźļĮą▓┘ĪĪĮąųZĪ¦Micron Technology

ż│żņż▐żŪDRAMżõNANDźšźķź├źĘźÕż╩ż╔ż╬źßźŌźĻżŽĪóźšźĪź”ź¾ź╔źĻż╚żŽ░█ż╩żļźŪźČźżź¾źļĪ╝źļż“├ōżżżŲżżżļĪŻ20nm░╩▓╝ż╦ż╩żļż╚Īó19nmż½żķ15Ī┴16nmż╦┼ŽżĻĪó1x nmĪó1y nmĪó1z nmż╚Š»żĘż║ż─╣’ż▀ż╩ż¼żķ╚∙║┘▓Įż“┐╩żßżŲżŁż┐ĪŻżĮż╬└ĶżŽĪó1”┴ nmĪó1”┬ nmĪó1ɤ nmż╚żĄżķż╦╣’ż¾żŪżŁż┐ż┐żßĪóMicronż╬ź¬ź¾źķźżź¾▓±Ė½żŪä®╠õżĘżŲż▀ż┐ż╚ż│żĒĪó13nm░╩▓╝ż└ż╚┼·ż©żŲżżż┐ĪŻż┐ż└żĘĪóż│ż╬źūźĒź╗ź╣ź╬Ī╝ź╔ż╬Øó╦ĪżŽż╔ż│ż╬Øó╦Īż“╗žżĘżŲżżżļż╬ż½żŽ£½żķż½ż╦żĘżŲżżż╩żżĪŻ

ż▐ż┐ĪóNANDźšźķź├źĘźÕż¼ź╗źļŗ╩¼ż“3╝ĪĖĄĪ╩3DĪ╦▓Įż╦żĶż├żŲĪóāeöĄĖ■ż╦└čż▀╗\ż╣ż│ż╚ż╦żĶż├żŲĄŁ▓▒═Ų╬╠ż“╗\żõżĘżŲżŁż┐ĪŻż│żņż╦×┤żĘżŲĪóDRAMżŌNANDźšźķź├źĘźÕż╚Ų▒══ĪóźßźŌźĻź╗źļż“3D▓Įż╣żļż│ż╚żŪ╝┬ĖĮżĘżŲżżżļĪŻDRAMź╗źļżŽĪóź╣źżź├ź┴ź¾ź░├ōż╬▐kż─ż╬ź╚źķź¾źĖź╣ź┐ż╦źŁźŃźčźĘź┐ź╗źļż“└▀ż▒żŲżżżļż¼Īóż│ż╬ź╗źļż╬║ŅżĻöĄż¼▀ģ┼¹Ę┐ż╬źĘźĻź¾ź└Ī╝ż╚ż╩ż├żŲżżżļżĶż”ż└ĪŻż│ż╬±T▓╠Īó┐▐2żŪĖ½żļżĶż”ż╦ĪóCMOS under Capacitorż╚ż╩ż├żŲżżżļĪŻ

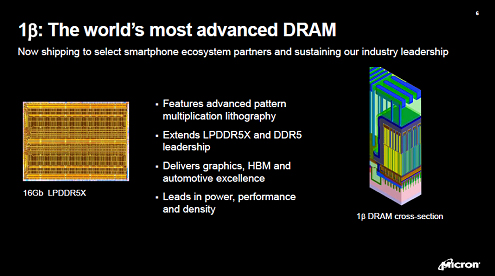

┐▐2ĪĪ1”┬ nmźūźĒź╗ź╣ż╬16Gb LPDDR5X DRAM ĮąųZĪ¦Micron Technology

ż│ż╬ż█ż╔│½╚»żĘż┐1”┬ nmźūźĒź╗ź╣ź╬Ī╝ź╔ż╬DRAMżŽĪóŲ³╦▄ż╬┼ņ╣ŁćŖ╣®ŠņżŪÖ┌ŠÅżĘĪó╝Īż╦±śŽčżŪ╬╠ŠÅż╣żļż╚żżż”ĪŻ▓┐ż¼Micronż╬ØŖ─╣ż½ż╚żżż”ä®╠õż╦×┤żĘżŲżŽĪóź│ź╣ź╚║’žō╦ĪżõĮĖ└č┼┘ĪóźßźŌźĻź╗źļż╬źĘźÕźĻź¾ź»ż╩ż╔ż╬Č\ĮčżŪźĻĪ╝ź╔żĘżŲżżżļż│ż╚Īóż╚Ų▒╝ęDRAMźūźĒź╗ź╣źżź¾źŲź░źņĪ╝źĘźńź¾├┤┼÷źąźżź╣źūźņźĖźŪź¾ź╚ż╬Thy TranĢ■żŽ┼·ż©żŲżżżļĪŻ┐Ę│½╚»ż╬DRAMżŽĪó1└ż┬ÕØiż╬1”┴ nmźūźĒź╗ź╣ź╬Ī╝ź╔ż╬×æēäż╚╚µż┘Īó┼┼╬üĖ·╬©żŽ15%Ė■æųżĘĪóźėź├ź╚╠®┼┘żŽ35%░╩æų╗\ż©ż┐ĪŻ┼┼╬üĖ·╬©ż“æųż▓żļż┐żßĪóŲ░┼¬ż╦┼┼░Ąż╚╝■āS┐¶ż“ź╣ź▒Ī╝źĻź¾ź░ż╣żļöĄ╦ĪĪ╩Dynamic Voltage Frequency ScalingĪ╦ż“├ōżżż┐ĪŻż│ż╬±T▓╠Īó3200Mbpsż▐żŪźĄź▌Ī╝ź╚ż╣żļż╚żżż”ĪŻ

ż│żņż▐żŪķ]┐╗ż╬ArFź▐źļź┴źčź┐Ī╝ź╦ź¾ź░ż“╗╚ż├ż┐źĻźĮź░źķźšźŻČ\Įčż“┐╩żßżŲżŁż┐ż¼ĪóEUVż╬╗╚├ōż╦×┤żĘżŲżŽĪóEUVČ\Įčż¼└«▌^ż╣żļ╗■┤³ż└żĒż”ż╚Ė½żŲż¬żĻĪóČ▓żķż»1ɤ nm░╩▓╝ż╬źūźĒź╗ź╣ź╬Ī╝ź╔ż╦ż╩żļ║óż└ż╚╗ūż”Īóż╚Ė½żŲżżżļĪŻ

ż▐ż┐Īóż│ż╬└Ķ1”┴ nmźūźĒź╗ź╣×æēäż╦×┤żĘżŲ1”┬ nm×æē俎żżż─║ó╝ń╬«ż╦ż╩żļż½ż╚żżż”ä®╠õż╦×┤żĘżŲĪóęŖĄļėXČĘż╦żĶż├żŲ╩čż’żļż└żĒż”ż╚Įęż┘żŲżżżļĪŻż─ż▐żĻĪóø]┤³┼¬ż╦żŽDRAMż╬źµĪ╝źČĪ╝żõ╬«─╠ż╬║▀ŚUż¼╗\ż©żŲżżżļż┐żßĪóżĮżņżķż╬─┤┼Dż¼╣įż’żņż┐ĖÕż╦Īó1”┬ nm×æē俎Ēö┴Ķ╬üż“Ęeż─ż│ż╚ż╦ż╩żĻĪó1”┴ nmźūźĒź╗ź╣×æēäż╚Ė“┬Õż╣żļż│ż╚ż╦ż╩żļż╚Ė½żŲżżżļĪŻ

ż│żņż█ż╔Įj═Ų╬╠ż╬DRAMż╬├ō²ŗżŽ“£═Ķż╬źŌźąźżźļ├ō²ŗżõźčźĮź│ź¾ĪóśOŲ░┘Zż╦▓├ż©ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝├ō²ŗż└żĒż”ż╚Įęż┘żŲżżżļĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ī╝├ō²ŗżŪżŽĪóCPUż╬╝■żĻż╦Ū█Åøż╣żļHBMĪ╩High Bandwidth MemoryĪ╦żõź░źķźšźŻź├ź»ź╣├ōż╬źßźŌźĻż╚żĘżŲżŌ╗╚ż”ĪŻ