SiTimeĪó4ż─ż╬SoCż╦Ų▒╗■ż╦ź»źĒź├ź»┐«ęÄ(gu©®)ż“┴„żņżļICż“×æēä▓Į

MEMSż“ŠW(w©Żng)├ōż╣żļ┐ČŲ░╗ęż╚╚»┐ČövŽ®Ī󟻟Ēź├ź»╚»Ö┌▀_ż“1źčź├ź▒Ī╝źĖż╦╝┬äóżĘż┐ź»źĒź├ź»ICżŽĪóŠ«Ę┐Īó╣Ō└Łē”Īó─Ńź╬źżź║ż└ż▒żŪżŽż╩ż»Ī󟻟Ēź├ź»╝■żĻż╬źūźĻź¾ź╚┤ł└▀╝ŖżŌį~░ūż╦żĘżŲż»żņżļĪŻMEMSź┘Ī╝ź╣ż╬ź»źĒź├ź»ICż“Š}²Xż▒żŲżŁż┐SiTimeż¼4ż─ż╬SoCż“Ų▒╗■ż╦ź»źĒź├ź»żŪżŁżļ4Įą╬üż╬ź»źĒź├ź»ICĪųChorusĪūż“×æēä▓ĮżĘż┐ĪŻ

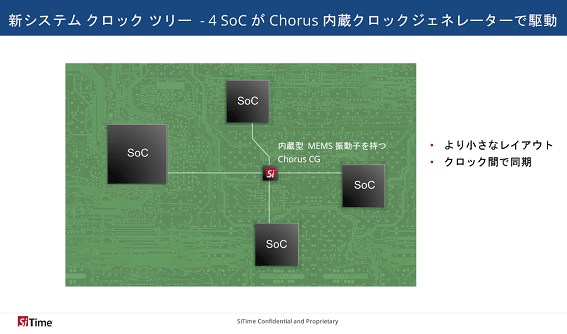

┐▐1ĪĪ1ź┴ź├źūżŪ4Ė─ż╬SoCż╦ź»źĒź├ź»┐«ęÄ(gu©®)ż“ČĪĄļż╣żļĪó┐ČŲ░╗ęŲŌē┼ż╬ź»źĒź├ź»ICĪĪĮj(lu©░)żŁżĄżŽ4mm│čż╬źčź├ź▒Ī╝źĖĪĪĮąųZĪ¦SiTime

┘ć│╬ż╩ź┐źżź▀ź¾ź░ż¼ØŁ═ūż╩źŪźĖź┐źļĄĪ▀_żŪżŽĪó┘ć│╬ż╩źčźļź╣ż“╚»Ö┌ż╣żļź»źĒź├ź»ICż¼’L(f©źng)ż½ż╗ż╩żżĪŻż│ż╬ż┐żßĪóča┼┘╩č▓Įż╦żŌ─╣┤³┤ųż╬┐«═Ļ└Łż╦żŌµ£ż»╩čż’żķż╩żżź»źĒź├ź»┐«ęÄ(gu©®)ż“Įą╬üżĘż╩ż▒żņżąż╩żķż╩żżĪŻ┘ć│╬żŪżóżļż│ż╚ż¼║Ū═ź└Ķż╬ICżŪżóżļĪŻ

┐ÕŠĮ┐ČŲ░╗꿎ča┼┘░═┘T└Łż¼äėżżż┐żßĪóźęĪ╝ź┐Ī╝ż╩ż╔żŪ─Ļčaż╦╩▌ż─ØŁ═ūż¼żóżļæųĪó┐ČŲ░╗ęż└ż▒żŪżŽ┐ČŲ░ż¼žō┐Ļż╣żļż┐żßĪóżĮżņż“▌öż”╚»┐Č▀_ż¼ØŁ═ūż╚ż╩żļĪŻż│ż│ż▐żŪżŽ┘ćĖ╣āSżŪżŌ╣Įż’ż╩żżż¼ĪóżĘż½żŌżŁż┴ż¾ż╚żĘż┐źčźļź╣ż“Įąż╣ż┐żßż╦żŽĪ󟻟Ēź├ź»╚»Ö┌▀_żŪ┘ć│╬ż╩źčźļź╣āSĘ┴ż“Įą╬üżĘż╩ż▒żņżąż╩żķż╩żżĪŻźčźļź╣āSĘ┴ż╬╬®ż┴æųż¼żĻżõæT▓╝ż╬ź©ź├źĖżŪż╬┴Ó║Ņż╩ż╔żŌĄßżßżķżņżļż½żķż└ĪŻż│żņżķ3┼└żŽźūźĻź¾ź╚┤łæųż╦źŪźŻź╣ź»źĻĪ╝ź╚żŪ┴╚ż▀╣ńż’żĄżņżŲ╗╚ż’żņżļż│ż╚ż¼¾Hż½ż├ż┐ĪŻżĘż½żĘĪóźūźĻź¾ź╚┤łæųż╬╝┬äóĀC└čż¼╠õ¼öż╦ż╩żļŠ«Ę┐Ę┴ėXżõ¾H┐¶ż╬SoCżõźóź»ź╗źķźņĪ╝ź┐ż╩ż╔ż╦ź»źĒź├ź»źčźļź╣ż“═┐ż©żķż▒żņżąż╩żķż╩ż»ż╩żļż╚Īó╝┬äóĀC└čż╦═Š═Ąż¼ż╩ż»ż╩ż├żŲżĘż▐ż”ĪŻżĘż½żŌź»źĒź├ź»ICż╬┐¶żŌźąź½ż╦ż╩żķż╩żżĪŻ

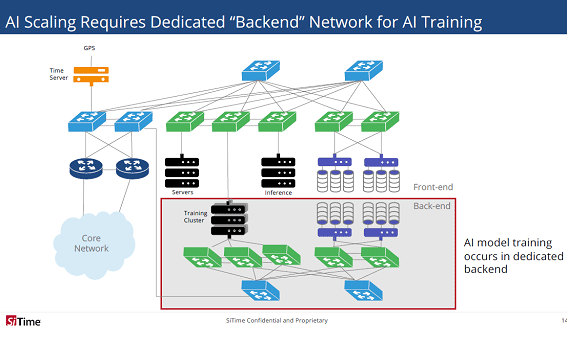

źŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŪżŽĪóŲ▒┤³ż“║╬żļż┐żßż╬ź╣źżź├ź┴żõźĄĪ╝źąĪóź╣ź╚źņĪ╝źĖż╩ż╔ż╦▓├ż©żŲĪó║ŪŖZżŽAIĪ╩ĄĪ│Ż│žØ{żõźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░Ī╦└ņ├ōż╬┐õébźĄĪ╝źążõ│žØ{źĄĪ╝źążŌ×óż©żŲżżżļĪŻØŖż╦AIż╬│žØ{źĄĪ╝źążŽĪó╔Įż╦Įąż║żÓżĘżĒ╬óżŪŲ»ż»ż│ż╚ż¼¾Hżżż¼Ī╩┐▐2Ī╦Īóżżż├ż┐ż¾│žØ{żĄż╗żŲżĘż▐ż©żąĪó┐õébźĄĪ╝źąż¼īÖ╠÷ż╣żļĪŻżĄżķż╦źŪĪ╝ź┐ź╗ź¾ź┐Ī╝żĮż╬żŌż╬żŽ▓Š„[▓ĮżĘżŲźĮźšź╚ź”ź©źóĪ╩źŽźżźčĪ╝źąźżźČĪ╦żŪź»źķźżźóź¾ź╚ż╦╩¼Ū█ż╣żļż┐żßĪóż│ż”żżż├ż┐ź╣źżź├ź┴żõźĄĪ╝źąż╬┐¶żŽ╗\ż©żļ▐köĄ(sh©┤)ż└ĪŻż│ż╬ż┐żßź»źĒź├ź»ICżŌŲ▒══ż╩ż”ż©ĪóźūźĻź¾ź╚övŽ®┤łæųż╦żŽ╩Ż┐¶ż╬ź»źĒź├ź»ICż¼ØŁ═ūż╚ż╩żļĪŻ

┐▐2ĪĪAI│žØ{źĄĪ╝źążŽ╬óżŪŲ»żżżŲżżżļĪĪĮąųZĪ¦SiTime

ż│ż”żżż├ż┐├ō²ŗż“┴└ż├ż┐ź»źĒź├ź»ICż¼║Żövż╬ĪųChorusĪūźĘźĻĪ╝ź║ż╚ż╩żļĪŻ╬Ńż©żą4ż─ż╬SoCżžź»źĒź├ź»ż“ČĪĄļż╣żļŠņ╣ńĪó“£═Ķż╩żķSoCż┤ż╚ż╦╚»┐Č▀_żõź»źĒź├ź»ICż¼ØŁ═ūż└ż├ż┐ż¼ĪóChorusźĘźĻĪ╝ź║ż└ż╚1Ė─żŪ║čżÓĪ╩┐▐2Ī╦ĪŻżĘż½żŌ1ź┴ź├źūż╬Įj(lu©░)żŁżĄż¼4mmĪ▀4mmżĘż½ż╩żżż┐żßĪóź▄Ī╝ź╔ĀC└čż“Š«żĄż»żŪżŁżļż└ż▒żŪżŽż╩ż»Īó4ż─ż╬SoCż“żŪżŁżļż└ż▒ŖZż┼ż▒żŲźņĪ╝źĘź¾ź░żõź»źĒź├ź»ęÆūāż“ķcż▒żļż│ż╚ż¼żŪżŁżļĪŻ

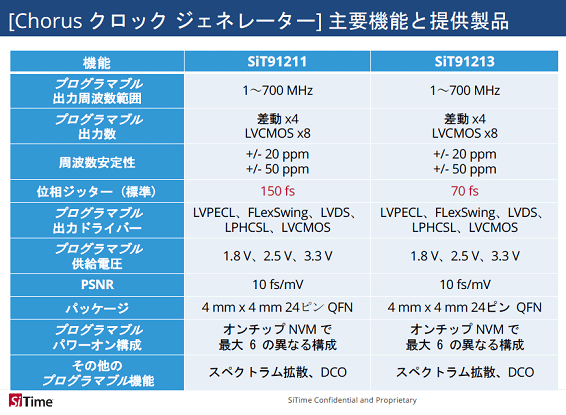

ź»źĒź├ź»ICżŪżŽĪ󟻟Ēź├ź»āSĘ┴ż╚żĮż╬░╠┴Ļ═æżķż«żŪżóżļźĖź├ź┐Ī╝ż¼Š«żĄż▒żņżąŠ«żĄżżż█ż╔╦Šż▐żĘżżż¼ĪóChorusźĘźĻĪ╝ź║żŽ150fsĪ╩10ż╬ź▐źżź╩ź╣15ŠĶ╔├Ī╦ż╚70fsż╬×æēäż¼żóżļĪŻČ╦żßżŲø]żżĪŻ

┐▐3ĪĪChorusźĘźĻĪ╝ź║ż╬ź╣ź┌ź├ź»ĪĪĮąųZSiTime

SiTimeż╬ź»źĒź├ź»ICżŽĪóMEMS┐ČŲ░╗ęż“CMOS┐«ęÄ(gu©®)ĮĶ═²ICæųż╦┼ļ║▄żĘźŌĪ╝źļź╔żŪźčź├ź▒Ī╝źĖżĘż┐×æēäĪŻMEMS┐ČŲ░╗꿎Ū÷╦ņźßź¾źųźņź¾ż“║Ņ×æż╣żļż┐żßÄņ─Šż╦┐╝ż»źĘźĻź│ź¾ż“║’żĻŲDżķż╩ż▒żņżąż╩żķż╩żżż┐żßĪóBoschźūźĒź╗ź╣ż╚Ō}żųĪóźŪź▌źĖźĘźńź¾żĘż╩ż¼żķź©ź├ź┴ź¾ź░ż╣żļż╚żżż”ĮĶ═²ż¼ØŁ═ūĪŻMEMSźŪźąźżź╣ż╬×æļ]żŽBoschĪóCMOSICżŽTSMCż╦Īóźčź├ź▒Ī╝źĖź¾ź░żŽ±śŽčż╬ASEżõź▐źņĪ╝źĘźóż╬Carsemż╦żĮżņżŠżņ░══ĻżĘżŲżżżļĪŻSiTimeżŽĮŃ┐Ķż╬źšźĪźųźņź╣ż└ĪŻ