źßź¾ź┐Ī╝ĪóSoCż╬źŪĪ╝ź┐źčź╣ÅUż└ż▒żŪżŽż╩ż»ź│ź¾ź╚źĒĪ╝źļÅUż╦żŌCĖ└Ėņ└▀╝Ŗż“│╚─ź

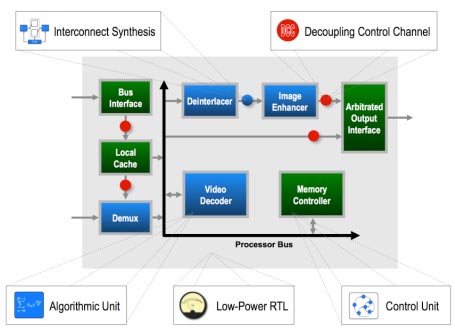

źßź¾ź┐Ī╝Ī”ź░źķźšźŻź├ź»ź╣żŽĪóCĖ└Ėņż╦żĶżļLSI└▀╝ŖŠ}╦ĪżõĖĪŠ┌ż“Īó“£═Ķż╬źŪĪ╝ź┐źčź╣ÅUövŽ®ż└ż▒żŪżŽż╩ż»Īóź│ź¾ź╚źĒĪ╝źļÅUövŽ®ż╦żŌ┼¼├ōżŪżŁżļżĶż”ż╦Catapult C Synthesisż“│╚─źĪóż│żņż╦żĶżĻźšźļź┴ź├źūż╬╣Ō░╠╣ń└«ż¼żŪżŁżļżĶż”ż╦ż╩ż├ż┐ĪŻČ╦żßżŲ╩Ż╗©ż╩źŪźĖź┐źļLSIĪóSoCż“│½╚»ż╣żļæųżŪĪóRTL║Ņ└«ż▐żŪż╬╣®┐¶ż¼ø]ż»ż╩żĻĪóż▐ż┐└▀╝ŖźŪĪ╝ź┐ż“║ŲŠW├ōżĘżõż╣ż»ż╩żļĪŻ

źŪĪ╝ź┐źčź╣żŽĪóźŪźĖź┐źļźĒźĖź├ź»övŽ®ż╬├µżŪ▓├ōQżõźĒĪ╝ź╔/ź╣ź╚źóż╩ż╔ż╬▒ķōQĮĶ═²ż“╣įż”źŪĪ╝ź┐ĘąŽ®żŪżóżĻĪóź│ź¾ź╚źĒĪ╝źļövŽ®żŽ╠┐╬ßż╦“£ż├żŲ▓┐ż“ż╔ż”ż╣żļż┘żŁż½ĪóźßźŌźĻĪ╝żõźŪĪ╝ź┐źčź╣ż╦╗ž╬ßż“Įąż╣övŽ®żŪżóżļĪŻźŪźĖź┐źļövŽ®ż╬źĘĪ╝ź▒ź¾ź╣ż╦▐pż├żŲ▒ķōQż╣żļż╬żŽźūźĒź░źķźÓż╦żĶż├żŲŠ}Įńż“żĘż├ż½żĻĮ±ż▒żą▒ķōQżŪżŁżļż┐żßĪóźŪĪ╝ź┐źčź╣övŽ®ż╬CĖ└ĖņźĄź▌Ī╝ź╚żŽ▓─ē”ż└ż├ż┐ĪŻżĘż½żĘĪóźąź╣ż╦ż¬żżżŲźŪĪ╝ź┐ż¼Ēö╣ńż╣żļż╚żŁż╬╚ĮéāżõĪó═ź└ĶĮń░╠ż╬»é─Ļż╩ż╔ż╬ź│ź¾ź╚źĒĪ╝źļövŽ®żŪżŽCĖ└Ėņ└▀╝ŖżŽż│żņż▐żŪżŪżŁż╩ż½ż├ż┐ĪŻź│ź¾ź╚źĒĪ╝źļövŽ®żŪżŽĪó£½┐ā┼¬źŌźŪźļż╦żĶżļ─┤─õż¼ØŁ═ūżŪżóżĻĪóźŪĪ╝ź┐ż╬’L═Ņżõ╠Ą£åż╣żļż│ż╚żŌÅŚżŁżļĪŻźŪĪ╝ź┐ż¼ż╩żżŠņ╣ńżŪżŌźĖźńźųż“╝┬╣įżĘż┐żĻśŗ┐ʿʿ┐żĻżĘż╩ż▒żņżąż╩żķż╩żżĪŻż│ż╬ż┐żßØŖ▓ĮżĘż┐Ė└Ėņż¼ØŁ═ūż╚żĄżņżŲżżż┐ĪŻ

SoCż╬├µż╬źūźĒź╗ź├źĄź│źóżŽARMżõMIPSĪóSHĪóVźĘźĻĪ╝ź║ĪóPowerPCż╩ż╔ż“ź│źóż╚żĘżŲ╗╚ż©żąĄ£’BżĻżļż¼Īó╝■╩šövŽ®żõ─╠┐«źąź╣öUĖµż╩ż╔╩Ż╗©ż╦ż╩ż├żŲżŁż┐ź│ź¾ź╚źĒĪ╝źļźĒźĖź├ź»övŽ®żŪżŽĪó└▀╝Ŗż¼╩Ż╗©ż╦ż╩żĻCĖ└Ėņż½żķRTLż“śOŲ░Ö┌└«ż╣żļ╣Ō░╠╣ń└«Č\Įčż¼╦Šż▐żņżŲżżż┐ĪŻ─Š└▄RTLż“ĄßżßżļŠ}╦ĪżŪżŽź┐źżź▀ź¾ź░ż“╣═╬ĖżĘż┐└▀╝ŖżõĖĪŠ┌ż╦╗■┤ųż¼ż½ż½żļæųż╦Īó└▀╝Ŗż╦║«Ų■ż╣żļźąź░żŌ¾Hż»ż╩żļĪŻRTLż╬ĖĪŠ┌ż╦żŽØiĖÕż╬╣®µćż“╣įż├ż┐żĻ═Ķż┐żĻż╣żļöv┐¶ż¼╗\ż©Īó╗■┤ųż¼ż½ż½ż├żŲżżż┐ĪŻŠ»żĘżŪżŌźąź░žōżķż╣ż┐żßż╦żŌ└▀╝Ŗż╬├Ļō■┼┘ż“æųż▓żŲCĖ└Ėņż“ŠW├ōż╣żļöĄ╦Īż¼ĄßżßżķżņĪóESLĪ╩electronic system levelĪ╦ż╚Ō}żążņżļCĖ└Ėņ└▀╝Ŗż¼żŌżŲżŽżõżĄżņżŲżŁż┐ĪŻ

ESLż“╗╚ż©żąĪó├Ļō■┼┘ż¼╣Ōż▐żĻĪóź│Ī╝źŪźŻź¾ź░ż“Š»ż╩ż»żŪżŁżļż┐żßĪó└▀╝Ŗ╗■┤ųżŌĖĪŠ┌╗■┤ųżŌø]ż»ż╩żļĪŻż│ż╬żĶż”ż╩╣ŌĮĖ└čż╩SoCżŽ─╠┐«źżź¾źšźķĄĪ▀_żõ▓ĶćĄĮĶ═²Īó▒¦├ĶÆņȧĄĪ▀_ż╩ż╔ż╬▒■├ōż╦╗╚ż’żņżŲżżżļĪŻ

ż│żņż▐żŪż╬źßź¾ź┐Ī╝ż╬ESLź─Ī╝źļżŪżóżļCatapult C SynthesisżŪżŽĪóŲŌŗźųźĒź├ź»ż╬öUĖµĪó╩Ż┐¶źųźĒź├ź»ż╬źŪĪ╝ź┐źšźĒĪ╝öUĖµż╦┤žżĘżŲżŽCĖ└Ėņ└▀╝Ŗż¼Įą═ĶżŲżżż┐ĪŻ║ŻövĪóCatapult C Synthesisż╬│╚─źż╦żĶż├żŲĪ󟻟Ēź├ź»żŪ┐«ęÄż“öUĖµż╣żļŲ▒┤³╝░ż“╗╚żżż╩ż¼żķ│░ŗźųźĒź├ź»ż▐żŪżŌöUĖµż╣żļżĶż”ż╦CĖ└ĖņĪ╩C++źĮĪ╝ź╣Ī╦żŪ£½┐ā┼¬ż╦─Ļ▒IżŪżŁżļżĶż”ż╦ż╩ż├ż┐ĪŻźóĪ╝źėź┐Ī╝ż“╗╚ż├żŲźĖźńźųż╬═ź└ĶĮń░╠ż“ż─ż▒żļŠņ╣ńĪóźŪĪ╝ź┐ż“ŲDżĻż╦╣įż»ż╬ż½┬įż┐ż╗żļż╬ż½ż“╚Įéāż╣żļż╩ż╔Ī󟻟Ēź├ź»┤žĘĖż“╔ĮĖĮżŪżŁżļż╚źßź¾ź┐Ī╝żŽĖ└ż”ĪŻÉ║öü┼¬ż╦C++źĮĪ╝ź╣ż“ż╔ż”╔ĮĖĮż╣żļż╬ż½ż╦ż─żżżŲżŽĖ└Ą┌żĘż╩żżż¼ĪóŲ▒┤³öUĖµ▓─ē”ż╩C++ż╬╗┼┴╚ż▀ż“─¾ČĪż╣żļĪóż╚źßź¾ź┐Ī╝Ī”ź░źķźšźŻź├ź»ź╣Ī”źĖźŃźčź¾ż╬źŲź»ź╦ź½źļĪ”ź╗Ī╝źļź╣╦▄ŗźĘź╦źóźóźūźĻź▒Ī╝źĘźńź¾ź©ź¾źĖź╦źóż╬┼ŽŅĄ├ęŠ╝Ģ■żŽĮęż┘żļĪŻ

Ų▒┤³öUĖµ▓─ē”ż╩C++ż╬╗┼┴╚ż▀ż╦ż─żżżŲÉ║öü┼¬ż╩Š▄║┘ż╦ż─żżżŲ┐©żņż╩żżż¼ĪóöUĖµź┴źŃź¾ź═źļż“╩¼┤¶ż╣żļż│ż╚Ī󿥿ķż╦ź»źĒź├ź»ż╦żĶżļź│ź¾ź╚źĒĪ╝źļźµź╦ź├ź╚ż╚ĪóźŪĪ╝ź┐ż╦żĶżļźóźļź┤źĻź║źÓĮĶ═²ż╚ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“Ų│Ų■Īó╣ń└«ż╣żļĪóż╚żĘżŲżżżļĪŻ

CĖ└ĖņĄŁĮęż½żķRTLż“╣ń└«ż╣żļż└ż▒żŪżŽż╩ż»ĪóĖĪŠ┌żõźŪźąź├ź░żŌżŪżŁżļżĶż”ż╩┤─ČŁż“║Ņż├ż┐ĪŻÖ┌└«żĄżņż┐RTLż“ĖĪŠ┌ż╣żļĪŻRTLŲ░║Ņż╚C++źĮĪ╝ź╣ż╬źąź├ź»źóź╬źŲĪ╝ź╚ż“╣įżżĪóźĮĪ╝ź╣ź│Ī╝ź╔ż╬źŪźąź├ź░ż“╣įż”ĪŻ

║ŻövĪóź│ź¾ź╚źĒĪ╝źļövŽ®ż▐żŪCĖ└Ėņ└▀╝Ŗż¼żŪżŁżļżĶż”ż╦ż╩ż├ż┐ż│ż╚żŪĪóźšźļź┴ź├źūż╬╣Ō░╠╣ń└«ż¼▓─ē”ż╦ż╩żļż└ż▒żŪżŽż╩ż»Īó─ŃŠ├õJ┼┼╬ü└▀╝ŖżŌżŪżŁżļżĶż”ż╦ż╩żļĪŻÉ║öü┼¬ż╦żŽź»źĒź├ź»ź▓Ī╝źŲźŻź¾ź░ż╬┘UŲ■▓─ē”ż╩ŠņĮĻż“śOŲ░┼¬ż╦Ė½ż─ż▒żķżņżļż┐żßĪóŠ}T┘ćż¼╔į═ūż╦ż╩żļĪŻż▐ż┐ĪóövŽ®źųźĒź├ź»ż╬Ų░║ŅėX▌åż“Ū─É█żĘĪóż╔ż╬övŽ®ż¼┘Vż▐ż├żŲżżżļż½ż“─╠ē¶ż╣żļż┐żßż╬źšźķź░ż“╣ń└«ż╣żļż│ż╚żŌżŪżŁżļĪŻ

źßź¾ź┐Ī╝żŽĪóż│ż╬ź─Ī╝źļż╬│╚─ź╚Ūż“ĮjŠ}╚ŠŲ│öüźßĪ╝ź½Ī╝ż╦╝┬Š┌żĘżŲżŌżķż├żŲż¬żĻĪó×æēäż╚żĘżŲż╬▐k╚╠▌xŠņżžż╬─¾ČĪżŽŃQŲŌż▐żŪż╦╣įż”═Į─Ļż╦ż╩ż├żŲżżżļĪŻ