EDAż╬║YØŹ▓Į├─öüAccellera Systems Initiativeż╦Ė½żļ╣±║▌║YØŹ▓Įż╬Š}╦Ī

EDAż╬║YØŹ▓Įż“┐╩żßżŲżżżļä▌╣±ż╬├─öüAccelleraż╚ĪóCĖ└Ėņź┘Ī╝ź╣ż╬VLSI└▀╝Ŗź─Ī╝źļż“║YØŹ▓ĮżĘżĶż”ż╚ż╣żļ├─öüOSCIĪ╩Open SystemC InitiativeĪ╦ż¼2011ŃQ12ĘŅż╦╣ń±éżĘż┐ĪŻ╣ŌĮĖ└čż╬VLSIż“─Ńź│ź╣ź╚Ī”ø]Ū╝┤³żŪ└▀╝Ŗż╣żļż┐żßż╦║YØŹ▓ĮżŽ’L(f©źng)ż½ż╗ż╩żżĪŻ╣±║▌║YØŹ▓Įż╬żõżĻöĄ(sh©┤)ż“ż│ż╬╬ŃżŪŠę▓żĘżĶż”ĪŻŲ³ä▌┤ųżŪSkypeźżź¾ź┐źėźÕĪ╝żĘż┐ĪŻ

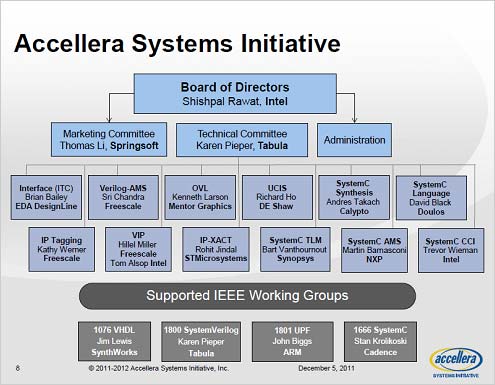

┐▐1ĪĪAccellera Systems Initiative▓±─╣ż╬Shishpal RawatĢ■Ī╩Intel╝ęĪ╦

║YØŹ▓Į├─öüż╚żĘżŲIEEEż¼Ń~ć@żŪżŽżóżļż¼ĪóŲ░żŁż¼ęÆżżĪŻż│ż╬ż┐żßAccelleraż╚żżż”├─öüż¼Ö┌ż▐żņż┐ĪŻ║YØŹ▓Įż╬ÅBżĘ╣ńżżż“IEEEż└ż╚2Ī┴3ź§ĘŅż╦1öv│½ż»ż└ż▒ż╩ż╬żŪĪó║ŪĮ¬░Ųż▐żŪĄ═żßżŲżżż»ż╬ż╦2Ī┴3ŃQż½ż½ż├żŲżĘż▐ż”ĪŻĪųAccellerażŽź▄źķź¾źŲźŻźóź┘Ī╝ź╣ż╬║YØŹ▓Į├─öüĪūĪ╩Accellera Systems Initiative▓±─╣ż╬Shishpal RawatĢ■Īó┐▐1Ī╦żŪĪóIEEE║YØŹ▓Į░čµ^▓±ż╦└ĶŅ~ż▒żŲ└▀╝ŖĖ└ĖņĪóĖĪŠ┌ź─Ī╝źļĪóIP└▀╝Ŗ╗┼══ż╩ż╔ż╬║YØŹ▓Įż“┐╩żßżŲżżż»ĪŻ╦ĶĘŅ1Ī┴2öv▓±Ą─ż“│½żŁĪó║YØŹ▓Įż╣żļż┐żßż╬╠õ¼ö┼└ż“¹ÉżżĮążĘ▓“»éżĘżŲżżż»ĪŻ║ŪŖZżŪżŽAccellerażŪ»éż▐ż├ż┐║YØŹ▓Į░Ųż“IEEEż╦─¾░ŲżĘĪóńRŪ¦ż“żŌżķż”ż│ż╚żŪ║YØŹ▓Įż“▓├Å]żĘżŲżżżļĪŻ

źÓĪ╝źóż╬╦Īō¦ż╚Č”ż╦VLSIż¼╣ŌĮĖ└čż╦ż╩żĻVHDLżõVerilogżŪż╬└▀╝ŖżŪżŽż╩ż»ĪóCĖ└Ėņź┘Ī╝ź╣żŪźĘź╣źŲźÓĄĪē”ż╬├Ļō■(j©┤)┼┘ż“╣ŌżßĪó└▀╝Ŗż╚ĖĪŠ┌ż“│┌ż╦żĘżĶż”ż╚żżż”ESLĪ╩electronic system levelĪ╦└▀╝ŖŠ}╦Īż¼īÖ╚»ż╦ż╩ż├żŲżżżļĪŻOSCIżŽż│ż╬ESL└▀╝ŖŠ}╦Īż╬║YØŹ▓Įż“┐╩żßżŲżŁż┐├─öüżŪĪóSystemCżõSystemC TLMĪóSystemC AMSż╩ż╔ż╬║YØŹ▓Įż╦╬üż“ÅRżżżŪżżżļĪŻ

║ŻövĪóOSCIż¼Accelleraż╚╣ń±éż╣żļż│ż╚żŪ┐ʿʿż┴╚“EĪóAccellera Systems Initiativeż¼Ö┌ż▐żņż┐ĪŻźĘź╣źŲźÓźņź┘źļż╬└▀╝ŖżõIPż“żżżĒżżżĒż╩ź─Ī╝źļżõ┤─ČŁżŪ└▀╝ŖżŪżŁżļżĶż”ż╦║YØŹ▓ĮżĘżŲżżżņżąĪóż│żņż▐żŪżĶżĻżŌ┴ßż»╝┬ĖĮżŪżŁżļżĶż”ż╦ż╩żļĪŻż│ż╬±T▓╠Īó└▀╝Ŗż╬Ö┌ŠÅ└Łż¼æųż¼żĻĪó┴╚ż▀╣■ż▀źĘź╣źŲźÓżõSoCż╬└▀╝Ŗ╗■┤ųż¼ø]Į╠żĘĪó×æēä▓Įż“┴ßżßżļż│ż╚ż¼żŪżŁżļĪŻØŖż╦Ī󿥿▐żČż▐ż╩Īų?j©½n)?sh©┤)Ė└Īūż“Ęeż─CÅUż╬Ė└Ėņż“║YØŹ▓Įż╣żļż│ż╚żŪĪóźÓĪ╝źóż╬╦Īō¦ż“żĄżķż╦┐õżĘ┐╩żßżļż│ż╚ż¼▓─ē”ż╦ż╩żļĪŻ

ESL└▀╝ŖŠ}╦Īż¼║YØŹ▓ĮżĄżņżŲČ”─╠ż╦╗╚ż©żļż╬ż╩żķĪóźšźĪźųźņź╣╚ŠŲ│öüż└ż▒żŪżŽż╩ż»ĪóźĄĪ╝ź╔źčĪ╝źŲźŻżŌ└▀╝Ŗ║ŅČ╚ż╦╗▓▓├żŪżŁżļĪŻIDMżõźšźĪźųźņź╣źßĪ╝ź½Ī╝żŽźĄĪ╝ź╔źčĪ╝źŲźŻż╦ESL└▀╝Ŗż“░══ĻżĘżŲĪóśOżķżŽįu┴Tż╩╩¼╠Ņż╦ĮĖ├µżŪżŁżļĪŻź─Ī╝źļż╬║YØŹ▓ĮżŽźĄĪ╝ź╔źčĪ╝źŲźŻżŌ╦▄┼÷ż╦╗╚ż©żļż½ż╔ż”ż½Īóźżź¾ź┐Ī╝ź¬ź┌źķźėźĻźŲźŻĪ╩InteroperabilityĪ¦┴ĻĖ▀▒┐├ō└ŁĪ¦║YØŹ▓ĮżĄżņż┐×æēäżŪżŌA╝ęż½żķZ╝ęż▐żŪż╔ż╬┤ļČ╚żŌ╗╚ż©żļż│ż╚ż“│╬Ū¦ż╣żļ║ŅČ╚Ī╦żŌ─_═ūżŪżóżļĪŻ║YØŹ▓ĮżĘżŲżŌ┬Š╝ęż¼╗╚ż©ż╩ż▒żņżą┴T╠Żż¼ż╩żżż½żķż└ĪŻ

AccellerażŽż│żņż▐żŪżŌźóź╩źĒź░żõź▀ź»ź╣ź╚źĘź░ź╩źļövŽ®ż“VerilogżõSystemCż╦│╚─źż╣żļż┐żßż╬║YØŹ▓Į║ŅČ╚żŌ╣įż├żŲżŁż┐ĪŻVerilog-AMSżŽĖĮ║▀┐╩╣į├µż╬ź▀ź»ź╣ź╚źĘź░ź╩źļĖ■ż▒║YØŹ▓ĮĖ└Ėņż╬▐kż─żŪżóżļĪŻĖĮ║▀żŽż│żņżŌ┤▐żßØ▓┐¶ż╬╗┼══ż╬║YØŹ▓Įż“Ų▒╗■╩┬╣įżŪ┐╩żßżŲżżżļĪŻĪųż’żņż’żņżŽ═ź└ĶĮń░╠ż“¤²ż▒ż║Īóż╣ż┘żŲż╬║YØŹ▓Į║ŅČ╚ż“Ų▒╗■╩┬╣įżŪżõż├żŲżżż»Īūż╚▓±─╣ż╬Shishpal RawatĢ■żŽĖ└ż”ĪŻ

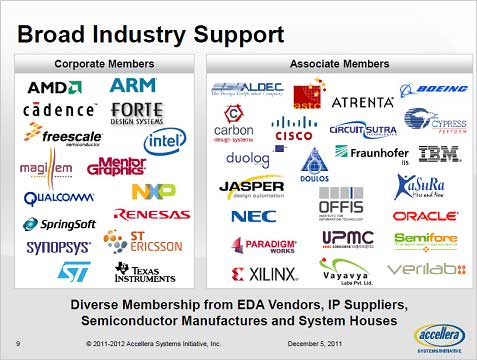

Accelleraż╬źßź¾źąĪ╝ż╦źšźĪź”ź¾ź╔źĻźßĪ╝ź½Ī╝żŽż▐ż└żżż╩żżĪŻAccellerażŪżŽVHDL/Verilogż½żķGDS-IIĮą╬üż▐żŪż╬║YØŹ▓Į║ŅČ╚ż“░Ęż”ż┐żßĪóźżź¾źŲźļżõAMDż╩ż╔ż╬IDMżõź»źóźļź│źÓżõSTź©źĻź»źĮź¾ż╩ż╔ż╬źšźĪźųźņź╣ĪóARMż╬żĶż”ż╩IPź┘ź¾ź└Ī╝Īóź▒źżźŪź¾ź╣żõźßź¾ź┐Ī╝ż╬żĶż”ż╩EDAź┘ź¾ź└Ī╝ż╩ż╔ż╬╚ŠŲ│öü┤žŽó┤ļČ╚ż╚Īóź▄Ī╝źżź¾ź░żõźĘź╣ź│Ī󟬟ķź»źļż╩ż╔ż╬źĘź╣źŲźÓ┤ļČ╚ż╩ż╔ż¼źßź¾źąĪ╝żŪżóżļĪ╩┐▐2Ī╦ĪŻŲ³╦▄┤ļČ╚ż╚żĘżŲźļź═źĄź╣ż╚NECż¼źßź¾źąĪ╝ż╦╗▓▓├żĘżŲżżżļż¼Īó▒┐▒─░čµ^ż╦Ų³╦▄┤ļČ╚żŽ1╝ężŌż╩żżĪ╩┐▐3)ĪŻ

┐▐2ĪĪAccellera Systems Initiativeż╬źßź¾źąĪ╝

┐▐3ĪĪAccellera Systems Initiative▒┐▒─░čµ^

Accelleraż╬║YØŹ▓Į║ŅČ╚żŽĪó╦ĶĮĄż╬żĶż”ż╦▓±Ą─ż“│½żŁĪ󿥿▐żČż▐ż╩╗┼══░Ų°Pż“Ų▒╗■╩┬╣įż╦┐╩żßżŲżżż»ĪŻ╗▓▓├źßź¾źąĪ╝żŽä▌╣±┤ļČ╚ż└ż▒żŪżŽż╩żżĪŻ▒č╣±Īóź╣źżź╣Ī󱜎čĪóź╔źżź─ĪóŲ³╦▄Īóźżź¾ź╔ż╩ż╔ż╬╣±ż╬┤ļČ╚ż¼źßź¾źąĪ╝ż╦ż╩ż├żŲżżżļĪŻ║YØŹ▓Į║ŅČ╚ż╦żŽ║ŪĮķż½żķź░źĒĪ╝źąźļż╩źßź¾źąĪ╝ż“ĮĖżßĪó╦ĶĘŅ1Ī┴2övż╬ź┌Ī╝ź╣żŪÅBżĘ╣ńżżĪó┘ć╝░ż╦IEEEż╩ż╔ż╦─¾░Ųż╣żļż│ż╚żŪĪó┴TĖ½ż¼ż▐ż╚ż▐ż├żŲżżżļż┐żßź╣źÓĪ╝ź║ż╦»éż▐żļĪŻŲ³╦▄╣±ŲŌżŪ┤▒░cż“ĮĖżßżŲ║YØŹ▓Į░Ųż“║ŅżĻĪóIECżõIEEEż╦─¾░ŲżĘżŲżŌ│░╣±┤ļČ╚ż╦×┤żĘżŲ║¼övżĘżõ┴TĖ½ż╬ĮĖ╠¾ż¼żŪżŁżŲżżż╩ż▒żņżą╚┐×┤żĄżņżŲĮ¬ż’ż├żŲżĘż▐ż”ĪŻ║YØŹ▓Į║ŅČ╚ż╦║ŪĮķż½żķź░źĒĪ╝źąźļ┤ļČ╚ż“┤▐żßżļż│ż╚żŽżŌżŽżõź▐ź╣ź╚żŪżóżļĪŻ