ARMĪó─ŃŠ├õJ┼┼╬ü▓Įż╬┤╦▄ż“╝ķżĻĪó×æēäź▌Ī╝ź╚źšź®źĻź¬ż“│╚Įj(lu©░)

źūźĒź╗ź├źĄIPź┘ź¾ź└Ī╝ź╚ź├źūż╬ARMż¼×æēäź▌Ī╝ź╚źšź®źĻź¬ż“╣Łż▓żŲżżżļĪŻĪų▐kż─ż╬źūźĒź╗ź├źĄżŪżŽµ£żŲż╬▒■├ōż“║Ū┼¼▓ĮżŪżŁż╩żżĪūĪ╩Ų▒╝ęEmbedded Processors├┤┼÷źąźżź╣źūźņźĖźŪź¾ź╚ż╬Keith ClarkeĢ■(hu©¼)Ī╦ż½żķż└ĪŻź▐źżź│ź¾▒■├ōż╬Cortex-MźĘźĻĪ╝ź║ż╦▓├ż©ĪóĘ╚┬ėĄĪ▀_(d©ó)ż╬źóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╦Ė■ż▒ż┐big.LITTLEźóĪ╝źŁźŲź»ź┴źŃĪóźĄĪ╝źąż╩ż╔ż╬źŽźżź©ź¾ź╔źūźĒź╗ź├źĄCortex-A50źĘźĻĪ╝ź║ż╩ż╔żžż╚│╚─źżĘ¶öż▒żŲżżżļ(┐▐1)ĪŻ

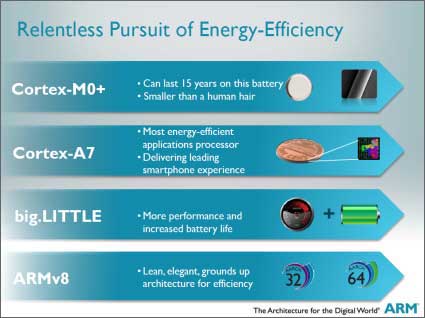

┐▐1ĪĪ«Ć─ŃŠ├õJ┼┼╬üż½żķ64źėź├ź╚źĄź▌Ī╝ź╚ż╬źŽźżź©ź¾ź╔ż▐żŪĪĪĮąųZĪ¦ARM

ż│żņżķż╬CPUźóĪ╝źŁźŲź»ź┴źŃż╦▓├ż©żŲĪóź░źķźšźŻź├ź»ź╣żŪżóżļGPUĪ╩graphic processing unitĪ╦ĪóźĘź╣źŲźÓIPĪóźšźŻźĖź½źļIPĪóźĮźšź╚ź”ź©źóż╩ż╔żžż╬│╚Įj(lu©░)żŌ┐▐ż├żŲżżżļĪŻż┐ż└żĘĪó─ŃŠ├õJ┼┼╬üż╦źšź®Ī╝ź½ź╣żĘż┐IPź┘ź¾ź└Ī╝ż╚żżż”źėźĖź═ź╣źŌźŪźļżŽ╩čż©ż╩żżĪŻ─Š└▄ż╬Ė▄ĄężŽ╚ŠŲ│öüźßĪ╝ź½Ī╝żŪżóżļĪŻ╚ŠŲ│öüż╬└Ķż╦żóżļźµĪ╝źČż“Ė½┐°ż©ż┐×æēä│½╚»└’ŠSż╬ź▌źĻźĘĪ╝żŌ═æżļż¼ż╩żżĪŻ╚ŠŲ│öüżĮż╬żŌż╬ż¼ŗēäż½żķźĘź╣źŲźÓżžż╚╩č═ŲżĘżŲżżżļż┐żßĪóź┴ź├źūż╬└Ķż╦żóżļ▒■├ōż“Ė½┐°ż©│½╚»ż╣żļż│ż╚żŪ┤ļČ╚▓┴├═ż“╣ŌżßżŲżżżļĪŻżżż»ż─ż½ż╬╬Ńż“12ĘŅż╦│½ż½żņż┐ARM Forumż½żķŠę▓ż╣żļĪŻ

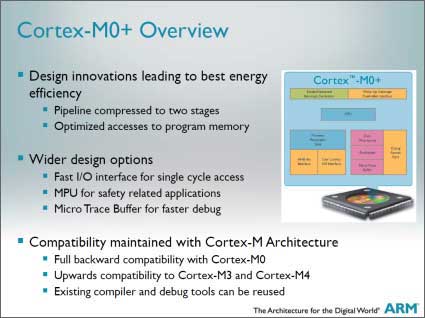

ź▐źżź│ź¾├ōż╬ź│źóCortex-M0+żŽĪ󿥿ķż╩żļ─ŃŠ├õJ┼┼╬üż“┴└ż├ż┐ź▐źżź│ź¾ż╦Ė■ż▒ż┐żŌż╬ĪŻCR2032ż╬ź▄ź┐ź¾┼┼├ė1Ė─żŪ15ŃQ┤ųŲ░║ŅżĄż╗żļż╚żżż”ų`║Yż“└▀─ĻżĘżŲżżżļĪŻż│ż╬Š“°PżŽĪóźŪźÕĪ╝źŲźŻ╚µ1%ĪóTSMCż╬90LPźūźĒź╗ź╣Ī╩─ŃŠ├õJ┼┼╬üż╬90nmĪ╦żŪ║ŅżļŠņ╣ńż╦┼÷żŲżŽż▐żļĪŻż│ż╬ų`║Yż│żĮĪóIOTĪ╩internet of thingsĪ╦żžż╬▒■├ōż“┴└ż├ż┐żŌż╬ż╚żżż©żļĪŻ

IOTżŽµ£żŲż╬źŌź╬ż¼źżź¾ź┐Ī╝ź═ź├ź╚żŪż─ż╩ż¼żļż╚żżż”▄ćŪ░ż└ĪŻZigBeeż╩ż╔ż╬─ŃŠ├õJ┼┼╬üźūźĒź╚ź│źļż“ź┘Ī╝ź╣ż╚ż╣żļź’źżźõźņź╣ź╗ź¾źĄź═ź├ź╚ź’Ī╝ź»ż½żķ┐╩·tżĘżŲżŁżŲżżżļĪŻŽė╗■╝ŖżõÅž∙iĪóźĮĪ╝źķĪ╝źĘź╣źŲźÓĪóśOŲ░╚╬ŪõĄĪĪóźņź¾ź┐źļĘ·ĄĪĪóź╚źķź├ź»żõźąź╣ĪóŠ╚£½▀_(d©ó)É║ż╩ż╔żóżĻż╚żóżķżµżļźŌź╬ż¼źżź¾ź┐Ī╝ź═ź├ź╚ż╚ż─ż╩ż¼żĻĪóżĮżņżķż╬ėX(ju©”)▌åż“źŌź╦ź┐Ī╝ż╣żļĪŻČČ£žżõÜłæčż╬żšżŌż╚ż╩ż╔ż╦ź’źżźõźņź╣ź╗ź¾źĄź═ź├ź╚ź’Ī╝ź»ż“╣Į├█ż╣żļ╗Ņż▀żŽż╣żŪż╦╣įż’żņżŲżżżļĪŻ╦╔¤ßź½źßźķż“źżź¾ź┐Ī╝ź═ź├ź╚ż╦ż─ż╩ż▓żąĪó═▐┘V╬üżŽ║Ż░╩æųż╦╣Ōż▐żļĪŻź╚ź¾ź═źļŲŌż╬ÜW░µłżõ╩╔ż╩ż╔ż╦ź╗ź¾źĄż“¤²ż▒ĪóŠ’╗■źŌź╦ź┐Ī╝ż╣żļżĶż”ż╩▒■├ōżŌ╣═ż©żķżņżŲżżżļĪŻ

┐ʿʿżCortex-M0+ż¼┴└ż”ź▐źżź│ź¾▒■├ōżŪżŽĪó│õżĻ╣■ż▀ĮĶ═²ż¼└õż©ż║╣įż’żņĪóżĘż½żŌź╣źĻĪ╝źūėX(ju©”)▌åżŌ¾HżżĪŻ│õżĻ╣■ż▀╠┐╬ßż¼═Ķż┐ĖÕż╣ż░ż╦żĮż╬╗┼Ą£ż“ĮĶ═²żŪżŁżļżĶż”ż╦ż╣żļż┐żßĪó│õżĻ╣■ż▀ź│ź¾ź╚źĒĪ╝źķż“Į╝╝┬żĄż╗Ī╩┐▐2Ī╦ĪóżĘż½żŌźčźżźūźķźżź¾ż╬╦▄┐¶ż“2├╩ż╦žō(f©┤)żķżĘż┐ĪŻźčźżźūźķźżź¾ĮĶ═²żŪ─╣żż┤ų┬įż┐żĄżņżļż│ż╚Ī╩źņźżźŲź¾źĘĪ╦ż“╦╔ż░ż┐żßż└ĪŻ▓├ż©żŲźūźĒź░źķźÓźßźŌźĻżžż╬źóź»ź╗ź╣żŌ║Ū┼¼▓ĮżĘżŲżżżļĪŻ┴Ū┴ßż»╬®ż┴æųż¼żļżĶż”ż╦źĘź¾ź░źļźĄźżź»źļżŪŲ░║ŅżŪżŁżļ╣ŌÅ]I/Oźżź¾ź┐Ī╝źšź¦Ī╝ź╣żŌ└▀ż▒żŲżżżļĪŻżŌż┴żĒż¾“£═Ķż╬Cortex-M0żõCortex-M3ż╚ż╬æų░╠Ė▀┤╣└Łż¼żóżĻĪó┘J┘Tż╬ź│ź¾źčźżźķżõźŪźąź├ź░ź─Ī╝źļżŌ╗╚ż©żļĪŻ

┐▐2ĪĪIOTĖ■ż▒ż╬ź▐źżź│ź¾ź│źóCortex-M0+ĪĪĮąųZĪ¦ARM

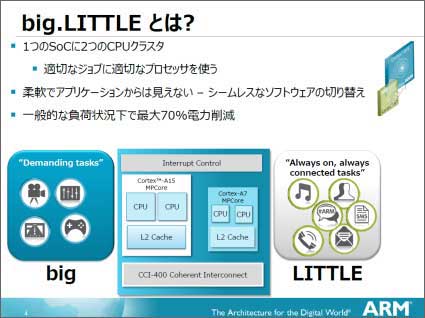

ARMż╬┤╦▄Ž®└■żŪżóżļźŌźąźżźļ▒■├ōżŪżŽĪóź┐źųźņź├ź╚żõź╣ź▐ź█ż¼─ŃŠ├õJ┼┼╬üż╩ż¼żķ╣Ō└Łē”ż¼ĄßżßżķżņżļżĶż”ż╦ż╩ż├żŲżŁż┐ż┐żßĪóż│żņżķż“źĘź╣źŲźÓ┼¬ż╦╬Š╬®żĄż╗żļż┐żßż╬big.LITTLEźóĪ╝źŁźŲź»ź┴źŃ(┐▐3)ż╬╝┬╬Ńż¼ĮążŲżŁż┐ĪŻż│żņżŽĪó╣Ō└Łē”ż╩CPUź│źóż╚─ŃŠ├õJ┼┼╬üż╬ź│źóż“1ź┴ź├źūæųż╦┼ļ║▄żĘĪóź┐źųźņź├ź╚ż╩ż╔ż╬ŠW(w©Żng)├ōėX(ju©”)▌åż╦▒■żĖżŲźūźĒź╗ź├źĄż“└┌żĻü÷ż©żļż│ż╚żŪŠ├õJ┼┼╬üż“║Ū┼¼▓Įż╣żļżŌż╬żŪżóżļĪŻ╬Ńż©żąĪóźėźŪź¬żõź▓Ī╝źÓĪóźųźķź”źĖź¾ź░ż╩ż╔╚µ│ė┼¬─_żżĮĶ═²ż╦żŽźŽźżź©ź¾ź╔ż╬Cortex-A15źŪźÕźóźļź│źóĪ╩bigĪ╦ż“╗╚żżĪóźßĪ╝źļżõSMSż╩ż╔Š’╗■└▄¶öżŪĘ┌żżĮĶ═²ż“ż╣żļż╚żŁż╦żŽCortex-A7źŪźÕźóźļź│źóĪ╩LITTLEĪ╦ż“╗╚ż”ĪŻCortex-A15źŪźÕźóźļź│źóżŽĖĮ║▀ż╬ź╣ź▐ź█ż╦Ų■ż├żŲżżżļźūźĒź╗ź├źĄż╬5Ū▄ż╬└Łē”żŪĪóCortex-A7źŪźÕźóźļź│źóżŪżŌĖĮėX(ju©”)źūźĒź╗ź├źĄżĶżĻżŌ╣Ō└Łē”ż└ż╚żĘżŲżżżļĪŻ

┐▐3ĪĪ└Łē”ż“░▌ĘeżĘż╩ż¼żķŠ├õJ┼┼╬üż“▓╝ż▓żķżņżļbig.LITTLEźóĪ╝źŁźŲź»ź┴źŃĪĪĮąųZĪ¦ARM

żĮżņżŠżņż╬źŪźÕźóźļź│źóż½żķż╩żļCPUź»źķź╣ź┐ż╦żŽL2źŁźŃź├źĘźÕźßźŌźĻż“┤▐ż¾żŪż¬żĻ(┐▐3)ĪóĘQCPUźĘź¾ź░źļź│źóŲ▒╗╬ż╬źßźŌźĻĪ╝ź│źęĪ╝źņź¾źĘż“╩▌ż├żŲżżżļĪŻżĄżķż╦Cortex-A7ż╚Cortex-A15ż╬CPUź»źķź╣ź┐Ų▒╗╬ż╬źŁźŃź├źĘźÕź│źęĪ╝źņź¾źĘżŌ│╬╩▌ż╣żļż┐żßż╬CCI-400źąź╣żŌ└▀ż▒żŲżżżļĪŻźŁźŃź├źĘźÕź│źęĪ╝źņź¾źĘżŽĪóźūźĒź╗ź├źĄż¼╩čż’ż├żŲżŌźŁźŃź├źĘźÕŲŌ═Ųż╬Ų▒▐k└Łż“╩▌ż─ż┐żßż╬╗┼┴╚ż▀żŪżóżļĪŻ

ź╣ź▐ź█żŪź”ź¦źųźųźķź”źĖź¾ź░ż“żĘżŲżżżļ╗■ż╦┼┼ÅBż¼ż½ż½ż├żŲż»żļżĶż”ż╩ėX(ju©”)ČĘżŽĪó│õżĻ╣■ż▀ĮĶ═²ż¼Ų■żļųZĘ┐╬ŃżŪżóżļĪŻż│ż╬big.LITTLEż╬źĮźšź╚ź”ź©źóżŪżŽĪóGIC-400│õżĻ╣■ż▀ź│ź¾ź╚źĒĪ╝źķż╦żĶż├żŲĪó│õżĻ╣■ż▀ż¼Ų■żļż╚źūźĒź╗ź├źĄ╔ķ▓┘ż╦×┤żĘżŲ┼¼└┌ż╩CPUżž?c©ói)Ī╣įż╣żļĪŻżĄżķż╦ź╣źņź├ź╔├▒░╠żŪ║Ū┼¼ż╩CPUż“│õżĻ┼÷żŲżļżĶż”ż╦ź╣ź▒źĖźÕĪ╝źķż¼╝┬ä󿥿ņżŲżżżļĪŻż│ż╬ź╣ź▒źĖźÕĪ╝źķżŽĪó│õżĻ╣■ż▀ż¼ż╩żżŠņ╣ńżŪżŌ╔ķ▓┘ż╦▒■żĖżŲ┼¼└┌ż╩CPUżõź»źķź╣ź┐ż“┬ō(li©ón)┘Iż╣żļĪŻ

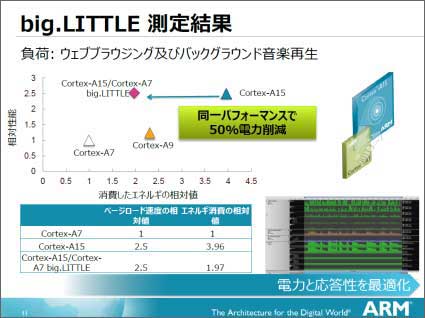

źųźķź”źĖź¾ź░żĘż╩ż¼żķ▓╗│┌ż“─░ż»ż╚żżż”▒■├ōżŪżŽĪóbig.LITTLEźóĪ╝źŁźŲź»ź┴źŃżŽCortex-A15ż└ż▒żŪĮĶ═²ż╣żļŠņ╣ńż╚╚µż┘ĪóŲ▒żĖ└Łē”ż“│╬╩▌żĘż╩ż¼żķŠ├õJ┼┼╬üżŽ╚Šžō(f©┤)żĘżŲżżżļĪ╩┐▐4Ī╦ĪŻ

┐▐4ĪĪbig.LITTLEżŽŲ▒żĖ└Łē”żŪŠ├õJ┼┼╬üż“╚Šžō(f©┤)ĪĪĮąųZĪ¦ARM

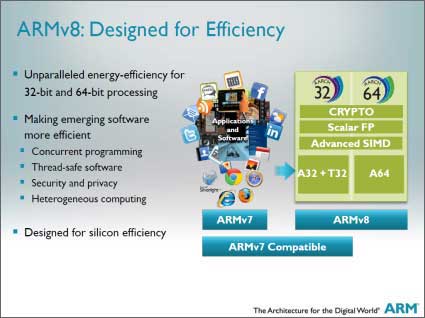

ARMżŽż│żņż▐żŪ║Ū╣Ōż╬└Łē”ż“ĖžżļCPUźóĪ╝źŁźŲź»ź┴źŃARMv8ż╦ż─żżżŲżŌ╚»╔ĮżĘż┐ĪŻ32źėź├ź╚źĘź╣źŲźÓż╩ż¼żķ64źėź├ź╚żŌźĄź▌Ī╝ź╚żĘĪóSIMDĪ╩single instruction multiple dataĪ╦źóĪ╝źŁźŲź»ź┴źŃż“Ų¦¬ä(ji©Żng)żĘż╩ż¼żķĪó╣ŌÅ]ż╬░┼ęÄ(gu©®)▓ĮĮĶ═²Īó╔ŌŲ░Š«┐¶┼└▒ķōQĄĪē”żŌ┼ļ║▄żĘżŲżżżļ(┐▐5)ĪŻARMv8źóĪ╝źŁźŲź»ź┴źŃż╬źŽźżź©ź¾ź╔źūźĒź╗ź├źĄż╬╬Ńż╚żĘżŲĪóCortex-A50źĘźĻĪ╝ź║ż“11ĘŅż╦╚»╔ĮżĘż┐ż¼Īóż│ż╬ż█ż╔żĮż╬Š▄║┘żŌ£½żķż½ż╦żĘż┐ĪŻ

┐▐5ĪĪźŽźżź©ź¾ź╔ż╬ARMv8źóĪ╝źŁźŲź»ź┴źŃĪĪĮąųZĪ¦ARM

A50źĘźĻĪ╝ź║ż╬║ŪĮķż╬×æē俎Ī󟎟żź©ź¾ź╔ż╬Cortex-A57ż╚Cortex-A53żŪżóżļĪŻA57żŽĪóĖĮ║▀ż╬ź╣ź▐ź█ż╚Ų▒żĖŠ├õJ┼┼╬üżŪ└Łē”żŽ3Ū▄Īóź┐źųźņź├ź╚żõź╬Ī╝ź╚PCĖ■ż▒ż╬źŌźąźżźļź│ź¾źįźÕĪ╝źŲźŻź¾ź░ē”╬üżŪ5Ū▄ż╚żżż”ĪŻżĄżķż╦64źėź├ź╚ż“źĄź▌Ī╝ź╚żĘĪó║ŪĮj(lu©░)16ź│źóż▐żŪĮĖ└č▓─ē”Īóż╚żĘżŲżżżļĪŻA53żŽCortex-A9ż╚Ų▒żĖ└Łē”żŪŠ├õJ┼┼╬üż¼40%żŪż╣żÓĪóź┴ź├źūĀC└迎25%║’žō(f©┤)żĘżŲżżżļĪ╩A9ż¼32nmż╚żĘżŲA53żŽ20nmĪ╦ĪŻ

FINFETż“ŠW(w©Żng)├ōż╣żļ10nm±śż╬źūźĒź╗ź╣Č\Įčż╦┤žżĘżŲżŌĪóTSMCż╚żŽ16nmĪóGlobalFoundriesż╚żŽ14nmż╬FINFETźūźĒź╗ź╣ż“│½╚»├µż└ĪŻż│żņż╦żĶżĻźšźŻźĖź½źļIPĪ╩Įą╬üż¼GDS IIż╬ź▐ź╣ź»źŪĪ╝ź┐Ī╦ż“─¾ČĪż╣żļżĶż”ż╦ż╩żļĪŻ