100GbpsźĘź╣źŲźÓĖ■ż▒ź┴ź├źū└▀╝Ŗż“═Ų░ūż╦ż╣żļTabulaż╬▓Š„[3╝ĪĖĄFPGA

ä▌╣±żŪż╣żż└▒ż╬żĶż”ż╦┼ąŠņżĘż┐3╝ĪĖĄFPGAż╬ź┘ź¾ź┴źŃĪ╝ĪóTabula╝ęĪ╩╗▓╣═½@╬┴1Ī╦ż¼ż│ż╬ż█ż╔żĮż╬┐╩·tėXČĘż“£½żķż½ż╦żĘż┐ĪŻ22nmż╬źżź¾źŲźļż╬ź╚źķźżź▓Ī╝ź╚FETČ\Įčż“╗╚ż”Īóż│ż╬FPGAż╬É║öü┼¬ż╩×æēäABAX2 PźĘźĻĪ╝ź║ż╚ĪóźµĪ╝źČĪ╝ż¼┐Ęæä│½╚»ż╣żļż┐żßż╬źūźĒź░źķźÓź─Ī╝źļż╬Stylusź│ź¾źčźżźķż“╚»╔ĮżĘż┐ĪŻ

┐▐1ĪĪ12Ī▀10Gbpsż½żķ100Gbpsżžż╬╩č┤╣źųźĻź├źĖĪĪĮąųZĪ¦Tabula

Tabula╝ęż╬3╝ĪĖĄFPGAČ\Į迎ĪóŠ«żĄż╩FPGAźūźņĪ╝ź¾ż“├ōżżżŲĪ󿥿ķż╦ĮjżŁż╩źĒźĖź├ź»ź▓Ī╝ź╚ż╬övŽ®ż“╗■╩¼│õżŪŠ├żĘżŲżŽ║Ų╣Į└«ż“Ę½żĻ╩ųż╣żŌż╬żŪżóżļĪŻź┴ź├źūĀC└čż¼Š«żĄż»ż╩żļż╚żżż”źßźĻź├ź╚żŽĖĄĪ╣żóż├ż┐ż¼ĪóżĮżņ░╩æųĮjżŁż╩źßźĻź├ź╚żŌżóżļĪŻź┴ź├źūŲŌŪ█└■ęÆūāż“═▐ż©żķżņżļż┐żßĪóźĒźĖź├ź»ĖĪŠ┌Īóź┐źżź▀ź¾ź░ĖĪŠ┌ż“ø]╗■┤ųżŪ║čż▐ż╣ż│ż╚ż¼żŪżŁżļĪŻ└Łē”┼¬ż╦żŌĪó╬Ńż©żąź»źĒź├ź»ż“2GHzżŪ┼²▐k┼¬ż╦Ų░║ŅżĄż╗żļż│ż╚żŌžMżĘż»ż╩żżĪŻź┴ź├źūż¼Š«żĄżżż┐żßĪóźņĪ╝źĘź¾ź░żõź»źĒź├ź»ź╣źŁźÕĪ╝ż╩ż╔ż╬╠õ¼öżŌÖ┌żĖż╦ż»żżĪŻż│ż╬ż┐żß└▀╝Ŗż½żķĖĪŠ┌ż▐żŪż╬ź┐źżź▀ź¾ź░ź»źĒĪ╝źĖźŃż¼═Ų░ūż╦ż╩żĻĪó└▀╝Ŗ┤³┤ųż╬ø]Į╠ż╦ż─ż╩ż¼żļĪŻ

ż│ż╬ź┴ź├źūż╬║ŪĮķż╬▒■├ōżŽĪó─╠┐«┤├ŽČ╔żŪż╬100GbpsźĘź╣źŲźÓż└(┐▐1)ĪŻ“£═Ķż╬Įjæä╠Žż╩FPGAżŪ100GbpsźĘź╣źŲźÓż“└▀╝Ŗż╣żļż│ż╚żŽ═Ų░ūżŪżŽż╩żżĪŻź┴ź├źūż¼żóż▐żĻż╦żŌĮjżŁżżż┐żßĪóź░źĒĪ╝źąźļŪ█└■żõźĒĪ╝ź½źļŪ█└■ż╬Čč▐k└Łż¼│╬╩▌żŪżŁż╩ż»ż╩żĻĪ󟻟Ēź├ź»ź╣źŁźÕĪ╝żõźņĪ╝źĘź¾ź░ż╩ż╔ż╬╠õ¼öż¼ĮążŲż»żļż╚Ī󟻟Ēź├ź»Å]┼┘ż“æųż▓żļż│ż╚ż¼žMżĘż»ż╩żļĪŻż│ż╬ż┐żßĪóź┴ź├źūæųż╦ź»źĒź╣źąĪ╝ź╣źżź├ź┴övŽ®ż“ĮĖ└čżĘż┐żĻĪóŲ│Ė„Ž®ż“└▀ż▒żļźĘźĻź│ź¾źšź®ź╚ź╦ź»ź╣Č\Įčż“╗╚ż├ż┐żĻż╣żļØŁ═ūż¼żóż├ż┐ĪŻżżż║żņżŌź│ź╣ź╚ż¼─Ęż═æųż¼żļöĄ╦Īż└ĪŻ

▓├ż©żŲĪó100GbpsźĘźĻźóźļ┼┴┴„ż╬└▀╝ŖżŽžMżĘżżĪŻĪųż▐ż║│░ŗż╚ż╬źżź¾ź┐źšź¦Ī╝ź╣ż“ż╚żļż┐żßż╬źķźżź¾ź┐Ī╝ź▀ź═Ī╝źĘźńź¾Ī╩┼┴┴„└■ż╬Į¬├╝Ī╦ż╬└▀╝Ŗż¼║żžMż╦ż╩żļż╚żżż”╠õ¼öż¼żóżļĪŻżŌż┴żĒż¾ź┴ź├źū│░ż╬DDR3źßźŌźĻż╚ż╬źŪĪ╝ź┐ż╬żõżĻŲDżĻż“╣įż”źąź╣ż╬źąź¾ź╔╔²ż¼ź▄ź╚źļź═ź├ź»ż╦ż╩żļĪŻź¬ź¾ź┴ź├źūźßźŌźĻż╬źąź¾ź╔╔²ż╚żĘżŲ300Gbpsµć┼┘żŽ═▀żĘżżĪŻż│ż”żżż├ż┐╣Łżżźąź╣╔²ż“│╬╩▌żĘż┐ż╚żĘżŲżŌ╣Ō└Łē”ż╩ŲŌŗźąź╣ż“░Ęż”ż┐żßż╬┐«ęÄż¼ĒšĒįż╣żļźąź╣Ēö╣ńż╬╠õ¼öżŌżóżļĪūż╚Ų▒╝ęź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷źąźżź╣źūźņźĖźŪź¾ź╚ż╬Alain BismuthĢ■żŽĖ└ż”ĪŻ

┐▐2ĪĪABAX2 P1ź┴ź├źūĪĪĮąųZĪ¦Tabula

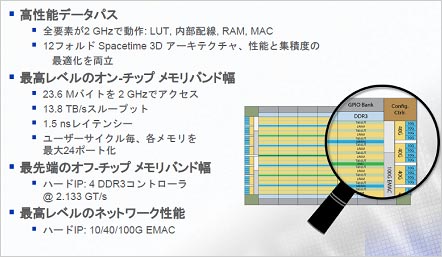

║Żövż╬ABAX2 PźĘźĻĪ╝ź║ż╦żŽĪóŲŌŗövŽ®ż╚żĘżŲĪóźĒźĖź├ź»ź╗źļżõRAMĪóMACźųźĒź├ź»ĪóŪ█└■ż╩ż╔ż“└▀ż▒żŲżżżļ(┐▐2)ż¼Īóµ£żŲż╬ź│ź¾ź▌Ī╝ź═ź¾ź╚żŽ2GHzż╬ź»źĒź├ź»żŪŖW─Ļ┼¬ż╦Ų░║ŅżĘżŲżżżļż╚żżż”ĪŻź┴ź├źūæųż╬źßźŌźĻżŽĪó12ź▌Ī╝ź╚ż╚24ź▌Ī╝ź╚ż╬I/OĪó23.3Mźąźżź╚ż╬═Ų╬╠ż“Ęeż─ĪŻźßźŌźĻż╚ż╬żõżĻŲDżĻż╦ż¬żżżŲĪó13.8Tźąźżź╚/╔├ż╚żżż”ź╣źļĪ╝źūź├ź╚ż“╝┬ĖĮżĘĪó╩Ż┐¶ż╬100Gbpsż╬«Ć╣ŌÅ]ź╣ź╚źĻĪ╝źÓż“źĄź▌Ī╝ź╚żŪżŁżļĪŻ╗■╩¼│õżŪżŁżļ║ŪĮjż╬źņźżźõĪ╝┐¶żŽ12┴žĪŻźąĪ╝ź┴źŃźļż╩3╝ĪĖĄICż╚żżż©żļĪŻ

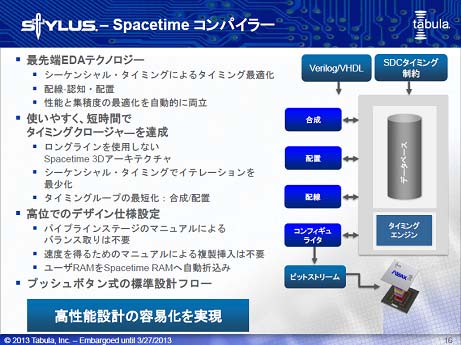

ż│ż╬FPGAż“źūźĒź░źķźÓż╣żļż┐żßż╬└▀╝Ŗź─Ī╝źļżŪżóżļStylusź│ź¾źčźżźķĪ╩┐▐3Ī╦2.6żŪżŽĪó╗■╩¼│õżŪź┐źżź▀ź¾ź░ĖĪŠ┌ż╣żļż┐żßĪóĘQ┴žż┤ż╚ż╦źĘĪ╝ź▒ź¾źĘźŃźļż╩ź┐źżź▀ź¾ź░żŪŪ█ÅøĪ”Ū█└■ż╬║Ū┼¼▓Įż“ĖĪŠ┌żŪżŁżļĪŻżĘż½żŌ─╣żżŪ█└■ż“µ£ż»ŠW├ōżĘż╩żżż┐żßĪóźĘĪ╝ź▒ź¾źĘźŃźļż╩ź┐źżź▀ź¾ź░ĖĪŠ┌żŽż’ż║ż½┐¶övż╬╚┐╔³żŪź┐źżź▀ź¾ź░ź»źĒĪ╝źĖźŃż¼▓─ē”ż╦ż╩żļĪŻRTLĮą╬üż½żķ╣ń└«ĪóŪ█Åøż▐żŪż╬ź┐źżź▀ź¾ź░źļĪ╝źūż¼ø]ż»żŲ║čżÓż┐żßż└ĪŻ

┐▐3ĪĪStylusź│ź¾źčźżźķżŪź┐źżź▀ź¾ź░ź»źĒĪ╝źĖźŃż¼į~├▒ż╦ĪĪĮąųZĪ¦Tabula

100GbpsźĘź╣źŲźÓż╬źĮźĻźÕĪ╝źĘźńź¾ż“źŪźŌż╣żļż┐żßĪóźĻźšźĪźņź¾ź╣źŪźČźżź¾źŁź├ź╚ż╦żŽĪó12Ī▀10Gbpsż½żķ100Gbpsź▌Ī╝ź╚żžż╬╩č┤╣źųźĻź├źĖ(┐▐1)żõĪó4Ī▀100Gbpsż╬ź╣źżź├ź┴ż╩ż╔5╬Ńż╬övŽ®ż“┼ļ║▄żĘżŲżżżļĪŻ

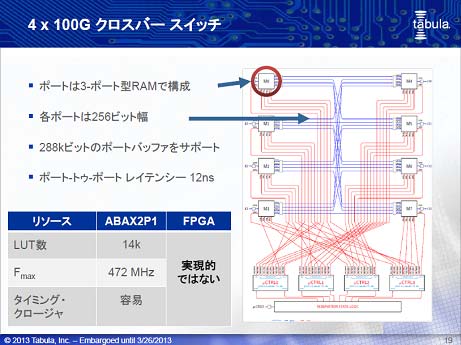

│½╚»ź─Ī╝źļStylusź│ź¾źčźżźķż“╗╚ż├żŲĪóż│ż╬ź┴ź├źūżŪ4Ī▀100Gbpsż╬ź»źĒź╣źąĪ╝ź╣źżź├ź┴ż“└▀╝ŖżĘż┐╬Ń(┐▐4)ż¼żóżļĪŻ14kĖ─ż╬LUTĪ╩źļź├ź»źóź├źūźŲĪ╝źųźļĪ╦ż“╗╚żżĪó╝■āS┐¶472MHzżŪĪó3ź▌Ī╝ź╚Īó256źėź├ź╚╔²żŪĪó288Kźėź├ź╚ż╬źąź├źšźĪRAMż“Ų░ż½ż╣ż│ż╚żŪĪó104.4Gbpsż╬źŪĪ╝ź┐źņĪ╝ź╚ż╦ż╩żļĪŻ

┐▐4ĪĪ4Ī▀100Gbpsż╬ź»źĒź╣źąĪ╝ź╣źżź├ź┴ż╬╬Ń

Stylusź│ź¾źčźżźķżŽĖĮ║▀Ų■Š}▓─ē”ż╦ż╩ż├ż┐ż¼Īóź┴ź├źūżŪżóżļABAX2 P1żŽ║ŻŃQż╬ŗī3╗═╚Š┤³ż╦źĄź¾źūźļĮą▓┘ż╬═Į─ĻżŪżóżļĪŻ

╗▓╣═½@╬┴

1. źżź¾źŲźļż╬22nmFINFETźūźĒź╗ź╣ż“źšźĪź”ź¾ź╔źĻż╚żĘżŲ╗╚ż”Tabula╝ę (2012/03/01)