3╝ĪĖĄICżõ┤łŲŌē┼ICż╬źŲź╣ź╚╦Īż╬╝ń╬«ż╦ż╩żļż½Īóźąź”ź¾ź└źĻź╣źŁźŃź¾

źąź”ź¾ź└źĻź╣źŁźŃź¾╦Īż¼BGAżõ3╝ĪĖĄICż╬źŽź¾ź└ź▄Ī╝źļż╬└▄¶öż“źŲź╣ź╚ż╣żļŠ}╦Īż╚żĘżŲĪóJPCAĪ╩Ų³╦▄┼┼╗ęövŽ®╣®Č╚▓±Ī╦źĘźńĪ╝2013żŪÅRų`żĄżņż┐ĪŻźóź¾ź╔Ī╝źļźĘź╣źŲźÓźĄź▌Ī╝ź╚ż¼└čČ╦┼¬ż╦ż│ż╬Š}╦Īż“┐õ┐╩żĘżŲżżżļż╬ż╦▓├ż©Īó╔┘╗╬─╠źżź¾ź┐Ī╝ź│ź═ź»ź╚źŲź»ź╬źĒźĖĪ╝ź║żŌĪóź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐Äó»BÄŻż╬źŲź╣ź╚ż╦ż│ż╬Š}╦Īż“╗╚ż├żŲżżż┐ż╚Įęż┘ż┐ĪŻ

┐▐1ĪĪźąź”ź¾ź└źĻź╣źŁźŃź¾╦Īż╬▄ćŠS┐▐ĪĪLSIż╚├╝╗ęż╚ż╬┤ųż╦źĒźĖź├ź»ź╗źļż“Ų■żņ├╝╗ęż╬└▄¶ö└Łż“─┤ż┘żļĪĪĮąųZĪ¦źóź¾ź╔Ī╝źļźĘź╣źŲźÓźĄź▌Ī╝ź╚

ż│żņż▐żŪĪó3╝ĪĖĄICżõ¾Hźįź¾BGAż╩ż╔źŽź¾ź└ź▄Ī╝źļżõ┼┼Č╦źįźķĪ╝ż“╗╚ż├ż┐LSIź┴ź├źūż╚┤łż╬┼┼Č╦źčź├ź╔ż╚ż╬└▄¶öż╬══╗ęż“ź┴ź¦ź├ź»żĘż┐ż»żŲżŌżŪżŁż╩ż½ż├ż┐ĪŻTEMĪ╩Ų®āįĘ┐┼┼╗ęĖ▓╚∙¬Ü(d©▓)Ī╦żŪżŌSEMĪ╩┴÷ØhĘ┐┼┼╗ęĖ▓╚∙¬Ü(d©▓)Ī╦żŪżŌ┼┼Č╦Ų▒╗╬ż¼┤░µ£ż╦└▄¶öżĄżņżŲżżżļż½ż╔ż”ż½ż“1Ė─ż║ż─ĖĪØhż╣żļż│ż╚żŽż█ż▄╔į▓─ē”ż└ż├ż┐ĪŻ

ż│ż╬ż┐żßر═²┼¬ż╦ż─ż╩ż¼ż├żŲżżżļż½Īóź¬Ī╝źūź¾ż╦ż╩ż├żŲżżżļż½Īó┼┼Ąż┼¬ż╦źŲź╣ź╚ż“ż╣żļżĘż½öĄ(sh©┤)╦Īż¼ż╩ż½ż├ż┐ĪŻ║ŻövĪóJPCAźĘźńĪ╝żŪÅRų`żĄżņż┐Č\Įčż╬▐kż─ż¼┼┼Ąż┼¬ż╦└▄¶öėX▌åż“ē¶żļż│ż╚ż¼żŪżŁżļźąź”ź¾ź└źĻź╣źŁźŃź¾╦ĪżŪżóżļ(┐▐1)ĪŻż│ż╬öĄ(sh©┤)╦ĪżŽźŲź╣ź╚═Ų░ū▓Į└▀╝ŖŠ}╦Īż╬▐kż─ż╚żĘżŲ1980ŃQ┬Õż╦─¾░ŲżĄżņż┐ż¼Īóż│żņż▐żŪżŽżóż▐żĻ╔ߥ┌żĘżŲż│ż╩ż½ż├ż┐ĪŻż┐ż└Īó╔┘╗╬─╠źżź¾ź┐Ī╝ź│ź═ź»ź╚żŽĪó1990ŃQ║óźßźżź¾źšźņĪ╝źÓź│ź¾źįźÕĪ╝ź┐ż╬źŲź╣ź╚ż½żķ╗╚ż├żŲżżż┐ż¼ĪóżĮżņ░╩æTĪó╔┘╗╬─╠╝ęŲŌż╬µ£×æēäż╦┼¼├ōżĘżŲżŁż┐ż╚Įęż┘żŲżżżļĪŻ

JPCAźĘźńĪ╝żŪÅRų`żĄżņż┐═²Įy(t©»ng)ż╚żĘżŲĪó╔┘╗╬─╠źżź¾ź┐Ī╝ź│ź═ź»ź╚żŽĪóŗēäŲŌē┼źūźĻź¾ź╚┤łż¼║ŪŖZ╗╚ż’żņżļżĶż”ż╦ż╩ż├żŲżŁż┐ż┐żßż╚ż╣żļĪŻLSIżžż╬└▄¶ö├╝╗ężõźŲź╣ź╚źčź├ź╔ż╦źūźĒĪ╝źųż“Į╝żŲżļźżź¾źĄĪ╝źŁź├ź╚źŲź╣ź╚Š}╦ĪżŽĪó└▄¶ö├╝╗ęż¼Ė½ż©ż╩ż»ż╩ż├żŲżżżļ┤łżõźŪźąźżź╣ż╦żŽżŌżŽżõ╗╚ż©ż╩żżĪŻ

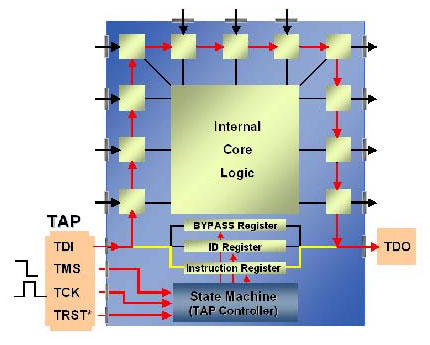

┐▐1ż╬Internal Core Logicż╚Į±ż½żņż┐żŌż╬ż¼źĒźĖź├ź»LSIżŪżóżļĪŻżĮż╬╝■żĻż╦Ū█ÅøżĄżņż┐Š«żĄż╩╗═│čż¼JTAGĪ╩Joint Test Action GroupĪ╦źĒźĖź├ź»ź╗źļżŪżóżļĪŻźąź”ź¾ź└źĻź╣źŁźŃź¾źŲź╣ź╚╦ĪżŽ╩╠ć@JTAGż╚żŌĖ└ż’żņżļż¼ĪóJTAGżŽĖĄĪ╣Īóż│ż╬źŲź╣ź╚╦Īż“─¾░ŲżĘż┐║YØŹ▓Į├─öüż╬ć@Š╬ż└ż├ż┐ĪŻ┐▐ż╦żŽĮ±ż½żņżŲżżż╩żżż¼BGAż╬ź▄Ī╝źļ1Ė─ż¼1Ė─ż╬JTAGź╗źļż╚ż─ż╩ż¼ż├żŲżżżļĪŻż│ż╬öĄ(sh©┤)╦ĪżŪżŽĪóźĘźšź╚źņźĖź╣ź┐ż“╣Į└«ż╣żļżĶż”ż╦JTAGź╗źļż“─Šš`└▄¶öżĘĪóżĮżņżŠżņż╬ź╗źļż½żķż╬Įą╬üėX▌åż“Ū─É█żŪżŁżļżĶż”ż╦żĘżŲż¬ż▒żąĪóĘQź╗źļż╚×┤▒■ż╣żļBGAź▄Ī╝źļż╚ż╬ż─ż╩ż¼żĻėX▌åż“Ū─É█żŪżŁżļĪŻ

µu└▄ż╣żļ├╝╗ę┤ųż¼źĘźńĪ╝ź╚żĘżŲżżżņżąĪ󟎟¾ź└ż¼źųźĻź├źĖż└ż├ż┐żĻĪóČõż╬źŪź¾ź╔źķźżź╚żõź”źŻź╣ź½Ī╝ż╬└«─╣ż╦żĶżļżŌż╬ż└ż├ż┐żĻĪóĖČ░°ż“├Ążļż│ż╚ż¼żŪżŁżļĪŻż▐ż┐ź¬Ī╝źūź¾╔į╬╔żŪżŽĪ󟎟¾ź└ż¼└▄¶öŗżŪ╣ńČŌ▓ĮżĄżņż║ż╦Ū÷żż╚’╦ņż¼żŪżŁżŲżżż┐Īóż╚żżż”żĶż”ż╩Ą£╬Ńż¼żóżĻĪó╔┘╗╬─╠źżź¾ź┐Ī╝ź│ź═ź»ź╚ż½żķ╚»╔ĮżĄżņż┐ĪŻ

┐▐2ĪĪźóź¾ź╔Ī╝źļźĘź╣źŲźÓźĄź▌Ī╝ź╚ż¼─¾ČĪż╣żļJTAGź│ź¾ź╚źĒĪ╝źķż╚┤łĪó┼²╣ń┤─ČŁź─Ī╝źļProVision

źóź¾ź╔Ī╝źļźĘź╣źŲźÓźĄź▌Ī╝ź╚żŽĪó4╦▄ż╬┐«ęÄ(gu©®)żŪ┤łµ£öüż“źŲź╣ź╚żŪżŁżļJTAGź│ź¾ź╚źĒĪ╝źķż╚ĪóProVisionż╚Ō}żų┼²╣ń┤─ČŁź─Ī╝źļż“╚╬ŪõżĘżŲżżżļĪ╩┐▐2Ī╦ĪŻJTAGź│ź¾ź╚źĒĪ╝źķżŽĪóźŲź╣ź╚┐«ęÄ(gu©®)ż“─¾ČĪż╣żļż┐żßż╬źŽĪ╝ź╔ź”ź©źóżŪĪóProVisionżŽźŲź╣ź╚źčź┐Ī╝ź¾ż“Ö┌└«ż╣żļż┐żßż╬┼²╣ńźĮźšź╚ź”ź©źóĪŻ4╦▄ż╬źŲź╣ź╚┐«ęÄ(gu©®)żŽĪóźŲź╣ź╚źčź┐Ī╝ź¾ż“Įą╬üż╣żļ├╝╗ęż╚Īóź╣źŁźŃź¾żĘżŲ±T▓╠ż“Ų■╬üż╣żļ├╝╗ęĪ󟻟Ēź├ź»├╝╗ęĪóźŲź╣ź╚źŌĪ╝ź╔┬ō(li©ón)┘I├╝╗ężŪżóżļĪŻź¬źūźĘźńź¾ż╚żĘżŲJTAGźĻź╗ź├ź╚├╝╗ężŌżóżļĪŻ

żĄżķż╦ĪóØÖźŲź╣ź╚ź┴ź├źūż“─Šš`ż╦źŪźżźĖĪ╝ź┴ź¦Ī╝ź¾ż╬żĶż”ż╦└▄¶öżĘĪóźąź”ź¾ź└źĻź╣źŁźŃź¾ż╬źŲź╣ź╚źčź┐Ī╝ź¾ż“Ų■╬üż╣żļż╚Īó─Šš`└▄¶öżĄżņż┐ź┴ź├źūż╬└▄¶öėX▌åż“źŲź╣ź╚żŪżŁżļĪŻżĄżķż╦┤łż“╩Ż┐¶ĮŚ└▄¶öżĘżŲź╣źŁźŃź¾żŪżŁżļż¼ĪóżĮż╬Šņ╣ńż╦żŽScanBridgeż╚Ō}żųźĘź╣źŲźÓźņź┘źļźŪźąźżź╣ż“ĘQ┤łż╦ŲDżĻ¤²ż▒żļØŁ═ūż¼żóżĻĪóźóź¾ź╔Ī╝źļżŽż│ż╬źŪźąźżź╣żŌ─¾ČĪżĘżŲżżżļĪŻźąź”ź¾ź└źĻź╣źŁźŃź¾źŲź╣ź╚╦ĪżŽżĶż”żõż»╔ߥ┌żĘżĮż”ż└ĪŻ