ARMż╬┐ĘIPĪóCortex-R52żŽ∙N─╣╣Į└«żŪż½ż─╣ŌÅ]▓Į

ARMżŽ∙N─╣╣Į└«ż“ż╚żĻżõż╣ż»żĘż┐CPUź│źóżŪżóżļĪóCortex-R52ż“źĻźĻĪ╝ź╣żĘż┐ĪŻśOŲ░┘Zż╬źųźņĪ╝źŁĄĪē”żõ░Õ┬äżŪż╬┼Ļ╠¶┤╔═²ż╩ż╔Īó╠┐ż╦ĘĖż’żļź▀ź├źĘźńź¾ź»źĻźŲźŻź½źļż╩źĖźńźųż╦×┤żĘżŲĪó∙N─╣╣Į└«ż“ż╚żĻĪóżĶżĻŖWµ£└Łż“╣Ōżßż┐CPUź│źóżŪżóżļĪŻCortex-RżŽźĻźóźļź┐źżźÓ└Łż“╝┬ĖĮżĘżõż╣żżź│źó×æēäźĘźĻĪ╝ź║ĪŻ

┐▐1ĪĪARM Cortex-R52żŽ∙N─╣╣Į└«ż╬źŪźÕźóźļź│źóż“2┴╚×óż©żķżņżļ

Cortex-RźĘźĻĪ╝ź║żŽĪóADASĪ╩└Ķ┐╩ź╔źķźżźąĪ╝?x©¼)¦▐qźĘź╣źŲźÓĪ╦ż╩ż╔ź»źļź▐├ōż╬źūźĒź╗ź├źĄż¼▒ķōQżõŪ¦╝▒ż¼Į¬╬╗żĘż┐ĖÕż╦Ī󟻟ļź▐ż╬╝Īż╬Ų░║Ņż“┬ō(li©ón)┘Iż╣żļĪų╚ĮéāĄĪē”Īūż╩ż╔ż╦╗╚ż”ĪŻźŪźÕźóźļź│źóż“├ōżżżŲĪóŲ¾ż─ż╬CPUź│źóż╦Ų▒┤³ż“ż╚żĻż╩ż¼żķŲ▒żĖ╗┼Ą£ż“żĄż╗ĪóżĮż╬ĮĶ═²±T▓╠ż¼Ų▒żĖż└ż├ż┐Šņ╣ńż╬ż▀╝┬╣įż╣żļĪóż╚żżż”∙N─╣╣Į└«ż“║╬żļĪŻż│ż╬∙N─╣╣Į└«ż“ĪųźŪźÕźóźļź│źóĪ”źĒź├ź»ź╣źŲź├źūĪūż╚Ō}ż¾żŪżżżļĪŻ

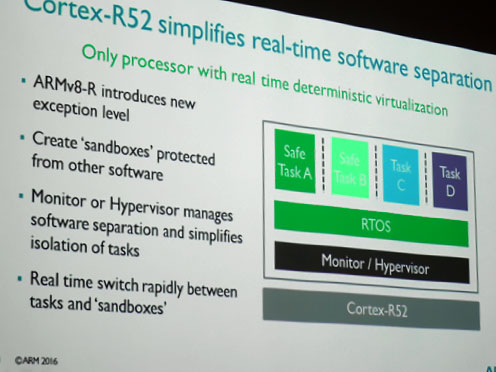

Cortex-R52żŪżŽĪó┐▐1ż╬żĶż”ż╦Īó4ż─ż╬ź│źóż╚żĮżņż“öU(ku©░)Ėµż╣żļźŽźżźčĪ╝źąźżźČż╚żĮż╬Ų░║Ņż“ź┴ź¦ź├ź»ż╣żļźŌź╦ź┐Ī╝övŽ®ż“?y©żn)óż©żŲżżżļĪŻźŽźżźčĪ╝źąźżźČżŽźĮźšź╚ź”ź©źóż╬╩¼▀`ż“┤╔═²żĘź┐ź╣ź»ż╬╩¼▀`ż“į~├▒ż╦ż╣żļĪŻźŌź╦ź┐Ī╝żŽ├▒ż╦żĮż╬Ų░║Ņż“│╬Ū¦ż╣żļĪŻ

żĄżķż╦Ī󟎟żźčĪ╝źąźżźČżŽĪó┐▐1żŪżŽ▐kż─ż╬RTOSż¼4ż─ż╬ź┐ź╣ź»(źĮźšź╚ź”ź©źó)ż“ź½źąĪ╝żŪżĘżŲżżżļż¼ĪóRTOSż“╩╠ż╬Ų¾ż─ż╦╩¼ż▒żŲź┐ź╣ź»A/Bż╚Īóź┐ź╣ź»C/Dż╬ź░źļĪ╝źūż╦╩¼ż▒żļż╚żżż”▓Š„[▓ĮżŌ╣įż”ż│ż╚ż¼żŪżŁżļĪŻź»ź’ź├ź╔ź│źóż╬∙N─╣╣Į└«żŪżóżļż┐żßĪó∙N─╣╣Į└«ż“▓Š„[▓Įż╦żĶż├żŲŲ¾ż─ŲDżļż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩żļĪŻż┐ż└żĘĪóż│żņżķżŽĖ▄Ąęż╬źčĪ╝ź╚ź╩Ī╝ż╬═ūĄßż╦żĶż├żŲARMŖõż¼╣Į└«ż“╩čż©żļĪŻ

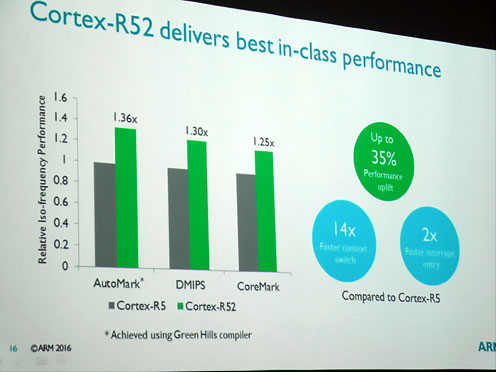

“£═Ķż╬Cortex-R5żŪżŽĪóŲ▒══ż╩∙N─╣╣Į└«ż└ż├ż┐ż¼ĪóźŪźÕźóźļź│źóżŪżóż├ż┐ż┐żßż╦▐kż─ż╬źĖźńźųżĘż½żŪżŁż╩ż½ż├ż┐ĪŻCortex-R52żŽż│ż╬∙N─╣╣Į└«ż╬źŪźÕźóźļź│źóż“Ų¾ż─×óż©ż┐╩┬š`źūźĒź╗ź├źĄŲ░║ŅżŌ▓─ē”żŪżóżļż┐żßĪó└Łē”żŽR5żĶżĻżŌĖ■æųżĘżŲżżżļ(┐▐2)ĪŻź┘ź¾ź┴ź▐Ī╝ź»└Łē”żŽR5ż╬║ŪĮj(lu©░)1.36Ū▄Īó│õżĻ╣■ż▀ż¼2Ū▄Īóź│ź¾źŲźŁź╣ź╚ź╣źżź├ź┴ż¼14Ū▄Ė■æųżĘżŲżżżļĪŻź│ź¾źŲźŁź╣ź╚ź╣źżź├ź┴ż╚żŽĪó╩Ż┐¶ż╬ĮĶ═²ż“▐kż─ż╬CPUżŪČ”Ń~żŪżŁżļżĶż”ż╦ż╣żļż┐żßż╦CPUż╬ėX▌åż“╩▌┘TżĘż┐żĻ╔³ĖĄżĘż┐żĻż╣żļĄĪē”ĪŻź▐źļź┴ź┐ź╣ź»żõ│õżĻ╣■ż▀ĄĪē”ż╦żŽ’L(f©źng)ż½ż╗ż╩żżĪŻ

┐▐2ĪĪCortex-R52żŽ“£═Ķż╬R5ż╦╚µż┘Īóź┘ź¾ź┴ź▐Ī╝ź»żŪżŽ╣Ō└Łē”

Cortex-R52ż╬ĄĪē”ŖWµ£żŽż│żņż└ż▒żŪżŽż╩żżĪŻżŌż┴żĒż¾ĪóśOŲ░┘Zż╬ŖWµ£æä│╩ISO26262ż╦ØŹĄ“żĘĪó∙N─╣╣Į└«ż“?q©▒)Ö├ōżĘżŲŖWµ£┤ØŹż╬║Ū╣Ō╩÷(śOŲ░▒┐┼Š▓─ē”źņź┘źļ)ż╬ASIL Dż╦żŌ×┤▒■żŪżŁżļĪŻźąź╣Ū█└■ż╬╩▌ĖŅĄĪē”żŌżóżļĪŻż│żņżŽźßźŌźĻż╬ECCĪ╩ĖĒżĻĖĪĮąĪ”ÖÄ┘ćĄĪē”Ī╦ż“źąź╣Ū█└■ż╦żŌ│╚─źżĘĪó┘ćżĘżżźŪĪ╝ź┐ż¼┴„£p┐«żĄżņżļżĶż”ż╦źŪĪ╝ź┐ż“╩▌ĖŅż╣żļĄĪē”ĪŻ

SoCź┴ź├źūż╬│½╚»╗■┼└żŪżŽĪóISO 26262ØŹĄ“żõASILż╬ŖWµ£źņź┘źļż“ź»źĻźóż╣żļżĶż”ż╦źĮźšź╚ź”ź©źóż“╣Į└«żĘźŽĪ╝ź╔ź”ź©źóż“└▀╝Ŗż╣żļĪŻżĘż½żĘĪó┴÷╣į├µż╬ź»źļź▐ż¼ź╬źżź║ż╩ż╔żŪĖĒŲ░║Ņż╣żļŠņ╣ńż╦żŽĪó∙N─╣╣Į└«żŪ×┤ĮĶż╣żļĪŻCortex-R52żŽĪó“£═Ķż╬R5żĶżĻżŌ╣ŌÅ]ĮĶ═²żŪżŁżļż┐żßĪóOSżŌ┤▐żßżŲźĻźóźļź┐źżźÓżŪ╚Įéāż╚źóź»ź┴źÕź©Ī╝ź┐ż╬Ų░║Ņż“╝┬╣įżŪżŁżļżĶż”ż╦ż╩żļĪŻźĻźóźļź┐źżźÓ└Łż“─_£åż╣żļźčź’Ī╝ź╚źņźżź¾żõźĘźŃźĘĪ╝ż╦╗╚ż”Šņ╣ńż╦żŽĪóŲ▒żĖ¹|╬Óż╬źūźĒź╗ź├źĄź│źóż“4Ė─├ōżżĪó╩┬š`Ų░║Ņż╬∙N─╣╣Į└«ż╦żĶż├żŲĪóżĶżĻ┴ßż»żĶżĻŖWµ£ż╦Ų░║Ņż╣żļöĄ(sh©┤)╝░ż¼Ė■ż»ĪŻADASż╬żĶż”ż╦▒ķōQ└Łē”ż“─_£åż╣żļŠņ╣ńż╦żŽĪóCortex-AźĘźĻĪ╝ź║ż“ź▐źļź┴ź│źóżŪ╗╚ż├żŲ╣ŌÅ]▒ķōQż“╣įżżCortex-R52żŪŖWµ£└▀╝Ŗż“╣įż”Īóż╚żżż”źžźŲźĒźūźĒź╗ź├źĄź│źóż╬SoCż¼┼¼żĘżŲżżżļĪŻ