Siemens EDAĪóŗī2└ż┬Õż╬SoCĖĪŠ┌ź©ź▀źÕźņĪ╝ź┐ż“4×æēä╚»╔Į

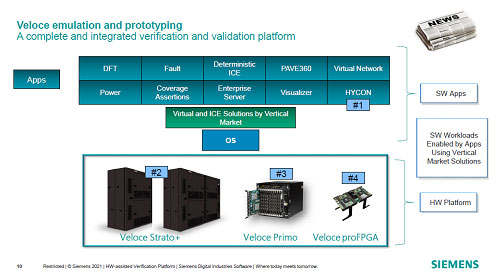

Siemens EDAĪ╩ĄņMentor GraphicsĪ╦żŽĪóLSI└▀╝Ŗż“źŽĪ╝ź╔ź”ź©źóźņź┘źļżŪĖĪŠ┌ż╣żļź©ź▀źÕźņĪ╝ź┐VeloceĪ╩ź┘źĒĪ╝ź┴ź¦ż╚╚»▓╗Ī╦ż╬╝Ī└ż┬Õ╚Ūż╬ĖĪŠ┌źĘź╣źŲźÓż“╚»╔ĮżĘż┐ĪŻ║Żövż╬ĖĪŠ┌źĘź╣źŲźÓżŪżŽĪóźŽĪ╝ź╔ź”ź©źóź▐źĘź¾ż└ż▒żŪżŽż╩ż»ĪóČ©─┤└▀╝ŖżŪØŁ═ūż╩▓Š„[źūźķź├ź╚źšź®Ī╝źÓżŪż╬źĮźšź╚ź”ź©źóĖĪŠ┌ź─Ī╝źļVeloce HYCONż“┤▐żß4×æēäż“├ō┴TżĘż┐ĪŻ

┐▐1ĪĪLSI└▀╝ŖĖĪŠ┌ż╬4ż─ż╬┐Ę×æēäź─Ī╝źļĪĪĮąųZĪ¦Siemens EDA.

LSI└▀╝ŖżŪżŽ║ŻżõLSIµ£öüż╬övŽ®ż¼Įą═ĶżŲż½żķĪóżĮżņż╦┼ļ║▄ż╣żļźĮźšź╚ź”ź©źóż“│½╚»ż╣żļż╬żŪżŽż╩ż»Īó║ŪĮķż╬├╩│¼żŪźŽĪ╝ź╔ź”ź©źóż╬▓Š„[┼¬ż╩źūźķź├ź╚źšź®Ī╝źÓż“ż▐ż║║Ņ└«ż╣żļĪŻżĮż╬▓Š„[źūźķź├ź╚źšź®Ī╝źÓæųżŪźĮźšź╚ź”ź©źóż“│½╚»żĘ╗ŽżßżļĪŻżĮż╬źĮźšź╚ź”ź©źóż╬ź’Ī╝ź»źĒĪ╝ź╔ż¼▒■├ō▌xŠņżŪ┼¼└┌ż½ż╔ż”ż½ż╚żżż├ż┐▓“└Žż“╝┬║▌ż╦źĘź▀źÕźņĪ╝źĘźńź¾ż╣żļż┐żßż╦ĪóĖĪŠ┌ź─Ī╝źļVeloceż╦źĮźšź╚ź”ź©źóż“║▄ż╗ĖĪŠ┌ż╣żļĪŻż│ż╬ż┐żßĪóźĮźšź╚ź”ź©źóż╚źŽĪ╝ź╔ź”ź©źóż╬źŽźżźųźĻź├ź╔ż╚żżż”┴T╠ŻżŪĪóHYCONĪ╩HYbrid CONfigurableĪ╦ż╚Ō}żųĪŻ

SoCż╬źŽĪ╝ź╔ź”ź©źóæųżŪżŽźĘźĻź│ź¾æųż╦ĮĖ└čż╣ż┘żŁIPźųźĒź├ź»ż“RTL└▀╝ŖĪ󿥿ķż╦żĮżņżķż“┴╚ż▀╣ńż’ż╗żŲSoCż╬RTL└▀╝Ŗż“╣įżżRTLźņź┘źļż“┤░└«żĄż╗żļĪŻżĮż╬ĖÕĪóź▓Ī╝ź╚źņź┘źļż╬övŽ®ż╦═Ņż╚żĘĪóź═ź├ź╚źĻź╣ź╚żŪövŽ®Ū█└■Š╩¾ż“║Ņ└«ż╣żļż¼Īóź═ź├ź╚źĻź╣ź╚ż╬║ŅČ╚żŽ║ŪŖZéb═²╣ń└«ź─Ī╝źļżŪ▐kĄżż╦╣įż”ż│ż╚ż¼¾HżżĪŻ║ŪĖÕż╦Ū█ÅøŪ█└■źņźżźóź”ź╚ż“║čż▐ż╗żļĪŻ

ż│ż╬┤ųĪó└▀╝Ŗ╣®µćż┤ż╚ż╦┘ć│╬ż╦ĄŁĮ꿥żņżŲżżżļż½ż╔ż”ż½Īóźąź░ż¼ż╩żżż½ż╔ż”ż½ż╩ż╔ĖĪŠ┌║ŅČ╚ż¼Ų■żĻĪóĖÕ╚ŠżŪŪ█└■æųż╬╔įÉ║╣ńżŪźņĪ╝źĘź¾ź░żõź╣źŁźÕĪ╝ż╩ż╔ź┐źżź▀ź¾ź░ż╬╠õ¼öż“ÅŚż│żĄż╩żżżĶż”ż╦ĖĪŠ┌ż╣żļż¼ĪóźĮźšź╚ż└ż▒żŪżŽØ▓╩¼ż╦äh▓┴żĘżŁżņż╩żżż┐żßĪóźŽĪ╝ź╔ź”ź©źóżŪż╬ĖĪŠ┌║ŅČ╚ż¼’Lż½ż╗ż╩żżĪŻ

║Żövż╬┐Ę×æēäż╬ĖĪŠ┌źŽĪ╝ź╔ź”ź©źóź©ź▀źÕźņĪ╝ź┐żŽĪóź│ź¾źįźÕĪ╝ź┐żĮż╬żŌż╬żŪżóżļVeloce Strato+ż╚ĪóFPGAź▄Ī╝ź╔10ĮŚż½żķż╩żĻĪóźūźĒź╚ź┐źżźįź¾ź░▓─ē”ż╩Veloce PrimoĪóżĮżĘżŲFPGAæųżŪSoCż╬źūźĒź╚ź┐źżźįź¾ź░ż¼▓─ē”ż╩Veloce proFPGAż╬įÆż─ż“┬Ęż©ż┐ĪŻ

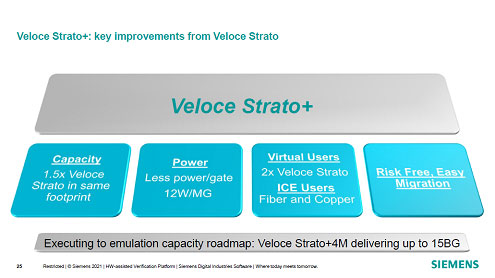

┐▐2ĪĪŗī2└ż┬Õż╬LSI└▀╝ŖĖĪŠ┌ź©ź▀źÕźņĪ╝ź┐Veloce Strato+ĪĪĮąųZĪ¦Siemens EDA

║ŪĮķż╬Veloce Strato+żŽĪóŗī1└ż┬Õż╬Veloceż“źóź├źūź░źņĪ╝ź╔żĘż┐źŽĪ╝ź╔ź”ź©źóź©ź▀źÕźņĪ╝ź┐żŪżóżĻĪó║ŪĮj150▓»ź▓Ī╝ź╚ż╬SoCż▐żŪ│╚─źżŪżŁżļĪŻŗī1└ż┬Õż╚╚µż┘Īó1.5Ū▄ż╬═Ų╬╠ż“Ęeż┴Īó100╦³ź▓Ī╝ź╚┼÷ż┐żĻż╬Š├õJ┼┼╬üżŽ12Wż└ż╚żżż”Ī╩┐▐2Ī╦ĪŻ└▀╝Ŗż╬┴ßżż├╩│¼żŪ▓Š„[┼¬ż╩SoCźŌźŪźļż“╣Į├█żĘĪó╝┬║▌ż╬źšźĪĪ╝źÓź”ź¦źóżõźĮźšź╚ź”ź©źóż“Veloce Strato+żŪ┴÷żķż╗żŲĖĪŠ┌ż╣żļĪŻéb═²ż╬ĖĪŠ┌ż¼║čż¾ż└żķĪó╝ĪżŽź┐źżź▀ź¾ź░ĖĪŠ┌żŪżóżļĪŻ

Ų▒żĖ└▀╝Ŗż“Veloce PrimożŪżŽĪó╝┬║▌ż╬ŖZżżź╣źįĪ╝ź╔żŪSoCźŌźŪźļż“Ų░ż½żĘĪóźĮźšź╚ź”ź©źó/źŽĪ╝ź╔ź”ź©źóż╬źżź¾ź┐Ī╝źšź¦źżź╣ż“ĖĪŠ┌żĘĪóźóźūźĻź▒Ī╝źĘźńź¾źĮźšź╚ź”ź©źóż“┴÷żķż╗żļż│ż╚ż¼żŪżŁżļż╚żżż”ĪŻVeloce Strato+ż╚Veloce PrimożŽŲ▒żĖRTLĪóŲ▒żĖ▓Š„[ĖĪŠ┌┤─ČŁĪóŲ▒żĖźŌźŪźļż“╗╚ż├żŲĖĪŠ┌ż╣żļĪŻ

ż▐ż┐ĪóSoCż“FPGAżŪźūźĒź╚ź┐źżźįź¾ź░ż╣żļŠņ╣ńżŽź▄Ī╝ź╔ż╬Veloce proFPGAż“╗╚ż├żŲĖĪŠ┌żĘSoCż“äh▓┴żŪżŁżļĪŻVeloce PrimożŽĪóFPGAż“┼ļ║▄żĘż┐ź▄Ī╝ź╔ż“10ĮŚ┼ļ║▄żĘż┐1±śż╬ø▄öüż“4±śźķź├ź»ż╦┼ļ║▄żĘż┐żŌż╬żŪĪó║ŪĮjżŪ320Ė─ż╬FPGAż“┼ļ║▄żĘżŲżżżļĪŻ╚ŠŲ│öü┤ļČ╚ż¼źūźĒź╚ź┐źżźįź¾ź░żŪSoCż“FPGAżŪ║Ņ×æżĘżĮż╬SoCż“ĖĪŠ┌ż╣żļż╬ż╦╗╚ż’żņżŲżżżļĪŻ

AMDż╬CPUżŪżóżļEPYCźūźĒź╗ź├źĄżõĪóArmż╬CPUź│źóż╬│½╚»ż╦żŌFPGAźūźĒź╚ź┐źżźįź¾ź░ż╬ĖĪŠ┌ż╦╗╚ż’żņż┐ż╚żĘżŲżżżļĪŻ

ŗī1└ż┬Õż╬Veloce Stratoż╦żŽŲ╚śOż╦│½╚»żĘż┐ź┴ź├źūCrystal3ż“┼ļ║▄żĘżŲżżż┐ż¼Īó║Żövż╬ŗī2└ż┬ÕżŪżŽź┴ź├źūżŌ┐Ęæäż╦ÅŚż│żĘż┐ĪŻ┐Ęź┴ź├źūCrystal3+żŽĪó2.5Dż╬SoCżŪżóżĻĪóØi└ż┬Õż╬Veloce StratożŪżŽ16ź┴ź├źūż“┼ļ║▄żĘżŲżżż┐ż¼Īó║Żövż╬ź▐źĘź¾ż╦żŽ24ź┴ź├źūż“┼ļ║▄żĘż┐ż╚żżż”ĪŻ

ĖĪŠ┌├ōż╬ź©ź▀źÕźņĪ╝ź┐żŽĮjŠ}ż╬╚ŠŲ│öüźßĪ╝ź½Ī╝żŽVeloceż“āAżżæųż▓żļż¼ĪóżĮżņ░╩│░ż╬╚ŠŲ│öüźßĪ╝ź½Ī╝żŽźūźĒźĖź¦ź»ź╚ź┘Ī╝ź╣żŪźĻĪ╝ź╣Ę└╠¾ż╣żļź▒Ī╝ź╣ż¼¾Hżżż╚żżż”ĪŻż▐ż┐╣±ŲŌżŪżŽēä└Ņż╦żóżļźßź¾ź┐Ī╝ź░źķźšźŻź├ź»ź╣źĖźŃźčź¾ż╬ź¬źšźŻź╣ż╦└▀ÅøżĘżŲżżżļVeloceż“źĻźŌĪ╝ź╚żŪżŌ╗╚ż©żļżĶż”ż╦żĘżŲżżżļż╚żżż”ĪŻ