┐ĘÖ┌KeysightĪó65GźĄź¾źūźļ/╔├ż╚«Ć╣ŌÅ]ż╬AWGż“╚»Ūõ

Keysight TechnologiesżŽĪó65GźĄź¾źūźļ/╔├ż╚ØÖŠ’ż╦╣ŌÅ]ż╬źĄź¾źūźĻź¾ź░źņĪ╝ź╚ż“Ęeż┴Īó20GHzż╚żżż”Č╦żßżŲ╣Łżż┬ė░ĶżŪ║ŪĮj(lu©░)4ź┴źŃź¾ź═źļż▐żŪ│╚─źżŪżŁżļŪż┴TāSĘ┴╚»Ö┌▀_(d©ó)Ī╩AWGĪ╦ż“│½╚»Īó×æēä▓ĮżĘż┐(┐▐1)ĪŻKeysightżŽĪóżŌż╚żŌż╚Hewlett-Packardż“╩ņöüż╚żĘżŲ╩¼ż½żņż┐Agilent Technologyż½żķĪ󿥿ķż╦╝Ŗ▒R▀_(d©ó)ŗ╠ńż╚żĘżŲ2014ŃQ8ĘŅ1Ų³ż╦╩¼▀`żĘż┐┤ļČ╚ĪŻ

![┐▐1ĪĪ«Ć╣ŌÅ]Ī”«Ć╣Ł┬ė░Ķż╬Ūż┴TāSĘ┴╚»Ö┌▀_(d©ó)M8195A](/archive/editorial/technology/img/TFE140911-01a.jpg)

┐▐1ĪĪ«Ć╣ŌÅ]Ī”«Ć╣Ł┬ė░Ķż╬Ūż┴TāSĘ┴╚»Ö┌▀_(d©ó)M8195A

Keysightż╚żżż”ē¶ć@┼┘żŽż▐ż└─ŃżżżŌż╬ż╬Īó╣Ō╝■āSĪ”╣ŌÅ]Č\Įčż╦żŽĖ┼ż»ż½żķ─Ļähż╬żóż├ż┐HPż╬╬«żņż“ĄŌżÓż└ż▒ż╦ĪóŲ³╦▄╦Ī┐═źŁĪ╝źĄźżź╚Ī”źŲź»ź╬źĒźĖĪ╝╝ę─╣ż╬Ū▀ćŖ┘ć£½Ģ■(hu©¼)(┐▐2)żŽĪóĪųHP┴ŽČ╚╗■ż╦övĄóżĘż┐ĪūĪóż╚║Żövż╬╩¼│õż“╔ĮĖĮż╣żļĪŻźŁĪ╝źĄźżź╚żŽ┼┼╗ę╝Ŗ▒RĄ£Č╚ż╦100%└ņŪ░żĘĪóŪõżĻæųż▓ż╬10%░╩æųż“Ė”ē|│½╚»ż╦┼Ļ½@ż╣żļĪŻŲ▒╝꿎ĪóĪų└ż─cĮķĪūż╦ż│ż└ż’żļż╚żżż”öĄ(sh©┤)┐╦ż“ź│ź▀ź├ź╚żĘżŲżżżļĪŻ

┐▐2ĪĪźŁĪ╝źĄźżź╚Ī”źŲź»ź╬źĒźĖĪ╝╝ę┐”ē»╝╣╣įŪv╝ę─╣ż╬Ū▀ćŖ┘ć£½Ģ■(hu©¼)

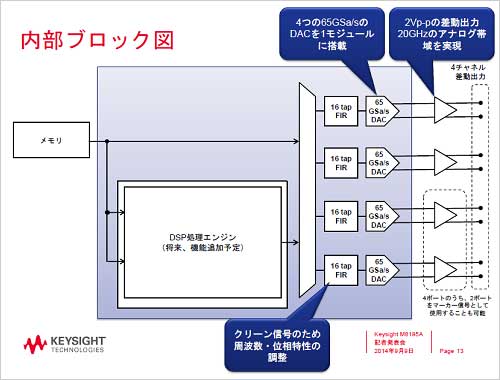

żĮż│żŪ║Żöv╚»╔ĮżĄżņż┐┐Ę×æē俎Ī󟥟¾źūźĻź¾ź░źņĪ╝ź╚ż¼65GźĄź¾źūźļ/╔├ż╚Č├░█┼¬ż╦║┘ż½ż»Īó20GHzż╚╝■āS┐¶┬ė░Ķż¼╣Łż»ĪóżĘż½żŌ║ŪĮj(lu©░)4ź┴źŃź¾ź═źļż▐żŪ└▄¶öżŪżŁżļĪóż╚żżż”└ż─cĮķż╦żšżĄż’żĘżż▒R─Ļ▀_(d©ó)żŪżóżļĪŻż│żņż█ż╔ż▐żŪż╦╣Ō└Łē”ż╩AWGż“▐köüż╔ż│ż╦╗╚ż”ż╬ż½ĪŻ

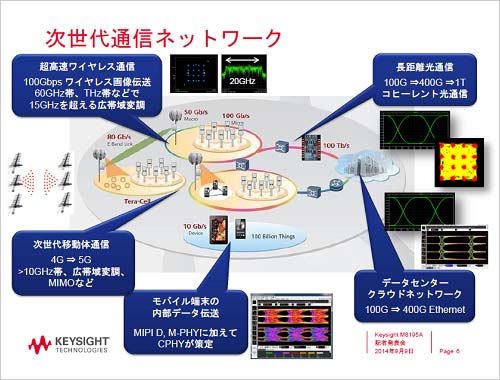

Keysightż¼┴└ż”▌xŠņżŽĪó100GbpsĪóżĮż╬╝Īż╬400Gbpsż╚żżż├ż┐Īó«Ć╣ŌÅ]żŪż╩ż▒żņżąźŪĪ╝ź┐ź╚źķźšźŻź├ź»ż“ĮĶ═²żĘżŁżņż╩żż╝Ī└ż┬Õ─╠┐«ź═ź├ź╚ź’Ī╝ź»żŪżóżļ(┐▐3)ĪŻż│ż│ż╦żŽźąź├ź»ź▄Ī╝ź¾ż╚ż╩żļ─╣š{(di©żo)▀`─╠┐«żŪżŽĪó100GbpsĪó400GbpsĪ󿥿ķż╦żŽ1TĪ╩źŲźķĪ╦bpsż╚Įj(lu©░)═Ų╬╠żžż╚Ė■ż½ż├żŲżżżļĪŻżĮż╬ż┐żßż╬Č\Įčż╚żĘżŲżŽĪóĖ„─╠┐«ż╦“£═Ķż╬ź¬ź¾ź¬źšöĄ(sh©┤)╝░żŪżŽż╩ż»ĪóQPSKĪ╩quadrature phase shift keyingĪ╦żõ16-QAMĪ╩quadrature amplitude modulationĪ╦ż╬żĶż”ż╩źŪźĖź┐źļ╩č─┤ż“╗▄żĄżņż┐źŪźĖź┐źļź│źęĪ╝źņź¾ź╚─╠┐«ż“ŠW(w©Żng)├ōż╣żļĪŻź’źżźõźņź╣źŌźąźżźļ─╠┐«żŪżŌ60GHz┬ėż╩ż╔żŪż╬źėźŪź¬┼┴┴„ż╩ż╔ż╦żŽ¾H┐¶ż╬źµĪ╝źČĪ╝ż“źĄź▌Ī╝ź╚ż╣żļ100Gbpsż╚żżż├ż┐Įj(lu©░)═Ų╬╠┼┴┴„żžż╬═ūĄßż¼żóżļĪŻĘ╚┬ė├╝¼ŹżŪżŌ4Gż½żķ5Gż╦ż╩żļż╚10Gbpsż╚żżż”źŪĪ╝ź┐źņĪ╝ź╚ż╦ż╩żļĪŻŃ~└■ż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõź»źķź”ź╔ź═ź├ź╚ź’Ī╝ź»żŪżŽĪóEthernetż¼100Gbpsż½żķ400Gbpsżžż╚╣ŌÅ]ĮĶ═²ż¼ĄßżßżķżņżļĪŻż│ż╬ź═ź├ź╚ź’Ī╝ź»żŪżŽĪó┤ļČ╚Ė■ż▒ż╬źūźķźżź┘Ī╝ź╚ź»źķź”ź╔ż└ż▒żŪżŽķu│▓ż¼ÅŚżŁż┐żķźŪĪ╝ź┐ż¼╝║ż’żņżļČ▓żņż¼żóżĻĪóźčźųźĻź├ź»ź»źķź”ź╔żŌŠW(w©Żng)├ōż╣żļźŽźżźųźĻź├ź╔ź»źķź”ź╔żžż╬Ų░żŁż¼żóżļĪŻż│żņżķż╬╝ę▓±źżź¾źšźķżŪżŽĮj(lu©░)═Ų╬╠ż╬źŪĪ╝ź┐ż“£pż▒Ų■żņżķżņżļż█ż╔ż╬╣ŌÅ]└ŁĪó╣Ł┬ė░ĶØŖ└Łż¼ĄßżßżķżņĪóśŗ(g©░u)ż╩żļ╣ŌÅ]▓Įż╦żŽ│╚─ź└ŁżŪ×┤▒■ż╣żļĪŻ

┐▐3ĪĪ╝Ī└ż┬Õ─╠┐«ź═ź├ź╚ź’Ī╝ź»▌xŠņĪĪĮąųZĪ¦Keysight Technology

ż│ż”żżż├ż┐źŽźżź©ź¾ź╔ż╬▒R─Ļ▀_(d©ó)żŽ╗╚żżżõż╣żĄżŌ─_═ūżŪżóżĻĪóKeysightżŽźµĪ╝źČĪ╝ż¼źŲź╣ź╚ż╦╗╚ż”āSĘ┴ż“ĘQ¹|źčźķźßĪ╝ź┐ż╩ż╔żŪ└▀─Ļż╣żļźĮźšź╚ź”ź©źóżŌ─¾ČĪż╣żļĪŻż│żņżķżŽPCż╚└▄¶öżĘżŲĪóPCż╬▓ĶĀCż“Ė½ż╩ż¼żķĪó┤╦▄┼¬ż╩└▀─ĻżõāSĘ┴ż╬źĒĪ╝ź╔Īóź╗Ī╝źųĪóźķźżźųźķźĻż╬╩▌┘Tż╩ż╔ż“╣įż”ĪŻ▓├ż©żŲĪóźėź├ź╚ź©źķĪ╝ż“▒R─Ļż╣żļż┐żßż╬źĮźšź╚ź”ź©źóżŌ┬Ęż©żŲżżżļĪŻźµĪ╝źČĪ╝ż¼Ų╚śOż╦āSĘ┴ż“║ŅżĻĮążĘż┐żżŠņ╣ńż╦żŽĪóMATLABżõLabVIEWż╩ż╔ż╬ź─Ī╝źļżõĪóC++źūźĒź░źķź▀ź¾ź░Ė└ĖņżŪāSĘ┴ż“└▀╝ŖĪ”ĖĪŠ┌żŪżŁżļĪŻ

żĄżķż╦Īóż│ż╬▒R─Ļ▀_(d©ó)żŽź▐źļź┴źņź┘źļż╬│¼├╩ėXż╬āSĘ┴żŌ║Ņ└«żŪżŁżļĪŻ¾H├═ż╬╩¼▓“ē”źņź┘źļżŽ╣ŌÅ]╝■āS┐¶ź╚ź░źļż╦żĶżļż¼Īó32GźĄź¾źūźļ/╔├ż└ż╚8źņź┘źļż▐żŪ║ŅżĻĮąż╗żļż╚żżż”ĪŻżŌż├ż╚źĄź¾źūźĻź¾ź░źņĪ╝ź╚ż“▓╝ż▓żļż╚Īó16/32źņź┘źļż╦żŌ×┤▒■żŪżŁżļż╚żĘżŲżżżļĪŻ

ż▐ż┐Īó4ź┴źŃź¾ź═źļż╬āSĘ┴Ī󿥿ķż╦żŽż│ż╬▒R─Ļ▀_(d©ó)ż“║ŪĮj(lu©░)4±śĪóż╣ż╩ż’ż┴16ź┴źŃź¾ź═źļż╬āSĘ┴ż“ĪóŲ▒┤³ż“ż╚żĻż╩ż¼żķĮą╬üż╣żļż│ż╚żŌ▓─ē”ż└ĪŻżĮż╬ż┐żßż╦Ų▒┤³ż“ż╚żļż┐żßż╬źŌźĖźÕĪ╝źļż“├ō┴TżĘżŲż¬żĻĪóĘQźŌźĖźÕĪ╝źļż╬ź╣źŁźÕĪ╝żŽźĄźųfsĪ╩źšź¦źÓź╚╔├Ī╦ż╚ØÖŠ’ż╦ø]żżĪŻ

┐▐4ĪĪŲ╚śO│½╚»żĘż┐Si CMOSASICż╚īÜŖõ4Ė─ż╬InPźóź¾źūĪĪĮąųZĪ¦Keysight Technology

ż│żņż█ż╔ż╬╣ŌÅ]ż╬▒R─Ļ▀_(d©ó)ż“│½╚»żŪżŁż┐ż╬żŽĪóŲ╚śOż╬ASICĪ╩CMOSźūźĒź╗ź╣Ī╦ż“└▀╝ŖżĘĪóIII-V▓Į╣ńر╚ŠŲ│öüż╬InPźóź¾źūż“└▀╝ŖÄź×æļ]żĘż┐ż┐żßżŪżóżļ(┐▐4)ĪŻCMOS ASICż╦żŽ65GźĄź¾źūźļ/╔├ż╬╣ŌÅ]DAź│ź¾źąĪ╝ź┐ż╚16ź┐ź├źūż╬FIRĪ╩Ń~Ė┬źżź¾źčźļź╣▒■┼·Ī╦źšźŻźļź┐ż╩ż╔ż“ĮĖ└čżĘżŲżżżļĪŻĮø(j©®ng)═Ķż╦×óż©żŲDSPź│źóżŌ└▀╝ŖżĘżŲżżżļĪŻż│ż╬DSPź│źóżŽĪó╬Ńż©żą┤╦▄āSĘ┴ż╦ź╬źżź║ż“║▄ż╗ż┐żĻĪóź©ź¾ź│Ī╝ź└ĄĪē”ż“└▀ż▒ż┐żĻĪó║ŻĖÕż╬ĄĪē”│╚─źż╦ŠW(w©Żng)├ōż╣żļĪŻCMOS ASICż╬×æļ]żŽźšźĪź”ź¾ź╔źĻż╦░══Ļż╣żļĪŻ