╣ŌNA EUVźĻźĮź░źķźšźŻäóÅøŗī1ęÄ(gu©®)ż“Intelź¬źņź┤ź¾╣®Šņż╦Ų│Ų■Īó┴╚ż▀╬®żŲż┐

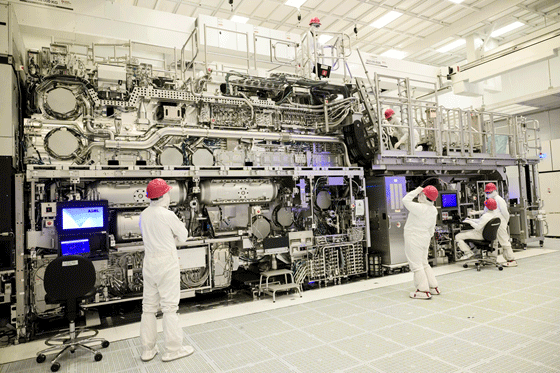

IntelżŽ1.8nmźūźĒź╗ź╣ź╬Ī╝ź╔ż╦┴Ļ┼÷ż╣żļIntel 18Aż╦Ė■ż▒Ī󟬟ķź¾ź└ASML╝ę×æż╬╣ŌNAż╬EUVźĻźĮź░źķźšźŻäóÅøĪųTWINSCAN EXE:5000ĪūĪ╩┐▐1Ī╦ż“źūźĒź╗ź╣│½╚»Ą“┼└ż╬żóżļź¬źņź┤ź¾╣®Šņż╦Ų│Ų■żĘż┐ĪŻż▐ż║Intel 18AźūźĒź╗ź╣ź╬Ī╝ź╔ż½żķŲ│Ų■żĘĪóIntel 14Aź╬Ī╝ź╔żžż╚│╚─źżĘżŲżżż»═Į─Ļż└ĪŻIntelż╬źšźĪź”ź¾ź╔źĻĄ£Č╚ŗż¼Ų│Ų■żĘTSMCż╦╝{żżż─żŁ╝{żż▒█ż╣╝Ŗ▓Ķż“┐╩żßżļĪŻ

┐▐1ĪĪASML║Ū┐Ęż╬╣ŌNA EUVäóÅøĪųTWINSCAN EXE:5000ĪūĪĪĮąųZĪ¦ASML

ż│żņż▐żŪż╬EUVŽ¬Ė„äóÅøż╚żĘżŲżŽĪó2017ŃQż╦NAĪ╩│½Ė²┐¶Ī¦Numerical ApertureĪ╦ż¼0.33ż╬ŗī1└ż┬Õż╬╬╠ŠÅĄĪĪųNXE:3400Īūż╚2020ŃQż╦ĪųNXE:3600Īūż“IntelżŽŲ│Ų■żĘżŲżŁż┐ĪŻEUV│½╚»└šŪżŪvżŪĪóIntelż╬źšź¦źĒĪ╝żŪżóżĻĪóIntel Foundry Logic Technology Developmentż╬Lithography , Hardware and Solutionż╬źŪźŻźņź»ź┐żŪżóżļMark PhilipsĢ■Ī╩┐▐2Ī╦żŽĪóEUVż╬żĶż”ż╩ø]āS─╣ż╬ŲX└■źĻźĮź░źķźšźŻż“27ŃQ┤ų│½╚»żĘżŲżŁż┐ż╚żżż”ĪŻIntelżŽEUVż╬╝┬└ėż¼20ŃQ░╩æųżóżļż╚äė─┤ż╣żļĪŻ

┐▐2ĪĪIntelźšź¦źĒĪ╝Ę¾ĪóIntel Foundry Logic Technology Developmentż╬Lithography , Hardware and Solutionż╬źŪźŻźņź»ź┐Mark PhilipsĢ■

║Żövż╬┐Ę×æē俎NA0.55ż╚ż╩żĻĪóźĘź¾ź░źļŽ¬Ė„żŪ8nmźŽĪ╝źšźįź├ź┴ż╬źčź┐Ī╝ź¾ż“▓├╣®żŪżŁżļĪŻĖĮ║▀Īó3nmĪó2nmź╬Ī╝ź╔ż╚żżż├żŲżŌ╝┬Øó╦ĪżŽ12nmµć┼┘ż╬ż▐ż▐żŪżóżļĪŻżĄżķż╦EUVż“╗╚ż├żŲżŌ3nmż»żķżżż╦ż╩żļż╚Īóź└źųźļźčź┐Ī╝ź╦ź¾ź░Ž¬Ė„ż¼ØŁ═ūż╦ż╩żĻż─ż─żóżļĪŻNAż¼0.55ż╚ż╩żļż╚źĘź¾ź░źļŽ¬Ė„ż¼▓─ē”ż╦ż╩żļż┐żßĪóź▐ź╣ź»┐¶ż“žōżķż╣ż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩żļĪóż╚PhilipsĢ■żŽĖņż├żŲżżżļĪŻ

ĖĮ╝┬ż╦ASMLżŽźšźļźšźŻĪ╝źļź╔żŪ10nmźĄźżź║ż╬źčź┐Ī╝ź¾ż“╝┬ĖĮżĘżŲż¬żĻĪóNA0.55ż╬╠OČ┌ż“ż─ż▒ż┐ż╚Ų▒Ģ■żŽĮęż┘żŲżżżļĪŻASMLżŽźčĪ╝ź╚ź╩Ī╝żŪżóżļZeissż╚▐kĮ’ż╦╣ŌNA EUVäóÅøż╬Ė„│žÅUż“└▀╝ŖżĘż┐ż╚żżż”ĪŻ

ż┐ż└Īó10nmźčź┐Ī╝ź¾ż“ż│ż╬ŗī2└ż┬Õż╬EUVźĻźĮź░źķźšźŻäóÅøżŪ└┌żļż╚żżż├żŲżŌź▀ź├źĘźńź¾ź»źĻźŲźŻź½źļż╩ź╣źżĪ╝ź╚ź╣ź▌ź├ź╚żŪ╣ŌNAäóÅøż“╗╚ż”ż│ż╚ż╦ż╩żļż└żĒż”ż╚PhilipsĢ■żŽĮęż┘żŲżżżļĪŻ10nmż╬źčź┐Ī╝ź¾ż╚ż╩żņżąĪóźšź®ź╚źņźĖź╣ź╚żŌ10nm░╩▓╝ż╦Ū÷ż»ż╣żļØŁ═ūż¼żóżļĪŻźņźĖź╣ź╚ż╚═▀żĘżżźčź┐Ī╝ź¾ż╚ż╬źóź╣ź┌ź»ź╚╚µż¼╣Ōż»ż╩żļż│ż╚ż“╣═ż©żņżąĪóźßź╚źĒźĒźĖĪ╝Č\ĮčżŪż╬┘ć│╬ż╩Øó╦Īż“▒R─Ļż╣żļČ\ĮčżŌ─_═ūż╦ż╩żļĪŻ2nmźūźĒź╗ź╣ź╬Ī╝ź╔żŽĪóŽ¬Ė„äóÅøż└ż▒żŪżŽż╩ż»ĪóźņźĖź╣ź╚Īó┼╔╔█äóÅøĪóĖĮćĄĪóź©ź├ź┴ź¾ź░ż“┤▐żßż┐źĻźĮź░źķźšźŻ┴Ē╣ń╬üż¼╠õż’żņżļżĶż”ż╦ż╩żĻżĮż”ż└ĪŻ

ä▌ź¬źņź┤ź¾ä”ź▌Ī╝ź╚źķź¾ź╔ŖZ╣┘ż╬źęźļź║ź▄źĒĪ╝ż╦żóżļIntelż╬ź¬źņź┤ź¾╣®ŠņżŪżŽĪ󟬟ķź¾ź└ż½żķȧ═óżŪ╣ŌNA EUVäóÅøż“╚┬Ų■żĘżŲżŁżŲż¬żĻĪóżĮż╬══╗ęż“YouTubeżŪĮo│½żĘżŲżżżļĪ╩╗▓╣═½@╬┴1Ī╦ĪŻź¬źķź¾ź└żŪ×æļ]żĘżŲżżżļEUVäóÅøż“250“v╚óż╦╩¼▓“żĘĪó43Ė─ż╬ź│ź¾źŲź╩ż“▓▀ر└ņ├ōĄĪż╦┼ļ║▄żĘżŲź¬źķź¾ź└ż½żķźĘźóź╚źļȧ╣┴ż▐żŪ▒┐ż¾ż└ĪŻĮj(lu©░)Ę┐ź╚źķź├ź»20±ś╩¼ż╦╩¼ż▒żŲȧ╣┴ż½żķIntelż╬ź¬źņź┤ź¾╣®Šņż▐żŪ╚┬Ų■żĘż┐ĪŻ

┐▐3ĪĪĖ─Ī╣ż╬źŌźĖźÕĪ╝źļż╦╩¼▓“ĪóżĮżņżŠżņż“źŲź╣ź╚▓─ē”ż╦żĘżŲź¬źķź¾ź└ż½żķ╚┬┴„żĘż┐źųźĒź├ź»ż“ź¬źņź┤ź¾żŪ┴╚ż▀╬®żŲż┐ĪĪĮąųZĪ¦Intel

ĘQźŌźĖźÕĪ╝źļżŽź¬źņź┤ź¾╣®ŠņŲŌżŪ┴╚ż▀╬®żŲż┐Ī╩┐▐3Ī╦ĪŻżĮżņżŠżņż╬źĄźųźĘź╣źŲźÓżŽźŲź╣ź╚▓─ē”ż╩źŌźĖźÕĪ╝źļż╦╩¼▓“żĄżņĪóżĮżņżŠżņż“źŲź╣ź╚żŪżŁżļżĶż”ż╦żĘżŲżżżļĪŻ╝ń═ūż╩źŌźĖźÕĪ╝źļż╚żĘżŲżŽźņź┴ź»źļźŌźĖźÕĪ╝źļĪóĖ„│žÅUźŌźĖźÕĪ╝źļĪ󟔟¦Ī╝źŽż“┼ļ║▄ż╣żļź”ź¦Ī╝źŽźŌźĖźÕĪ╝źļĪóźņĪ╝źČĪ╝Ņ~Ų░äóÅøĪóĖ„Ė╗źŌźĖźÕĪ╝źļż╩ż╔ż¼żóżļĪŻżĄżķż╦ź╣źļĪ╝źūź├ź╚ż“æųż▓żļż┐żßż╬TWINSCANź╣źŲĪ╝źĖČ\ĮčżõĪó╚∙║┘▓├╣®ż╦╔į▓─’L(f©źng)żŪIJ┼└┐╝┼┘ż“┐╝ż»ż╣żļźóź╩źŌźšźŻź├ź»ż╩╚┐╝oÅUĖ„│žźŌźĖźÕĪ╝źļż╩ż╔ż“┴╚ż▀╬®żŲżŲżżż»ĪŻ

╗▓╣═½@╬┴

1. "Intel Adds ASMLĪŪs First High NA EUV Tool to Oregon Factory", YouTube