NANDźšźķź├źĘźÕż“16Ė─┤╔═²ż╣żļĘ╚┬ėĄĪ▀_(d©ó)Ė■ż▒╝■╩šź┴ź├źūż“Cypressż¼│½╚»

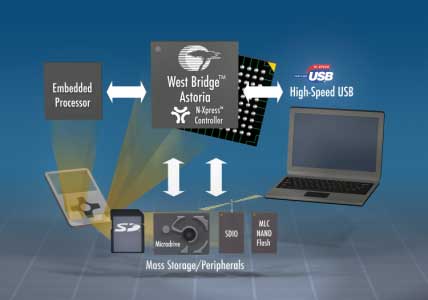

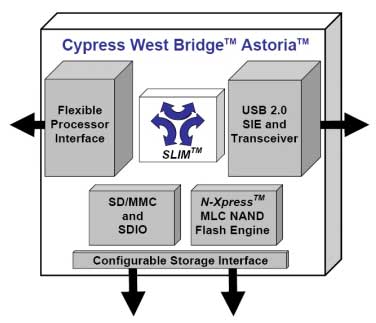

┴╚ż▀╣■ż▀źĘź╣źŲźÓż╬╝■╩šź┴ź├źūżŪżóżļź”ź¦ź╣ź╚źųźĻź├źĖż╚Ō}żų╝■╩šLSIĪųAntiochĪūż“ä▌(sh©¼)Cypress Semiconductor╝ęż¼║“ŃQ╚»ŪõżĘż┐ż¼Īóż│ż╬ż█ż╔Ę╚┬ėĄĪ▀_(d©ó)żžż╬┴╚ż▀╣■ż▀źĘź╣źŲźÓż“┴T╝▒żĘĪó¾Hźėź├ź╚/ź╗źļż╬NANDźšźķź├źĘźÕż“16ź┴ź├źūźĄź▌Ī╝ź╚żĘĪóSD/MMICź½Ī╝ź╔ż╬źĄź▌Ī╝ź╚żõSDźżź¾ź┐źšź¦Ī╝ź╣ż╩ż╔ż“äė(d©░ng)▓ĮżĘż┐╝■╩šź┴ź├źūĪųAstoriaĪūż“│½╚»Ī󟥟¾źūźļĮą▓┘żĘż┐ĪŻ

┴╚ż▀╣■ż▀źĘź╣źŲźÓżŪż╬ź”ź¦ź╣ź╚źųźĻź├źĖż╚Ō}żų╝■╩šź┴ź├źūżŽĪóźčźĮź│ź¾źĘź╣źŲźÓżŪCPUż╚źßźŌźĻĪ╝ż“ż─ż╩ż░ź╬Ī╝ź╣źųźĻź├źĖĪ󿥿ķż╦żĮż╬ź╬Ī╝ź╣źųźĻź├źĖż╚╝■╩šĄĪ▀_(d©ó)ż╚ż“ż─ż╩ż░źĄź”ź╣źųźĻź├źĖż“┐┐ō¶żŲĪó┴╚ż▀╣■ż▀źĘź╣źŲźÓż╬CPUż╚╝■╩šĄĪ▀_(d©ó)ż“±Tżų?j©½n)vŽ®ż“ź”ź¦ź╣ź╚źųźĻź├źĖż╚Ō}ż¾żŪżżżļĪŻźčźĮź│ź¾░╩│░ż╦źūźĒź╗ź├źĄż╚źßźŌźĻĪ╝Īó╝■╩šźĘź╣źŲźÓż½żķż╩żļ┴╚ż▀╣■ż▀źĘź╣źŲźÓżŪżŽĪó“£═Ķż╬CPUżŽ╝■╩šĄĪ▀_(d©ó)ż╚ż─ż╩ż▓żļż┐żßż╬źżź¾ź┐źšź¦Ī╝ź╣ż“ż╣ż┘żŲźĄź▌Ī╝ź╚żĘżŲżżż╩ż½ż├ż┐ĪŻ

ż│ż╬żĶż”ż╩ź”ź¦ź╣ź╚źųźĻź├źĖź┴ź├źūż¼żóżņżąĪóCPUż╚╝■╩šż╚ż╬żõżĻŲDżĻż¼ź╣źÓĪ╝ź║ż╦ż╩żļæųĪ󿥿ķż╦╣ŌÅ]ż╬╝■╩šźżź¾ź┐źšź¦Ī╝ź╣ż¼┼ąŠņż╣żļ╗■ż╦żŌ×┤▒■żŪżŁżļĪŻ╗■ż╦żŽCPUż╦╔ķ├┤ż“ż½ż▒żļż│ż╚ż╩ż»╝■╩šż½żķźßźŌźĻĪ╝żžĪóżóżļżżżŽ╝■╩šż½żķ╝■╩šżžż╚─Š└▄żõżĻŲDżĻżŪżŁĪóCPUżžż╬╔ķ├┤ż“Ę┌ż»ż╣żļż│ż╚ż¼żŪżŁżļĪŻż┴ż╩ż▀ż╦ż│ż╬ź┴ź├źūż“╗╚ż├ż┐Ę╚┬ė┴╚ż▀╣■ż▀źĘź╣źŲźÓżŪ1Gźąźżź╚ż╬źŪĪ╝ź┐ż“ź└ź”ź¾źĒĪ╝ź╔ż╣żļ╗■┤ųżŽĪóżĮż╬ź┴ź├źūż“╗╚ż’ż╩żżĘ╚┬ė┼┼ÅBżõĪóź╣ź▐Ī╝ź╚źšź®ź¾ż╚╚µż┘żŲ1/6Ī┴1/32ż╬╗■┤ųżŪ║čżÓż╚żżż”╝┬┘xż“╣įż├żŲżżżļĪŻ

║“ŃQ│½╚»żĘż┐ź”ź¦ź╣ź╚źųźĻź├źĖź┴ź├źūAntiochżŽĪóUSBż¬żĶżėź▐ź╣ź╣ź╚źņĪ╝źĖź│ź¾ź╚źĒĪ╝źķż╚CPUż╚ż“ż─ż╩żżż└ż¼Īóźšźķź├źĘźÕż╚ż╬└▄¶öżŽ2źąź¾ź»żĘż½źĄź▌Ī╝ź╚żĘżŲżżż╩ż½ż├ż┐ĪŻ

║Żöv│½╚»żĘż┐ŗī2└ż┬Õż╬ź”ź¦ź╣ź╚źųźĻź├źĖź┴ź├źūAstoriażŽĪó║ŪĮj(lu©░)16Ė─ż╬¾H├═Ī╩4źėź├ź╚ż▐żŪĪ╦NANDźšźķź├źĘźÕź┴ź├źūżõĪóSDźżź¾ź┐źšź¦Ī╝ź╣ż╩ż╔ż“źĄź▌Ī╝ź╚żĘżŲżżżļĪŻ¾H├═NANDż╦ż│ż└ż’żļż╬żŽĪóź«ź¼źąźżź╚┼÷ż┐żĻż╬▓┴│╩ż¼1źėź├ź╚/ź╗źļż╬NANDźšźķź├źĘźÕżĶżĻżŌŖWżżż½żķżŪżóżļĪŻżĘż½żĘ¾H├═NANDźšźķź├źĘźÕżŽ1źėź├ź╚/ź╗źļż╚╚µż┘żŲĮ±żŁ╣■ż▀╗■┤ųż¼─╣żżż╩ż╔ż╬╠õ¼öż¼żóżĻĪóĖĒżĻÖÄ┘ćżõźųźĒź├ź»┤╔═²Īó╔į╬╔źėź├ź╚ż╬╩┐ØŹ▓Įż╩ż╔ż¼žMżĘż½ż├ż┐ĪŻ

AstoriażŽż│ż╬żĶż”ż╩╠õ¼öż“▓“»éżĘĪóN-Xpressż╚Ō}żųźšźķź├źĘźÕź│ź¾ź╚źĒĪ╝źķövŽ®ż“│½╚»żĘż┐ĪŻż│ż╬ź│ź¾ź╚źĒĪ╝źķövŽ®ż╦żŽĪó║ŪĮj(lu©░)4źėź├ź╚ż▐żŪĖĒżĻÖÄ┘ćżŪżŁżļReed-Solomon╔õęÄ(gu©®)ż╦żĶżļECCĪ╩ĖĒżĻĖĪĮąÖÄ┘ćĪ╦övŽ®Īó╔į╬╔źųźĒź├ź»ż╬┤╔═²övŽ®Īó╔į╬╔źėź├ź╚ż╬╩┐ØŹ▓ĮövŽ®ż“ŲŌē┼żĘż┐ĪŻżĄżķż╦ź└źżź╩ź▀ź├ź»ż╩źżź¾ź┐źĻĪ╝źų?j©½n)vŽ®ż“NANDźšźķź├źĘźÕż╚ż╬źżź¾ź┐źšź¦Ī╝ź╣ż╦└▀ż▒Īó16Ė─ż╬NANDźšźķź├źĘźÕż“┤╔═²żŪżŁżļżĶż”ż╦żĘż┐ĪŻźżź¾ź┐źĻĪ╝źų?j©½n)vŽ®żŽ8źėź├ź╚źąź╣ż¼2╦▄żóżĻĪóżĮżņżŠżņ8Ė─ż║ż─ż╬NANDźšźķź├źĘźÕż“ż─ż╩ż░ż│ż╚ż¼żŪżŁżļĪŻ

żĄżķż╦SD/MMICź½Ī╝ź╔ż╩ż╔ż╬ź╣ź╚źņĪ╝źĖźŪźąźżź╣ż╚ż╬źżź¾ź┐źšź¦Ī╝ź╣żõSDIOźżź¾ź┐źšź¦Ī╝ź╣övŽ®ż╬ź©ź¾źĖź¾żŌ└▀ż▒ż┐ĪŻżŌż┴żĒż¾Īó“£═Ķż╬Antiochż╚Ų▒══Īó┴╚ż▀╣■ż▀źūźĒź╗ź├źĄż╚ż╬źżź¾ź┐źšź¦Ī╝ź╣övŽ®żõĪóźčźĮź│ź¾ż╩ż╔ż╚ż╬USB2.0źżź¾ź┐źšź¦Ī╝ź╣żŌ└▀ż▒żŲżżżļĪŻ

ĖĒżĻÖÄ┘ćövŽ®żŪżŽĪó4źėź├ź╚/ź╗źļż╬Šņ╣ńżŪżĄż©Īóź╗źļŲŌż└ż▒żŪżŽż╩ż»ź╗źļ┤ųż╬źėź├ź╚ĖĒżĻż╦×┤żĘżŲżŌĖĪĮąÖÄ┘ćżŪżŁżļĪŻźßźŌźĻĪ╝ź╗źļż╦żŽ┤žĘĖż╩żżĪŻź╗źļż╬Ū█ÅøżŽĪó1źųźĒź├ź»┼÷ż┐żĻ512źąźżź╚ż½żķż╩żļĪŻż┐ż└żĘĪó¾H├═ź╗źļż╬NANDźšźķź├źĘźÕżŪżŽ3źėź├ź╚/ź╗źļż▐żŪż¼ĖĮ╝┬┼¬ż╦└▀╝ŖżŪżŁżļ¾H├═ż└ż╚źšźķź├źĘźÕźßĪ╝ź½Ī╝żŽĖ½żŲżżżļĪŻ

ż│żņż└ż▒ż╬övŽ®ż“ŲŌē┼żĘżŲż¬żŁż╩ż¼żķĪóŠ├õJ┼┼╬üżŽ░╩Øiż╬Antiochż╚Ų▒żĖµć┼┘żŪĪóź╣ź┐ź¾źąźż╗■ż╦50”╠AĪóŲ░║Ņ╗■żŽ┐¶100mAż└ż╚żżż”ĪŻ┼┼Ė╗┼┼░ĄżŽ1.8VĪ┴3.3VĪŻźčź├ź▒Ī╝źĖżŽ6mmĪ▀6mmżŪĪóź▄Ī╝źļźįź├ź┴0.5mmż╬BGAĪŻ═ĶŃQØi╚Šż╦żŽ╬╠ŠÅż╦Ų■żļĪŻ▓┴│╩żŽØiövż╬ź┴ź├źū╩┬ż▀ż└ż╚żĘżŲżżżļĪŻ