NECĪó3Ū▄└Łē”żõ1/5░╩▓╝ż╬▓┴│╩ż╩ż╔4ēä¹|ż╬┘Z║▄├ō▓ĶćĄŪ¦╝▒źūźĒź╗ź├źĄż“│½╚»

NECź©źņź»ź╚źĒź╦ź»ź╣ż¬żĶżėNECżŽĪó┘Z║▄├ō▓ĶćĄŪ¦╝▒└ņ├ōż╬źūźĒź╗ź├źĄIMAPCAR2ż“│½╚»ĪóNECź©źņź»ź╚źĒź╦ź»ź╣ż¼2009ŃQæų┤³ż½żķĮń╝ĪźĄź¾źūźļĮą▓┘ż“żĘżŲżżż»═Į─ĻżŪżóżļĪŻNECź©źņź»ź╚źĒź╦ź»ź╣żŽ┘Z║▄├ōż╬ź▐źżź»źĒź│ź¾ź╚źĒĪ╝źķ(ź▐źżź│ź¾)ż╬▌xŠņźĘź¦źóżŽŗī3░╠żŪĪóĖ─╩╠╚ŠŲ│öüżŪżŌ┘Z║▄├ōż“Ęeż├żŲżżżļż¼ĪóSoCż╬ŪõżĻæųż▓żŽŠ«żĄżżĪŻż│ż╬ż┐żßĪóż│ż╬▓ĶćĄĮĶ═²└ņ├ōźūźĒź╗ź├źĄIMAPCAR2żŪźŽźżź©ź¾ź╔ż½żķźĒĪ╝ź©ź¾ź╔ż▐żŪź»źļź▐ż╬ŖWµ£ż“├┤ż”├ō²ŗż“│╚ĮjżĘżŲżżż»┴└żżż¼żóżļĪŻ

▓ĶćĄĮĶ═²└ņ├ōźūźĒź╗ź├źĄż╚żĘżŲNECź©źņź»ź╚źĒź╦ź»ź╣żŽ2006ŃQż╦IMAPCARż╚żżż”źųźķź¾ź╔ć@żŪŪõżĻĮążĘż┐ż¼Īó╣ŌĄķ┘Z¹|ż╦żĘż½┼ļ║▄żĄżņż║ĪóŪõżĻæųż▓│╚Įjż╦żŽż╚żŲżŌż─ż╩ż¼żķż╩ż½ż├ż┐ĪŻ║ŻövżŽĪ󟎟żź©ź¾ź╔ż½żķźĒĪ╝ź©ź¾ź╔ż▐żŪ4ēä¹|ż“żĮżĒż©Īó║ŪĮķż╬×æēäż╚Ų▒┼∙└Łē”ż╩żķ1/5ż╬▓┴│╩Īó║Ū╣Ō└Łē”ż╬×æēäż╩żķ3Ū▄ż╬└Łē”ż“├Ż└«żĘżŲżżżļż╚żżż”ĪŻ║Ū╣Ō└Łē”ż╬Šņ╣ńĪó“£═Ķż╬└Ķ╣įŪvŪ¦╝▒żõźņĪ╝ź¾Ū¦╝▒ż╚żżż”├▒ĮŃż╩ĄĪē”ĪóżóżļżżżŽź╩źżź╚źėźĖźńź¾ż└ż▒ż╚żżż”├▒Ų╚ż╬ĄĪē”żĘż½╝┬╣įżŪżŁż╩ż½ż├ż┐ż¼Īó║Żövż╬└Łē”ż╩żķź╩źżź╚źėźĖźńź¾ż╦▓├ż©║Y╝▒ż╬Ū¦╝▒żŌżŪżŁżļż”ż©ż╦Īó╩Ō╣įŪvż╬Ū¦╝▒żŌ▓─ē”ż└ż╚żżż”ĪŻż│żņż▐żŪżŽ╬®öü┼¬ż╩رöüż╚żĘżŲż╬Ū¦╝▒żĘż½żŪżŁż╩ż½ż├ż┐ż¼Īó└Łē”ż¼Ė■æųżĘż┐±T▓╠Īó┐═┤ųżŪżóżļż╚żżż”źčź┐Ī╝ź¾Ū¦╝▒żŌżŪżŁżļż╚żĘżŲżżżļĪŻ

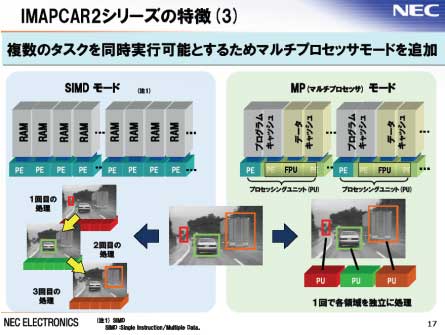

║Żövż╬IMAPCAR2żŽĪóźóĪ╝źŁźŲź»ź┴źŃżŌ╩čż©ż┐ĪŻŗī1└ż┬Õż╬IMAPCARżŽŲ▒żĖźūźĒź╗ź├źĄź©źņźßź¾ź╚PEż“128Ė─╩┬š`ĮĶ═²ż╣żļSIMDĪ╩single instruction multiple dataĪ╦źóĪ╝źŁźŲź»ź┴źŃż└ż├ż┐ż¼Īó║ŻövżŽŲ▒żĖ128źūźĒź╗ź├źĄź©źņźßź¾ź╚ż╩ż¼żķĪóĘQźūźĒź╗ź├źĄź©źņźßź¾ź╚ż╬╣Į└«żŌ╩čż©ż┐ĪŻ“£═ĶżŽĘQPEż╦RAMż“║▄ż╗ż┐żŌż╬ż“1├▒░╠ż╚żĘż┐ż¼Īó║ŻövżŽĘQPEż╦╔ŌŲ░Š«┐¶┼└▒ķōQźµź╦ź├ź╚Ī╩FPUĪ╦ż╚źūźĒź░źķźÓźŁźŃź├źĘźÕż╚źŪĪ╝ź┐źŁźŃź├źĘźÕż╬źßźŌźĻĪ╝ż“┼ļ║▄żĘż┐żŌż╬ż“1źūźĒź╗ź├źĘź¾ź░├▒░╠ż╚żĘż┐ĪŻ“£═ĶżŽŲ▒żĖ▓ĶćĄĮĶ═²ż“µ£ŗż╬PE+RAMżŪ╣įż├żŲżżż┐ż¼Īó║ŻövżŽĘQ├▒░╠ż╬źūźĒź╗ź├źĘź¾ź░źµź╦ź├ź╚ż╦Ų╚╬®ż╬▒ķōQż“╣įż©żļżĶż”ż╦żĘż┐ĪŻ

ż│żņż╦żĶż├żŲĪó╬Ńż©żąź»źļź▐ż╬ØiöĄż╦ŠĶ├ō┘Zż╚żĮż╬Øiż╦Š«Ę┐ź╚źķź├ź»Īóµuż╬źņĪ╝ź¾ż╦ĮjĘ┐ź╚źķź├ź»ż“ĖĪĮążĘż┐ż╚żĘżĶż”ĪŻżĮż╬ĖĪĮąż╦żŽĪóŗī1└ż┬Õē俎µ£öüż“ź╣źŁźŃź¾ż╣żļż│ż╚żŪ2ż─Øiż╬Š«Ę┐ź╚źķź├ź»ż“ĖĪĮążĘĪóżŌż”▐k┼┘ź╣źŁźŃź¾ż╣żļż│ż╚żŪØiż╬ŠĶ├ō┘Zż“Īó3övų`ż╬ź╣źŁźŃź¾żŪµuż╬ĮjĘ┐ź╚źķź├ź»ż“ĖĪĮąż╣żļĪŻż│ż╬ż┐żßĖĪĮą╗■┤ųż¼ż½ż½ż├żŲżżż┐ĪŻ║ŻövżŽĪóŠ«Ę┐ź╚źķź├ź»ĪóŠĶ├ō┘ZĪóĮjĘ┐ź╚źķź├ź»ż“żĮżņżŠżņ▐kż─ż╬źūźĒź╗ź├źĘź¾ź░├▒░╠ż║ż─ż╦żĶż├żŲĖĪĮąż╣żļĪŻĘQźūźĒź╗ź├źĘź¾ź░├▒░╠ż¼░█ż╩żļĮĶ═²ż“ż╣żļ┼└ż¼Øiövż╬IMAPCARż╚ĮjżŁż»░Ńż”ĪŻ

IMAPCAR2ż╦żŽĪ󟎟żź©ź¾ź╔ż╬IMAPCAR2-300ż½żķĪóźĒĪ╝ź©ź¾ź╔ż╬IMAPCAR2-50ż▐żŪĪó²ŗ├µż╦-200Īó-100ż╚żżż”ēä¹|żŌ▓├ż’żļĪŻ-300żŽźūźĒź╗ź├źĄ┐¶128Ė─żŪĪó└Łē”ż¼270GOPSĪ╩giga operations per secondĪ╦Īó-200ż¼źūźĒź╗ź├źĄ┐¶64Ė─żŪ170GOPSĪó-100żŽźūźĒź╗ź├źĄ┐¶64Ė─żŪŲ░║Ņ╝■āS┐¶ż“66MHzż╚╚ŠžōżĘżŲ84GOPSĪó-50ż¼źūźĒź╗ź├źĄ┐¶32Ė─żŪ42GOPSż╚żżż”ź╣ź┌ź├ź»żŪżóżļĪŻż│ż╬ż”ż┴-100ż¼“£═Ķż╬IMAPCARż╚Ų▒┼∙ż╬└Łē”ż“Ęeż─ż╚żĘżŲżżżļĪŻ

ż│żņżķż╬×æēäż╬ż”ż┴Ī󟎟żź©ź¾ź╔ż╬-300ż“ź┘Ī╝ź╣ż╦└▀╝ŖżĘĪóżĮż╬źóĪ╝źŁźŲź»ź┴źŃż“▓╝░╠ż╦·t│½żĘż┐ĪŻ╗■┤ų┼¬ż╩öU╠¾ż½żķ-300ż╦żŽ90nmźūźĒź╗ź╣Īóż█ż½ż╬3ēä¹|ż╦żŽ55nmźūźĒź╗ź╣ż“┼¼├ōż╣żļĪŻŗī1└ż┬Õż╬×æē俎130nmźūźĒź╗ź╣ż└ż├ż┐ż┐żßĪóź┴ź├źūźĄźżź║żŽŠ«żĄż»ż╩ż├ż┐ż╚żĘżŲżżżļĪŻ╝²żßżļźčź├ź▒Ī╝źĖżŽĪó-300ż¼780źįź¾FCBGAĪó-200ż╚-100żŽ357źįź¾FCBGAĪó-50żŽ208źįź¾QFPż“═Į─ĻżĘżŲżżżļĪŻ