nMOSź╚źķź¾źĖź╣ź┐ż╬żążķż─żŁżŽ╔įĮŃرż└ż▒żŪżŽ»éż▐żķż╩żż

65nmźĒźĖź├ź»źūźĒź╗ź╣Ī╩źŽĪ╝źšźįź├ź┴żŪżŽ90nmźūźĒź╗ź╣ż╦┴Ļ┼÷ż╣żļźūźĒź╗ź╣ź╬Ī╝ź╔hp90Ī╦żŪ100╦³Ė─ż╬nź┴źŃź¾ź═źļ/pź┴źŃź¾ź═źļMOSź╚źķź¾źĖź╣ź┐źóźņźżĪ╩╬ŠöĄżŪ200╦³Ė─Ī╦ż“║ŅżĻĪóź▓Ī╝ź╚żĘżŁżż┼┼░ĄVthż╬żążķż─żŁż╬ĖČ░°ż“Ų═żŁ┘Vżßż┐Īóż╚╚ŠŲ│öüMIRAIźūźĒźĖź¦ź»ź╚ż¼Īó12ĘŅ18Ų³░±ŠļĖ®ż─ż»żą▌xżŪ│½ż½żņż┐2007ŃQ╚ŠŲ│öüMIRAIźūźĒźĖź¦ź»ź╚└«▓╠╩¾╣▓±żŪ╚»╔ĮżĘż┐ĪŻpź┴źŃź¾ź═źļMOSż╬żążķż─żŁżŽ╔įĮŃرż╬═æżķż«ż╦żĶżĻĪónź┴źŃź¾ź═źļMOSżŽ╔įĮŃرż╬═æżķż«ż╚╩╠ż╬═ū░°ż¼▓├ż’ż├żŲżżżļż╚żĘżŲżżżļĪŻ

ż│ż╬╝┬┘xżŪżŽĪóMillennium Research for Advanced Information Technology (MIRAI)źūźĒźĖź¦ź»ź╚ż¼Īó200mmź”ź¦Ī╝źŽż╬├µż╦26Ė─ż╬TEGź┴ź├źūż“║ŅżĻĪóĘQTEGź┴ź├źūż╦żŽ20Ė─ż╬źĄźųź┴ź├źūż“║Ņż├ż┐ĪŻ20Ė─ż╬źĄźųź┴ź├źūż╬├µż╦Īó100╦³Ė─ż╬ź╚źķź¾źĖź╣ź┐źóźņźżŗ╩¼ż“nż¬żĶżėpź┴źŃź¾ź═źļ2ź½ĮĻ└▀ż▒ż┐żŌż╬żŪĪóĘQ100╦³Ė─ż╬nMOSź╚źķź¾źĖź╣ź┐Īó100╦³Ė─ż╬pMOSź╚źķź¾źĖź╣ź┐ż½żķż╩żļĪŻźóźņźżż╬ź╚źķź¾źĖź╣ź┐żŽnMOSĪópMOSż╚żŌż╣ż┘żŲŲ▒żĖĖ■żŁż╦║ŅżĻ╣■ż¾ż└ĪŻż│ż╬żĶż”ż╩Įj╬╠ż╬ź╚źķź¾źĖź╣ź┐źóźņźżż“╗╚ż├żŲźĄźųź╣źņź├źĘźńźļź╔┼┼╬«ØŖ└ŁżõVthż“▒R─ĻżĘżążķż─żŁż“äh▓┴żĘż┐ĪŻ

100╦³Ė─ż╬ź╚źķź¾źĖź╣ź┐ż╦ż─żżżŲ▒R─ĻżĘż┐Vthż“Īó╩Å└č╔č┼┘ż“┐āż╣ź’źżźųźļ╩¼╔█ż╚żĘżŲż▐ż╚żßżļż╚Ī󿣿ņżżż╩─Š└■ėXż“ķWżŁĪó┘ćæä╩¼╔█żĘżŲżżżļż│ż╚ż¼ż▐ż║ż’ż½ż├ż┐ĪŻżĘż½żŌĪóż│ż╬VthżŽ├µ▒¹├═ż½żķĪ▐5”ęĪ╩”꿎║YØŹ╩ą║╣Ī╦ż╚ż½ż╩żĻ╣ŁżżšJ░Žż╦Ą┌ż¾żŪżżżļĪŻż┐ż└żĘĪóżĮż╬1”꿎pMOSż¼43mVżŪżóżļż╬ż╦×┤żĘżŲĪónMOSżŽ65mVĪóż╚żążķż─żŁżŽpMOSżĶżĻżŌĮjżŁż½ż├ż┐ĪŻ

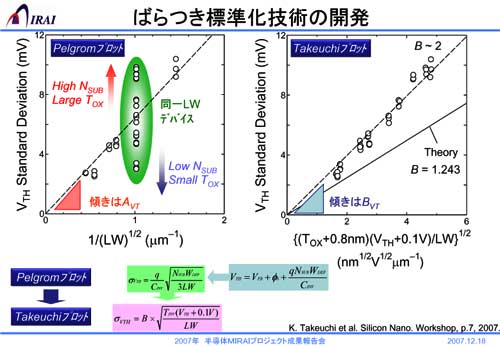

żążķż─żŁż╬ĖČ░°ż“├Ążļż┐żßĪóźūźĒźĖź¦ź»ź╚żŽVthż“ź╬Ī╝ź▐źķźżź║żĘżŲ╔ĮĖĮż╣żļż│ż╚ż“╣═ż©ż┐ĪŻź╬Ī╝ź▐źķźżź║ż╬Š}╦Īż╚żĘżŲĪóVthż╬żążķż─żŁ”ęĪ╩║YØŹ╩ą║╣Ī╦ż╚ź▓Ī╝ź╚─╣Lż╚ź▓Ī╝ź╚╔²WżŪ╔Įż╣öĄ╦Īż¼żóżļż¼Īóż│żņżŪżŽź▓Ī╝ź╚¤©▓Į╦ņĖ³żõ╔įĮŃرŪ╗┼┘ż╦żĶż├żŲ─Š└■└Łż¼ĮjżŁż»╩°żņż┐ĪŻżĮż│żŪĪóźūźĒźĖź¦ź»ź╚żŪżŽĪóVthż╬║YØŹ╩ą║╣ż“(ToxĪ▄0.8nm)(VthĪ▄0.1V) / LWż╬źļĪ╝ź╚żŪźūźĒź├ź╚żĘżŲż▀żļż╚ĪóVthż╬żążķż─żŁżŽ─Š└■┼¬ż╦╔Įż╣ż│ż╚ż¼żŪżŁż┐ĪŻ

ż│ż│żŪĪóToxż╬ź▓Ī╝ź╚¤©▓Į╦ņĖ³ż╦0.8nmż“▓├ż©ż┐╬╠żŽMOS╚┐┼Šż“ÅŚż│żĘż┐╗■ż╬╝┬Ė·┼¬ż╩Ī╩żóżļżżżŽ┼┼Ąż┼¬ż╩Ī╦¤©▓Į╦ņĖ³ż“╔ĮżĘż┐żŌż╬żŪżóżļĪŻż▐ż┐ĪóVthĪ▄0.1VżŽĪóVthż╦ż¬ż▒żļźßź┐źļż╚╚ŠŲ│öüż╚ż╬╗┼Ą£┤ž┐¶ż╬║╣ż½żķż╩żļźšźķź├ź╚źąź¾ź╔┼┼░ĄĪ󿬿Ķżė╔ĮĀCź▌źŲź¾źĘźŃźļż╬┤¾═┐╩¼-0.1Vż“▓├╠ŻżĘż┐żŌż╬żŪĪó╝┬Ė·┼¬ż╦qNWdep/Coxż╚żżż”╝░żŪ╔Įż’żĄżņżļĪ╩WdepżŽČ§Ēś┴žż╬╔²ĪóCoxżŽź▓Ī╝ź╚¤©▓Į╦ņĖ³Ī╦ĪŻż─ż▐żĻĪóVthż╬żążķż─żŁżžż╬┤¾═┐ż¼╔įĮŃرŪ╗┼┘ż╬żążķż─żŁżŪżŽż╩żżż½ż╚żżż”▓Š└Ōż╬żŌż╚ż╦ĪóVthż╬żążķż─żŁĪóż╣ż╩ż’ż┴”ęż“╔įĮŃرŪ╗┼┘Nż¼┤¾═┐ż╣żļ╝░żŪź╬Ī╝ź▐źķźżź║żĘż┐ĪŻ

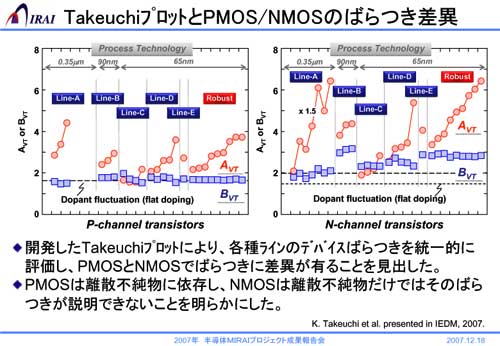

╝┬║▌ż╦żŽ┐▐ż╦┐āżĄżņżļżĶż”ż╦ĪópMOSż╚nMOSż╚żŪ░Ńż├ż┐±T▓╠ż¼įużķżņż┐ĪŻpMOSż╬Šņ╣ńĪó╔įĮŃرŪ╗┼┘ż¼░Ńż├żŲżŌ▐k─ĻżŪżóżļż┐żßĪóVthż╬żążķż─żŁżŽĮŃ┐Ķż╦╔įĮŃرŪ╗┼┘ż╬żążķż─żŁż└ż▒żŪ»éż▐żļż│ż╚ż¼ż’ż½ż├ż┐ĪŻżĘż½żĘĪónMOSżŪżŽ╔įĮŃرŪ╗┼┘ż¼░Ńż├żŲżŌżĮż╬’łżŁżŽż█ż▄▐k─Ļż└ż¼Ū╗┼┘ż¼╣Ōż»ż╩żļż╦ż─żņ’łżŁżŌ╣Ōż»ż╩żļ’łĖ■ż¼żóż├ż┐ĪŻż│ż╬ż┐żßĪóVthż╬żążķż─żŁż¼╔įĮŃرŪ╗┼┘ż└ż▒żŪżŽż╩ż»Īó┬Šż╬═ū┴ŪżŌ▓├ż’ż├żŲżżżļż╚╚ĮéāżĘż┐ĪŻ

źūźĒźĖź¦ź»ź╚żŪżŽĪóźšźķź├ź╚źąź¾ź╔┼┼░ĄĪó╚┐┼Š┴žż╬Ė³żĄĪóźĘĪ╝ź╚ź┴źŃĪ╝źĖĪ╩─cĀCØŹ░╠żõĪżź▓Ī╝ź╚└õ▒’╦ņ├µż╬╔w─Ļź┴źŃĪ╝źĖĪż─cĀCż╦źčźżźļźóź├źūżĘż┐╔įĮŃرĖČ╗ęż╩ż╔ż╬┴ĒŠ╬Ī╦ż╩ż╔ż¼żóżõżĘżżż╚ż╦żķż¾żŪżżżļż¼Īóż▐ż└éā─Ļż╣żļż╦żŽ╗Ļż├żŲżżż╩żżĪŻż│ż╬ż┐żßż╦¤©▓Į╦ņż╬Ė³żĄż╬żążķż─żŁżõ─cĀCż╬╣ėżņĪóż╩ż╔ż“ر═²┼¬ż╦▒R─Ļż╣żļż┐żßż╬Č\Įč│½╚»ż╚źĘź▀źÕźņĪ╝źĘźńź¾Č\Įčż╬│½╚»ż╦ŲDżĻ┴╚ż¾żŪżżżļĪŻ