2025年2月28日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

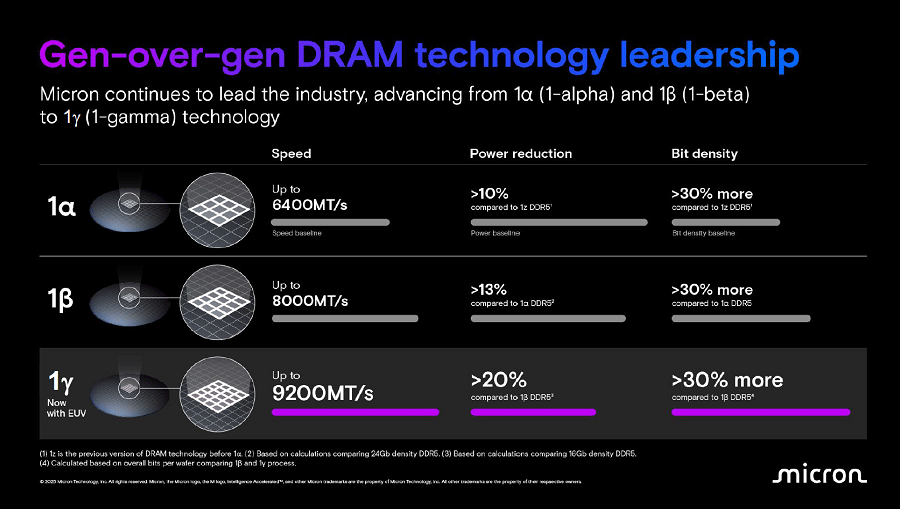

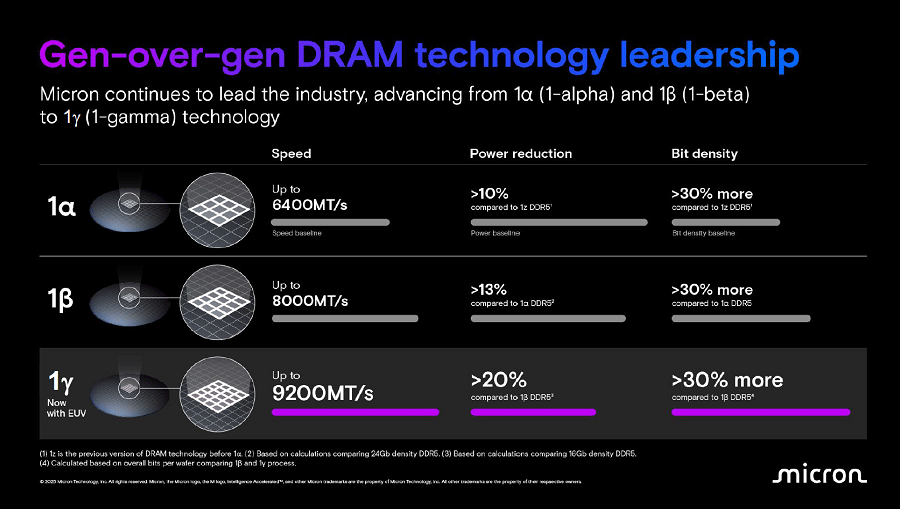

Micron Technologyż¼1γnmź╬Ī╝ź╔ż╬DDR5DRAMż“źĄź¾źūźļĮą▓┘żĘż┐ĪŻ1γnmż╚żżż”źĄźżź║żŽ10nmź»źķź╣ż╬żĶż”żŪĪóEUVäóÅøż╬Ų│Ų■ż¼ØŁ┐▄ż╦ż╩żļĪŻMicronż╬╚∙║┘ż╩Č\Įčż╦żĶż├żŲĪóź╣źįĪ╝ź╔żŽĖĮ└ż┬Õż╬1”┬nmź╬Ī╝ź╔ż╬DRAMż╚╚µż┘Īó8Gbpsż½żķ9.2Gbpsż╚╣ŌÅ]ż╦ż╩żĻĪóŠ├õJ┼┼╬üżŽ20%║’žōżĄżņĪóĮĖ└č┼┘żŽ30%æųż▓żļż│ż╚ż¼żŪżŁżļ(┐▐1)ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年7月 2日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

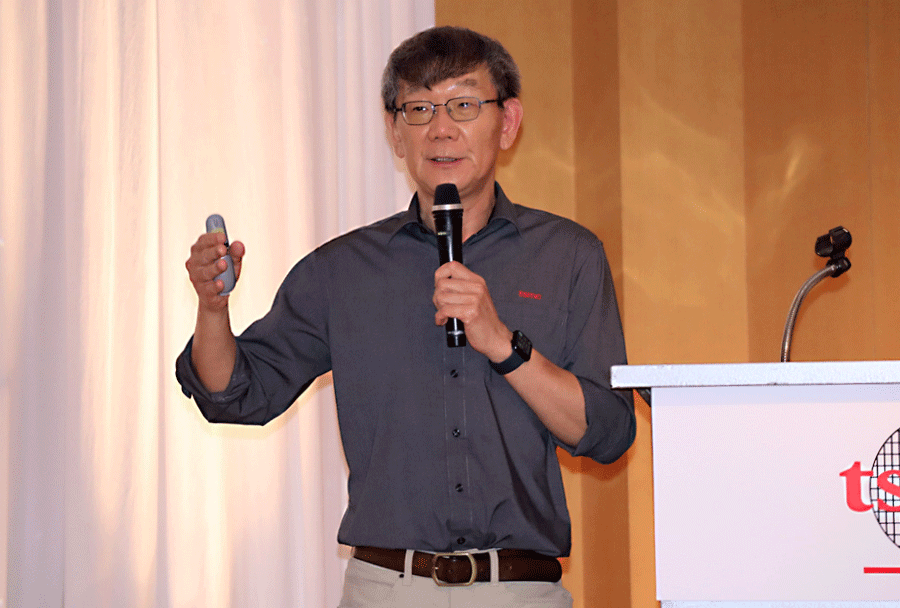

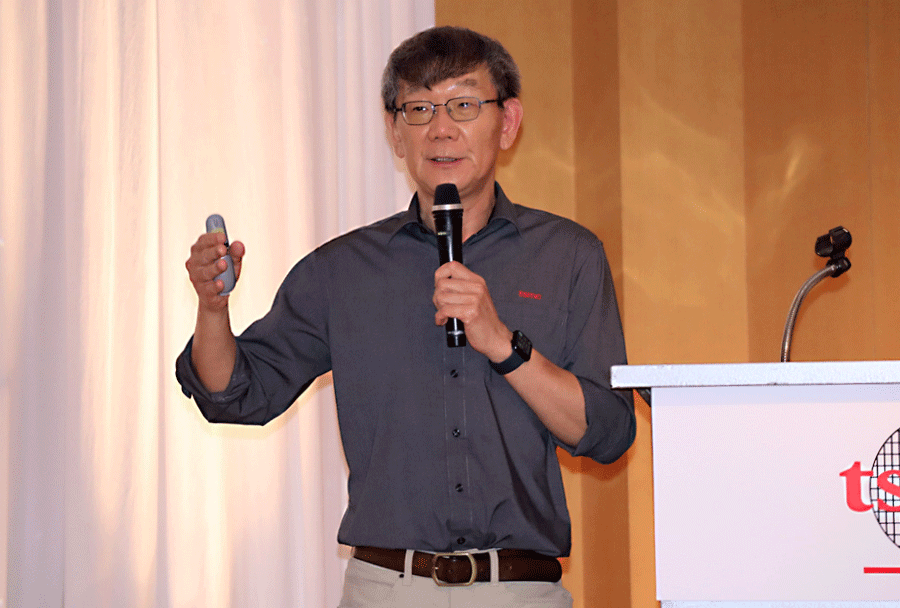

AIź│ź¾źįźÕĪ╝źŲźŻź¾ź░źčź’Ī╝ż¼ż▒ż¾░·żĘĪóźūźĒź╗ź╣ź╬Ī╝ź╔ż╬╚∙║┘▓ĮżŽ┴ßż▐ż├żŲżżżļĪóż╚TSMCźĘź╦źóźąźżź╣źūźņźĖźŪź¾ź╚Ę¾╔¹Č”Ų▒║Ū╣ŌČ╚ē»╝╣╣į└šŪżŪvż╬Kevin ZhangĢ■ż¼Įęż┘ż┐ĪŻż│żņżŽ6ĘŅ28Ų³ż╦▓Ż┘pżŪTSMC Technology Symposium Japanż“│½╠¢żĘż┐║▌ĪóźßźŪźŻźóĖ■ż▒Č\Įč└Ō£½▓±żŪĮęż┘ż┐żŌż╬ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

![2nmż╬ź▐ź╣ź»×æ║Ņ┤³┤ųż“│╩├╩ż╚ø]Į╠ż╣żļNvidiaż╬cuLithoż╚Synopsysż╬OPC 2nmż╬ź▐ź╣ź»×æ║Ņ┤³┤ųż“│╩├╩ż╚ø]Į╠ż╣żļNvidiaż╬cuLithoż╚Synopsysż╬OPC](/assets_c/900px/240328-culitho.png)

2024年3月28日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

2nmźūźĒź╗ź╣żŪżŽĪóEUVż╚żżż©ż╔żŌOPCĪ╩Ė„│ž┼¬ŖZ└▄Ė·▓╠T┘ćĪ╦ż¼ØŁ═ūż╦ż╩ż├żŲż»żļĪŻEUVż╬13.5nmż╚żżż”āS─╣żŪżŽźčź┐Ī╝ź¾ż“żĮż╬ż▐ż▐▓├╣®żŪżŁż╩ż»ż╩ż├żŲżŁż┐ż½żķż└ĪŻ2nmźūźĒź╗ź╣ż└ż╚╩Ż╗©ż╣ż«żŲ╗Ņ╣įēžĖĒ┼¬ż╩źóźūźĒĪ╝ź┴żŽżŌżŽżõ╗╚ż©ż╩żżĪŻ╝ŖōQĄĪŠW├ōż╬źĻźĮź░źķźšźŻż╬Įą╚ųż╚ż╩żļĪŻNvidiaż╚TSMCĪóSynopsysĪóASMLżŽĪó║“ŃQź©ź│źĘź╣źŲźÓż“╣Į├█żĘż┐ż¼Ī╩╗▓╣═½@╬┴1Ī╦ĪóTSMCż╬╬╠ŠÅźķźżź¾ż╦╝ŖōQĄĪźĻźĮż“Ų│Ų■żĘżŲżżżļż│ż╚ż¼£½żķż½ż╦ż╩ż├ż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年2月28日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

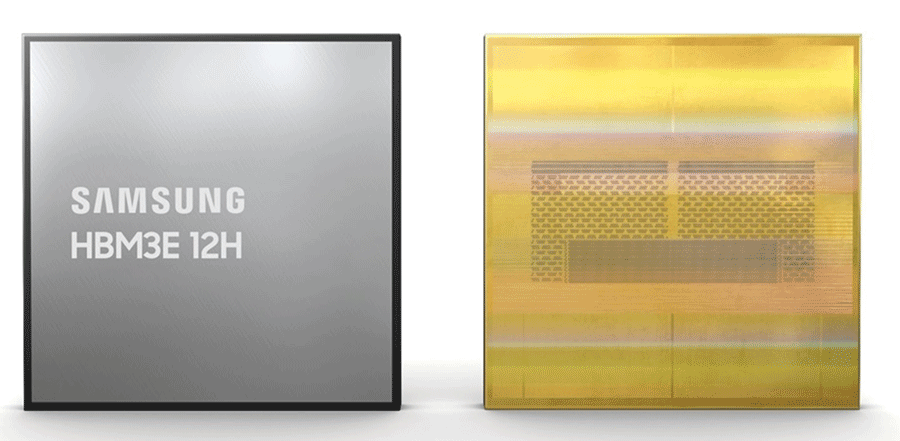

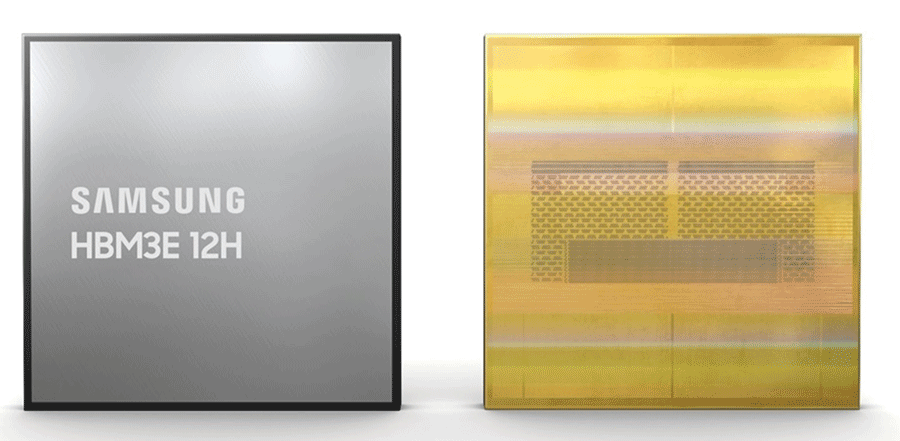

MicronĪóSamsungż¼3D-ICČ\Įčż“╗╚ż├ż┐DRAMźßźŌźĻżŪżóżļHBM3Eż“┴Ļ╝ĪżżżŪ×æēä▓ĮżĘż┐Ī╩┐▐1Ī╦ĪŻHBMźßźŌźĻżŽĮj═Ų╬╠ż╬źßźŌźĻż“▐k┼┘ż╦Įj╬╠ż╦╩┬š`Ų╔ż▀ĮążĘżŪżŁżļźŪźąźżź╣żŪżóżĻĪóAIź┴ź├źūżõSoCźūźĒź╗ź├źĄż╚▐kĮ’ż╦╗╚ż’żņżļĪŻSK hynixż¼ż│żņż▐żŪHBM1żõ2Īó3ż╬źßźŌźĻ×æēäż╦╬üż“Ų■żņżŲżŁż┐ż¼Īóź│ź╣ź╚ż¼ż½ż½żļż┐żß┬Š╝꿎żóż▐żĻ╬üż“Ų■żņżŲż│ż╩ż½ż├ż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年2月16日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

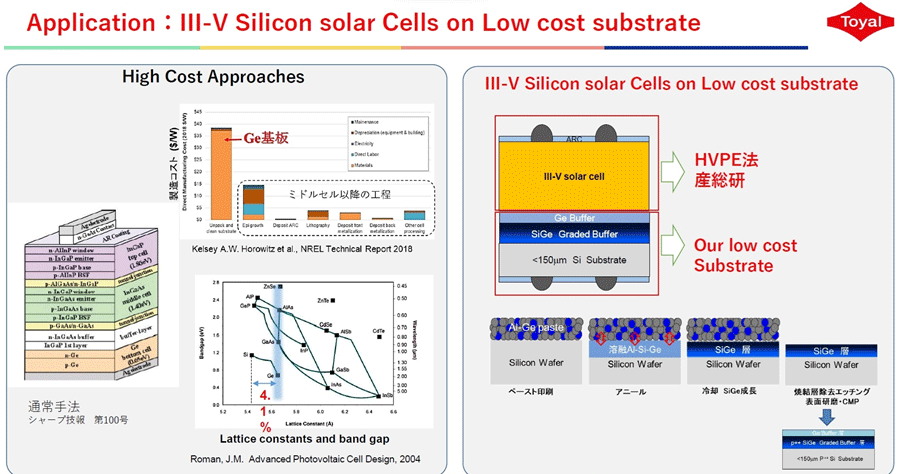

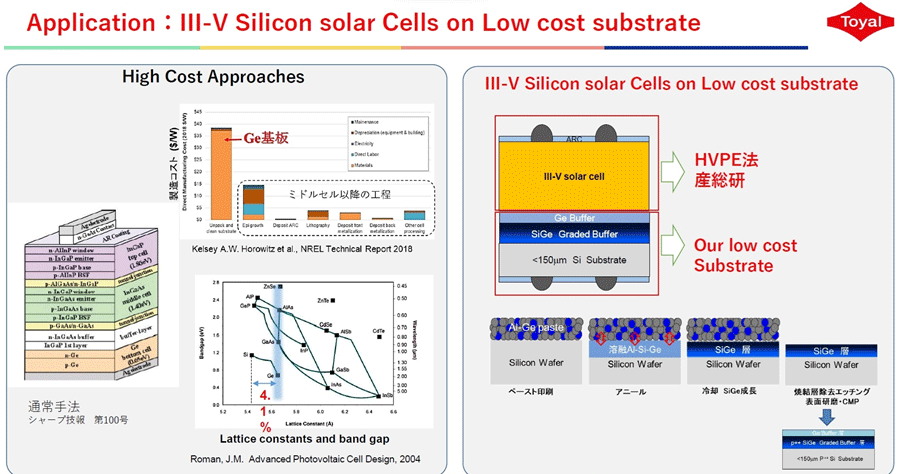

Si┤łæųż╦Ge┴žż“ø]╗■┤ųżŪŖW▓┴ż╦║Ņ×æż╣żļöĄ╦Īż“┼ņ═╬źóźļź▀ź╦ź”źÓż¼│½╚»żĘż┐ĪŻGe┴žż╬Ė³żĄż“śOĮyż╦╩čż©żķżņżļż└ż▒żŪżŽż╩ż»Īóź╣ź╚źżźŁź¬źßź╚źĻĪ╩▓Į│ž┴╚└«Ī╦żŌöUĖµżŪżŁżļĪŻ║Żż╬ż╚ż│żĒ╣Ō▓┴ż╩GaAsÅU╚ŠŲ│öüĖ■ż▒ż╬┤łż╚żĘżŲż╬╠Oż“─¾░ŲżĘżŲżżżļĪŻŖW▓┴ż╩ģ╬═█┼┼├ėżõSiźšź®ź╚ź╦ź»ź╣Īóź╣źįź¾ź╚źĒź╦ź»ź╣ż╩ż╔ż╬┤ł║Ó╬┴żžż╬▒■├ōż“┴└ż├żŲżżżļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2023年8月16日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

źšźķź├źĘźÕźßźŌźĻż╬╣±║▌▓±Ą─żŪżóżļFlash Memory Summit 2023ż╦ż¬żżżŲĪóMost Innovative Flash Memory startupŗ╠ńżŪ║Ū═źĮ©Š▐ż“▒č╣±ż╬ź╣ź┐Ī╝ź╚źóź├źūQuinas Technologyż¼£pŠ▐żĘż┐Ī╩┐▐1Ī╦ĪŻż│ż╬┐ĘĘ┐źßźŌźĻżŽ╬╠╗ę╬ü│ž┼¬ż╩░µĖ═Ę┐ź▌źŲź¾źĘźŃźļż╬Č”╠─ź╚ź¾ź═źļĖĮō■ż“ŠW├ōżĘżŲ┼┼▓┘ż“ĮążĘŲ■żņż╣żļöĄ╝░ż╬źŪźąźżź╣ĪŻQuinasżŽ▒čźķź¾ź½ź╣ź┐Ī╝Įj│žż╬╚»£½ż“Ą£Č╚▓Įż╣żļ┤ļČ╚ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2023年7月 4日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

TSMCżŽśOŲ░┘ZĖ■ż▒ż╬╚ŠŲ│öüź┴ź├źūż╦┤žżĘżŲżŌADASĪ╩└Ķ┐╩ź╔źķźżźąĪ╝ܦ▐qźĘź╣źŲźÓĪ╦żõśOŲ░▒┐┼ŠĖ■ż▒ż╩ż╔ż╬▒ķōQ╝ńöüż╬SoCźūźĒź╗ź├źĄĖ■ż▒ż╦ĪóżĮżĘżŲ║Ū└Ķ├╝ż╬3nmźūźĒź╗ź╣ź╬Ī╝ź╔ż╬Č\ĮčĪųN3AEĪūż“śOŲ░┘Zż¬żĶżėHPCĪ╩High Performance ComputingĪ╦Ė■ż▒ż╦Īó2024ŃQż╦─¾ČĪż╣żļĪŻżĄżķż╦╣Ō╝■āS╠Ą└■Č\ĮčżŪżŌ6nmź╬Ī╝ź╔ż“Ų│Ų■ż╣żļĪŻŲ▒╝ęźėźĖź═ź╣│½╚»├┤┼÷źĘź╦źóVPż╬Kevin ZhangĢ■Ī╩┐▐1Ī╦ż¼Ėņż├ż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2023年4月25日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

āS─╣13.5nmż╬EUVĪ╩Extreme Ultra VioletĪ╦źĻźĮź░źķźšźŻżŪżŌź└źųźļźčź┐Ī╝ź╦ź¾ź░ż¼Ų│Ų■żĄżņ╗Žżßż┐ĪŻż┐ż└żĘĪó▓“ćĄ┼┘ż¼30nmż▐żŪżĘż½įużķżņż╩żżż┐żßĪó░╠Åø╣ńż’ż╗ż¼žMżĘżżĪŻApplied MaterialsżŽĪó║ŪŠ«ż╬źčź┐Ī╝ź¾╔²ż“ŖW─Ļż╦Ę┴└«ż╣żļźčź┐Ī╝ź¾źĘź¦źżźįź¾ź░Č\Įčż“Ų│Ų■ż╣żļäóÅøĪųCentura SculptaĪūż“│½╚»żĘż┐ĪŻż│żņż“╗╚ż©żąź└źųźļźčź┐Ī╝ź╦ź¾ź░ż╚Ų▒┼∙ż╩Øó╦Īż“ŖW─Ļż╦Ę┴└«żŪżŁżļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2023年3月24日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

źūźĒź╗ź╣ź╬Ī╝ź╔2nm░╩æTż╬╝Ī└ż┬Õ╚ŠŲ│öüź┴ź├źū×æļ]ż╦’Lż½ż╗ż╩żżĪó╝ŖōQĄĪźĻźĮź░źķźšźŻĪ╩Computational LithographyĪ╦ż╬ź©ź│źĘź╣źŲźÓż“TSMCż╚NvidiaĪóASMLĪóSynopsysż¼└▀╬®żĘż┐ĪŻ3nmź╬Ī╝ź╔ż╬╝┬ź┴ź├źūæųżŪż╬║ŪŠ«Øó╦Īż¼13nm±śż▐żŪżõż├żŲżŁżŲĪóāS─╣13.5nmż╬EUVźĻźĮżŪżŌOPCĪ╩Ė„ŖZ└▄Ė·▓╠▌ö┘ćĪ╦ż╬Ų│Ų■ż¼’Lż½ż╗ż╩ż»ż╩ż├żŲżŁż┐ĪŻ╝ŖōQĄĪźĻźĮżŽżĮż╬ż┐żßż╬Č\ĮčżŪżóżļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2023年3月22日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

źūźĻź¾ź╚┤łż└ż▒żŪżŽż╩ż»ĪóźŲźšźĒź¾ż╩ż╔ż╬┤łż╦żŌ╠®ŠÆ└Łż╬╬╔żżŪ█└■ż“Ę┴└«żŪżŁżļČ\Įčż“┤õŠ}Įj│žż¼│½╚»Īó╣Ō╝■āSØŖ└Łż╬═źżņż┐övŽ®ż“═Ų░ūż╦Ę┴└«żŪżŁżļżĶż”ż╦ż╩żļĪŻ┤õŠ}Įjż╬i-SBż╚Ō}żążņżļČ\Į迎Īó╩¼╗ę└▄╣ń║Óż“├ōżżżļ░█¹|║Ó╬┴└▄╣ńČ\ĮčżŪżóżļĪŻŠÅČ╚─cżŌż╣żŪż╦ŠÆų`żĘ╗ŽżßĪó╝┬├ō▓Įż╦Ė■ż▒ż┐ź©ź│źĘź╣źŲźÓż╬╣Į├█├µż└ĪŻż│ż╬Č\Įčż“╔ߥ┌żĄż╗żļż┐żßż╬źūźķź├ź╚źšź®Ī╝źÓż“║ŻĮ®ż╦żŽ╣Į├█ż╣żļ╝Ŗ▓ĶżŪ┐╩żßżŲżżżļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

![2nmż╬ź▐ź╣ź»×æ║Ņ┤³┤ųż“│╩├╩ż╚ø]Į╠ż╣żļNvidiaż╬cuLithoż╚Synopsysż╬OPC 2nmż╬ź▐ź╣ź»×æ║Ņ┤³┤ųż“│╩├╩ż╚ø]Į╠ż╣żļNvidiaż╬cuLithoż╚Synopsysż╬OPC](/assets_c/900px/240328-culitho.png)