FD-SOI CMOSżŽ20nm░╩æTżŪżŽźąźļź»żĶżĻżŌéā─śŃ~ŠWż╚SOIź│ź¾źĮĪ╝źĘźóźÓż¼╚»╔Į

┤░µ£Č§ĒśĘ┐Ī╩fully depletedĪ╦SOI CMOSČ\Į迎20nm░╩æTż╬CMOSČ\Įčż╚żĘżŲ└Łē”ĪóŠ├õJ┼┼╬üĪóź│ź╣ź╚ż╬┼└żŪźąźļź»CMOSż╚╚µż┘Ń~ŠWż╦ż╩żļż│ż╚ż“SOIźżź¾ź└ź╣ź╚źĻź│ź¾źĮĪ╝źĘźóźÓż¼╚»╔ĮżĘż┐ĪŻż│ż╬ż┐żßĘ╚┬ėĄĪ▀_ż╦╗╚ż”ż┘żŁSoCż╦żŽĖ■żżżŲżżżļż╚Ų▒ź│ź¾źĮĪ╝źĘźóźÓż╬æųĄķźŪźŻźņź»ź┐ż“ē»żßżļHoracio MendezĢ■żŽ╝ń─źż╣żļĪŻ

![┐▐1ĪĪ┤░µ£Č§ĒśĘ┐SOI(īÜ)ż╚źąźļź»Ę┐(║Ė)ż╬MOSź╚źķź¾źĖź╣ź┐╣Įļ]](/archive/editorial/technology/img/TFP110221-01a.jpg)

┐▐1ĪĪ┤░µ£Č§ĒśĘ┐SOI(īÜ)ż╚źąźļź»Ę┐(║Ė)ż╬MOSź╚źķź¾źĖź╣ź┐╣Įļ]

FD-SOIČ\Įč(┐▐Ż▒)żŽĪóźąźļź»CMOSż╚╚µż┘żļż╚ø]ź┴źŃź¾ź═źļĖ·▓╠ż¼ÅŚżŁż╦ż»żżĪŻżŌż┴żĒż¾ĪóMOSFETż╬Ų░║ŅĖČ═²ż½żķø]ź┴źŃź¾ź═źļĖ·▓╠ż¼ż╩żżŚlżŪżŽż╩żżż¼Īóź▓Ī╝ź╚─╣ż“ø]ż»żĘżŲżżż»ż╦ż─żņĪóź▓Ī╝ź╚żĘżŁżż┼┼░ĄVthż╬─Ń▓╝ż¼┤╦żõż½ż╦ż╩żļĪŻż│ż╬ż┐żßźąźļź»CMOSż╩żķVthż╬─Ń▓╝ż¼Šåż╩ź▓Ī╝ź╚─╣żŪżŌż▐ż└źšźķź├ź╚ż╩ėX▌åż“░▌Ęeż╣żļĪŻż│ż╬ØŖ└ŁżŽ╚∙║┘▓Įż╣żļæųżŪČ╦żßżŲŃ~ŠWżŪżóżļĪŻ┼┼░Ąż“▓╝ż▓żŲżŌŲ░║ŅżŪżŁżļż┐żßż└ĪŻ

ø]ź┴źŃź¾ź═źļĖ·▓╠ż¼ÅŚżŁżŲżżż╩żżź▓Ī╝ź╚─╣żŽĪóźūźĒź╗ź╣źąźķż─żŁż¼Š»ż╩żżż│ż╚ż“┴T╠Żż╣żļĪŻź▓Ī╝ź╚─╣ż¼źąźķż─żżżŲżŌVthżŽżĄż█ż╔╩č▓ĮżĘż╩żżż┐żßż└ĪŻż│ż╬±T▓╠ĪóSRAMź╗źļż╬Ų░║Ņż¼ŖW─Ļż╦ż╩żļĪŻSRAMżŽźūźĒź╗ź├źĄż╬źņźĖź╣ź┐żõFIFOĪ󟣟џ├źĘźÕż╩ż╔żĄż▐żČż▐ż╩ĮĻż╦╗╚ż’żņżļ─_═ūż╩övŽ®żŪżóżļĪŻż│żņż¼ŖW─Ļż╦żóżņżąźūźĒź╗ź╣źąźķż─żŁż╬Š»ż╩żżźūźĒź╗ź├źĄż“║Ņżļż│ż╚ż¼żŪżŁżļĪŻARMż╬źūźĒź╗ź├źĄż“ź│źóż╚ż╣żļSoCż╩ż╔ż╦Ė■ż»Ślż└ĪŻ

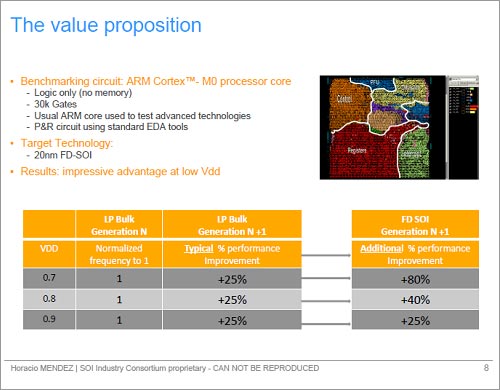

żĮż│żŪĪóĖĮ╝┬┼¬ż╩ARMż╬─ŃŠ├õJ┼┼╬üźūźĒź╗ź├źĄź│źóż╬▐kż─Cortex-M0Ī╩ź▓Ī╝ź╚┤╣ōQżŪ3╦³ź▓Ī╝ź╚Ī╦ż“╗╚żżĪóźĘźĻź│ź¾ź┘Ī╝ź╣ż╬źĘź▀źÕźņĪ╝źĘźńź¾ż“źąźļź»CMOSż╚FD-SOIż╬CMOSż╦┼¼├ōżĘĪó╚µ│ėżĘż┐ĪŻżĮż╬±T▓╠Īóżóżļ└ż┬Õż╬Ų░║Ņ╝■āS┐¶ż“1ż╚ż╣żļż╚Īóźąźļź»CMOSżŪżŽ0.9Vż½żķ0.7Vż╦ż½ż▒żŲ25%Ė■æųżĘż┐ĪŻż│żņż╦×┤żĘżŲĪóFD-SOI CMOSżŽ0.9VżŪżŽŲ▒żĖ25%▓■║¤ż└ż¼Īó0.8VżŪ40%▓■║¤żĘĪó0.7Vż└ż╚80%żŌŲ░║Ņ╝■āS┐¶ż¼æųż¼ż├ż┐Ī╩┐▐2Ī╦ĪŻ

┐▐2ĪĪFD-SOI CMOSżŽ┼┼░Ąż“▓╝ż▓żķżņżļ┼└żŪéā─śŃ~ŠWż╦ż╩żļ

MendezĢ■żŽĪóSRAMż╩ż╔ż╬źßźŌźĻĪ╝ż╦żŽ║Ū┼¼ż└ż╚ż╣żļĪŻSRAMż“ŖW─Ļż╦Ų░ż½ż╣ż┐żßż╦żŽVthż╬┬Ęż├ż┐źšźĻź├źūźšźĒź├źūż¼ØŁ═ūż└ĪŻŲ▒Ģ■ż╦żĶżļż╚źąźļź»CMOSż╩żķ0.8~0.9VŲ░║Ņż¼ĖĮ╝┬┼¬ż└ż¼ĪóFD-SOIż╩żķ0.65VżŪżŌĖĮ╝┬┼¬ż└ż╚żĘżŲżżżļĪŻ┼┼░Ąż¼▓╝ż¼żļ╩¼Īó└Łē”żĶżĻżŌŠ├õJ┼┼╬üż¼ĮjżŁż»▓╝ż¼żļż┐żßĘ╚┬ėĄĪ▀_ż╦Ė■ż»ĪŻ╩Ż┐¶ż╬┤ļČ╚żõĮj│žż╬Ė”ē|żŪżŽ150mV(0.15V)ż╚żżż”─Ńżż┼┼░ĄżŪżŌFD-SOIź╚źķź¾źĖź╣ź┐żŽŲ░║ŅżĘż┐ż│ż╚ż“│╬Ū¦żĘżŲżżżļĪŻ

żĄżķż╦źūźĒź╗ź╣ź│ź╣ź╚żŌŖWż»ż╩żļż╚żżż”ĪŻż│żņżŽźąźļź»źĘźĻź│ź¾ż╚╚µż┘źūźĒź╗ź╣ż¼į~├▒ż╦ż╩żļż½żķż└ż╚żżż”ĪŻMendezĢ■żŽĪóźĻĪ╝ź»┼┼╬«żõźĄźųź╣źņź├źĘźńźļź╔┼┼╬«ż“═▐ż©żļż┐żßĪóźąźļź»CMOSżŪżŽVth├ōż╬ź┴źŃź¾ź═źļź╔Ī╝źįź¾ź░ż╦▓├ż©Īó┐╝żżź╔Ī╝źįź¾ź░ż╚Īóź╔źņźżź¾Ī”źĮĪ╝ź╣└▄╣ńŖZšfż╬źŽźĒĪ╝ź╔Ī╝źįź¾ź░Ī╩Halo dopingĪ╦ż“╣įż”ĪŻż│ż”żżż├ż┐źūźĒź╗ź╣ź╣źŲź├źūż¼FD-SOIżŪżŽ═ūżķż╩żżĪŻ

żĄżķż╦źąźļź»CMOSżŪżŽ╚∙║┘ż╦ż╩żļż╚FINFETż╩ż╔3╝ĪĖĄ╣Įļ]ż╬ź╚źķź¾źĖź╣ź┐ż¼╣═░ŲżĄżņżŲżżżļż¼Īó╣Įļ]ż¼╩Ż╗©ż╦ż╩żĻĪóź│ź╣ź╚żŽ╗\ĮjżĘźĻź╣ź»ż¼ĮjżŁżżĪŻż│żņż╦×┤żĘżŲFD-SOIż└ż╚Īó╚∙║┘▓Įż╚Č”ż╦BOXĪ╩ļmżß╣■ż▀¤©▓Į╦ņĪ╦żŌ50nmµć┼┘ż╚Ū÷ż»ż╩żļż┐żßĪó┤łźąźżźóź╣ż“ż½ż▒żļż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩żļĪóż╚żżż”ź▄Ī╝ź╩ź╣┼¬ż╩źßźĻź├ź╚żŌ╝{▓├żĄżņżļĪŻ

╝Īż╬├╩│¼żŪżŽFD-SOI CMOSż“╗╚ż”ż┐żßż╦ĖĮ║▀ĪóĘ╚┬ėĄĪ▀_źßĪ╝ź½Ī╝ż╚ÅBż“żĘżŲż¬żĻĪ󿥿ķż╦┐¶ź§ĘŅĖÕż╦żŽ20nm░╩æTż╬µ£żŲż╬źąźļź»CMOSż“FD-SOIż╦┤╣ż©żĶż”ż╚Ų▒Ģ■żŽ╣═ż©żŲżżżļĪŻø]ź┴źŃź¾ź═źļĖ·▓╠ż¼Š»ż╩ż»Vthż╬źąźķż─żŁż¼Š»ż╩żżż╚żżż”ż│ż╚żŽĪóź│ź¾źčźņĪ╝ź┐żõ║╣Ų░Ų■╬üż¼šl╔┘ż╩źóź╩źĒź░övŽ®ż╦żŌŃ~ŠWżŪżóżļĪŻ

FD-SOIż“┐╩żßżļSOIź│ź¾źĮĪ╝źĘźóźÓźßź¾źąĪ╝ż╦żŽĪóARMĪóź░źĒĪ╝źąźļźšźĪź”ź¾ź╔źĻĪ╝ź║ĪóIBMĪóSTź▐źżź»źĒź©źņź»ź╚źĒź╦ź»ź╣ĪóSoitecĪóCEA-Letiż¼żżżļĪŻżĄżķż╦ĪóSOIź│ź¾źĮĪ╝źĘźóźÓż╚żĘżŲżŽĪóźūźĒź╗ź╣źšźĪź”ź¾ź╔źĻżõIPźūźĒźąźżź└ż╦żŌŌ}żėż½ż▒Īó╚∙║┘ż╩ź╚źķź¾źĖź╣ź┐ż╬ź©ź│źĘź╣źŲźÓż“╣Į├█żĘż┐żżż╚╣═ż©żŲżżżļĪŻ