TSMCĄČ20nmĄ╬ąÎąÝą╗ą╣Ą˛═ŔŃQőî3╗═╚ż┤ŘĄ╦ąŕąŕí╝ą╣íó14nmĄ╦ĄÔ│ź╚»żĺż}

║ă└Ŕ├╝Ą╬IC│ź╚»ĄăĄ¤28nmĄ╬╬╠żĆĄČ╗¤ĄŮĄ├Ą┐ĄČíó┴ߥ»ĄÔ20nmąÎąÝą╗ą╣Ą˛2012ŃQĄ╬őî3╗═╚ż┤ŘĄ╦ąŕąŕí╝ą╣Ą╣ĄŰíóĄ╚˝ś¤ĐTSMC╝ĎĄ╬CTOĄăĄóĄŰJack SunĽ■(┐Ů1)Ą¤ŞýĄ├Ą┐íúSunĽ■Ą¤╝íĄ╬14nm░╩ĹTĄ╦Ą─ĄĄĄĂĄÔĄŻĄ╬Şź─╠ĄĚĄ˛ŞýĄŕíóĄ│Ą│ĄźĄÚĄ¤ąŕąŻą░ąÚąŇąúĄÔąăąđąĄą╣╣ŻŰ]ĄÔŻjĄşĄ»╩ĐĄ´ĄŰĄ│Ą╚Ą˛┐â║ÂĄĚĄĂĄĄĄŰíúĄĚĄźĄĚíóśO┐«Ą╦Ż╝Ą┴░ţĄýĄĂĄĄĄŰíúĄ╩Ą╝Ąźíú

┐Ů1ííTSMCĄ╬CTOĄăĄóĄŰJack SunĽ■

Ą│ĄýĄŮĄă130nmíó90nmíó65nmíó40/45nmíó28nmĄ╚ĄńĄ├ĄĂĄşĄĂíó│ź╚»Ą╬żĺż}ĄźĄÚ╬╠żĆĄ╬╬ęĄ┴ĹÍĄČĄŕĄŮĄăĄ╬┤Ř┤ÍĄČ╝┬Ą¤íóĄ╔ĄˇĄ╔ĄˇŤ]Ą»Ą╩Ą├ĄĂĄĄĄŰĄ│Ą╚ĄČĄŻĄ╬śO┐«Ą╬╬óĄ╦ĄóĄŰíú╩Ôé╬ĄŮĄŕĄ╦─ż└▄┤ěĚŞĄ╣ĄŰąĐą┐í╝ąˇĄ╬´L┤┘╠ę┼┘Ą¤íó130nmĄźĄÚ40nmĄ╚╚¨║┘Ą╦Ą╩ĄŰĄ╦Ą─Ąýíóß×═Ă├═░╩▓╝Ą╦Ą╩ĄŰ┤Ř┤ÍĄČŤ]Ą»Ą╩Ą├ĄĂĄĄĄŰíú╬ŃĄĘĄđíó90nmąÎąÝą╗ą╣ĄăĄ¤Ö┌żĆ╬╠ĄČąďí╝ą»╗■Ą╬50%Ą╦Ą╩ĄŰĄ╬Ą╦12╗═╚ż┤Ří╩3ŃQí╦ĄźĄźĄ├Ą┐ĄČíó28nmąÎąÝą╗ą╣Ą¤4╗═╚ż┤Ř(1ŃQ)ĄĚĄźĄźĄźĄ├ĄĂĄĄĄ╩ĄĄíúĄ┐Ą└ĄĚíóĄ│Ą╬┤Ř┤ÍĄ╬╬óčřĄ▒Ą╚Ą╩ĄŰÉ║öü┼¬Ą╩ąăí╝ą┐Ą¤╣Í▒ڥ㪟Ą╗Ą┐Ą└Ą▒Ą╦é╬ĄŮĄŕíó═ŻđMŻŞĄ╦ĄÔĚă║▄ĄĚĄĂĄĄĄ╩ĄĄíúSunĽ■Ą╦ĄŔĄŰĄ╚íó28nmĄ˛╬╠żĆĄĚĄĂĄźĄÚĄ╬ąĂí╝ąÎąóąŽą╚Ą╬┐˘Ą¤íó40nmąÎąÝą╗ą╣Ą╬╬╠żĆĄ˛╗¤ĄßĄĂĄźĄÚ╬ęĄ┴ĄóĄČĄŰĄŮĄăĄ╬┤Ř┤ÍĄČĂ▒ĄŞĄ╚ĄĚĄĂĄ█Ą▄2ă▄Ą╦ĄÔĄ╩ĄŰĄ╚Ą╣ĄŰíú28nmĄ╬╩Ôé╬ĄŮĄŕĄ¤íÍvery goodíÎĄ╚Ş└ĄĄíóśO┐«╦■í╣ĄăĄóĄŰíú

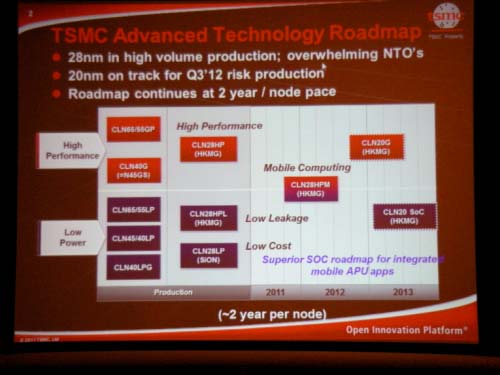

20nmĄ╦Ą─ĄĄĄĂĄ¤Ą╣ĄăĄ╦SRAMĄ╬╗ţ║ţĄ╚Ă░║ţ│╬㞥˛Ż¬ĄĘĄĂĄ¬ĄŕíóąßąÔąŕĄ└Ą▒ĄăĄ¤Ą╩Ą»ąÎąÝą╗ą├ąÁĄńąÝąŞą├ą»ICĄ╬ąýąŞą╣ą┐Ą╩Ą╔Ą╦ĄÔ╗╚ĄĘĄŰąýą┘ąŰĄ╦═ŔĄĂĄĄĄŰĄ│Ą╚Ą˛╝┬ż┌ĄĚĄ┐íú▒ĐARM╝ĎĄ╚─ˇĚ╚ĄĚĄĂĄĄĄŰTSMCĄ¤íóARMĄ╬Cortex-A9ąăąňąóąŰą│ąóĄ˛ąĂí╝ąÎąóąŽą╚ĄĚĄĂĄ¬Ąŕíó10ĚţĄ╦ĄÔ20nmąÎąÝą╗ą╣Ąă║ţĄŰCortex-A15MPCoreĄ˛ąĂí╝ąÎąóąŽą╚ĄĚĄ┐Ą│Ą╚Ą˛╚»╔ŻĄĚĄĂĄĄĄŰí╩╗▓╣═ź@╬┴1í╦íú20nmĄ╬ąÎąÝą╗ą╣×Ĺë䥤└şëŽĄ˛─_ťćĄ╣ĄŰCLN20Gí╩HKMGí╦Ą˛ĄŮĄ║─ˇÂíĄĚíó╝íĄ╦─Ńż├ńJ┼┼╬üĄ╬CLN20 SoCí╩HKMGí╦Ą˛2013ŃQĄźĄÚ─ˇÂíĄ╣ĄŰ(┐Ů2)íú20GĄ¤║ă┐Ě28nmąÎąÝą╗ą╣Ą╬28HPíó20SoCĄ¤28HPMĄ╚ĄŻĄýĄżĄý╚ŠĄ┘ĄĂíó└şëŽĄ¤2.1ă▄Ą╦ą╣ąĄą├ą┴ąˇą░┼┼╬üĄ¤0.75ă▄░╩▓╝Ą╦Ą╩ĄŰĄ╚Şź└ĐĄÔĄ├ĄĂĄ¬Ąŕíóą┴ą├ąÎĄ¤35í┴40%ż«ĄÁĄ»íóĆ]┼┘Ą¤20%░╩ĹÍĆ]Ą»íóż├ńJ┼┼╬üĄ¤30%░╩▓╝Ą╦ż«ĄÁĄ»Ą╩ĄŰĄ╚ĄĚĄĂĄĄĄŰíú

┐Ů2íí2012Şň╚żĄźĄÚ20nmąÎąÝą╗ą╣Ą˛ąŕąŕí╝ą╣Ą╣ĄŰ

20nmąÎąÝą╗ą╣ĄăĄ¤íóą▓í╝ą╚ąÚą╣ą╚╣ŻŰ]Ą˛╗╚ĄĄíóą▓í╝ą╚└ń▒´╦ýĄ˛╠ęĄ╦ĄĚĄ╩ĄČĄÚă÷Ą»Ą╣ĄŰĄ│Ą╚Ąă╚¨║┘▓ŻĄ╦ĄÔ×┤▒■ĄĚíóă█└■ő╩ČĄ¤─Ń°BŃ^Ą╬Cuă█└■Ą˛╗╚ĄŽĄ╩Ą╔Ą╬╣ę╔ÎĄ˛╗▄ĄĚĄĂĄĄĄŰíúSiĄ╬¤─Ą▀Ą╦×┤ĄĚĄĂĄÔGeĄ╬ă█╩Č╬╠Ą˛╩ĐĄĘíóSiNĄ╬ő╩ČĄ╦ĄÔ╣ę╔ÎĄ˛Â┼ĄÚĄĚíóĄ│ĄýĄŮĄăĄ╬ąÎąÝą╗ą╣Ą˛┐╩▓ŻĄÁĄ╗ĄŰĄ╚ĄĄĄ├Ą┐╚¨öéĄ╩╣ę╔ÎĄ╦ĄŔĄ├ĄĂ╝┬ŞŻĄĚĄĂĄĄĄŰíú

20nmĄ╬ąŕąŻą░ąÚąŇąúĄăĄ¤íóNA=1.35Ą╬ArFÚ]┐╗ąŕąŻą░ąÚąŇąúĄ╬ą└ąÍąŰąĐą┐í╝ą╦ąˇą░Ą˛╦▄╠┐Ą╚ĄĚĄĂ╗╚ĄĄíóąŮąŰą┴ąËí╝ąÓĄ˛╗╚ĄŽ┼┼╗ĎąËí╝ąÓąŕąŻą░ąÚąŇąúĄ╚íóEUVí╩NA=0.25í╦ĄÔĂ│Ă■ĄĚĄĂĄĄĄŰíúą└ąÍąŰąĐą┐í╝ą╦ąˇą░ĄăĄ¤Ă╚śOĄ╬└▀╝ŐąŰí╝ąŰĄ˛║ţĄŕĹÍĄ▓íóąźą╣ą┐ąŮĄČ¤¬Ş¸Ą˛2övĄ╦╩ČĄ▒ĄŰĄ┐ĄßĄ╬ąŮą╣ą»Ą˛║ţĄŰŁş═ÎĄ¤Ą╩ĄĄíúĄ╣Ą┘ĄĂTSMCĄČąŮą╣ą»Ą˛ĂˇĄ─Ą╦╩ČĄ▒ĄŰíú

┼┼╗ĎąËí╝ąÓ¤¬Ş¸ĄăĄ¤ąŮąŰą┴ąËí╝ąÓĄ╬ąËí╝ąÓ╦▄┐˘Ą˛1╦Ř3000╦▄Ą╦╗\ĄńĄĚąŽąží╝ą¤ŻŔ═řŻŚ┐˘Ą╚ĄĚĄĂ10 wphí╩wafers per hourí╦Ą˛╝Ő▓ŔĄĚĄĂĄĄĄŰĄČíóŞŻ╝┬Ą╬ą╣ąŰí╝ąÎą├ą╚Ą¤ĄŮĄ└1wphĄ╦ĄÔ╦■Ą┐Ą╩ĄĄíúŮköÁíóEUV¤¬Ş¸ÁíĄ╚ĄĚĄĂą¬ąÚąˇą└ASML╝ĎĄ╬NXE3100Ą˛└▀ĆŤĄĚ27nmąĐą┐í╝ąˇĄ˛NA=0.25Ą╬╚┐╝o޸│ěĆUĄă4.5 wph░╩▓╝Ą╚ĄĄĄŽ˝T▓╠Ą˛ďuĄĂĄĄĄŰíú

ÂŽĄ╦╔ďŁ▓╩ČĄ╩ĄČĄÚĄÔ14nmĄăĄ¤Ą╔Ą┴ĄÚĄźĄ╬┬ô┘IĄĚĄźĄ╩ĄĄĄ╚ĄĚĄĂĄĄĄŰíúąŮąŰą┴ąËí╝ąÓĄ╬EBĄăĄ¤ą»ąÚą╣ą┐╣Ż└«Ąă100 wph░╩ĹÍíóEUVĄăĄÔNA0.33Ą╬޸│ěĆUĄă100 wph░╩ĹÍĄ╬ą╣ąŰí╝ąÎą├ą╚Ą˛Í`╗ěĄĚĄĂĄĄĄŰíú

ĄŻĄ╬╝íĄ╬14nmĄ╦Ą─ĄĄĄĂĄÔŞŽë|│ź╚»Ą˛╗¤ĄßĄĂĄ¬ĄŕíóMUGFETíóFINFETĄ╩Ą╔Ą╬ąăąđąĄą╣╣ŻŰ]ĄńGeĄ˛Ą¤ĄŞĄßĄ╚Ą╣ĄŰ╣ÔöíĂ░┼┘║Ó╬┴Ą˛╔ŻáC┼┼╗Ď┴÷╣ď┴ěĄ╦╗╚ĄŽąăąđąĄą╣ĄČŞíĂĄĄ╦Ă■Ą├ĄĂĄĄĄŰíúĄŻĄ╬╝┬┘xĄ╚ĄĚĄĂ22nmĄ╬ąýąĄąóąŽą╚Ąă║ţĄ├Ą┐FINFETĄ˛íó║˛ŃQĄ╬IEDMĄă╚»╔ŻĄĚĄĂĄĄĄŰĄČíóąÁąÍą╣ąýą├ąĚąšąŰą╔┼┼╬«Ą╬´łĄşĄČ70mV/decadeĄ╚ąÎąýí╝ą╩╣ŻŰ]ĄăĄ¤ďuĄÚĄýĄ╩ĄĄ├═Ą˛ďuĄĂĄĄĄŰíúĄ│Ą╬├═Ą╦ĄŔĄŕíó┼┼░ÁĄ˛▓╝Ą▓ĄĂĄÔĂ░║ţĄăĄşĄŰĄ│Ą╚Ą˛┐âĄĚíóÁŇĄ╦FINFETĄăĄ¤Ą╩Ą»˛ť═ŔĄ╬ąÎąýí╝ą╩FETĄăĄ¤ĄÔĄ¤ĄńąÁąÍą╣ąýą├ąĚąšąŰą╔┼┼╬«Ą╬´łĄşĄ˛▓╝Ą▓ĄÚĄýĄ╩ĄĄĄ┐Ąßíóą╚ąÚąˇąŞą╣ą┐Ą¤╗╚ĄĘĄ╩ĄĄĄ╚ĄĚĄĂĄĄĄŰíúĄ┴Ą╩Ą▀Ą╦14nmĄăFINFET╣ŻŰ]Ą└Ą╚0.75í┴0.7VĂ░║ţĄ╦Ą╩ĄŕĄŻĄŽĄ└Ą╚SunĽ■Ą¤═Ż▒RĄ╣ĄŰíú14nmĄăĄ¤SOIĄ¤ĄÔĄ¤Ąń┬ô┘I╗ŔĄ╦Ă■ĄÚĄ╩ĄĄíúSOIĄ¤┴ŕ╩ĐĄ´ĄÚĄ║ą╦ą├ą┴ŢxżýĄ╦╗╚Ą´ĄýĄŰĄ└ĄÝĄŽĄČíóąßąŞąŃí╝Ą╦Ą¤Ą╩ĄŕĄĘĄ╩ĄĄĄ╚Ă▒Ľ■Ą¤ŞźĄĂĄĄĄŰíú

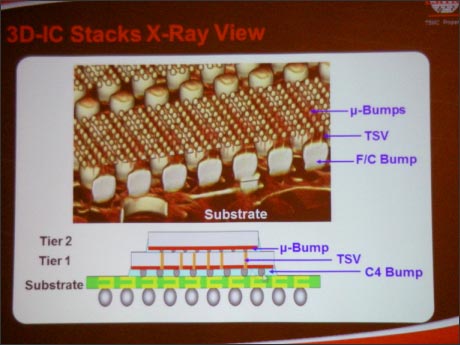

╚¨║┘▓ŻĄ╚Ą¤╩╠Ą╦╣ÔŻŞ└ĐĄ˛├ú└«Ą╣ĄŰÂ\ŻĐĄ╚ĄĚĄĂ3╝íŞÁICĄČĄóĄŰíúTSMCĄ¤ąÁąÍąĚą╣ąĂąÓąĄąˇąĂą░ąýí╝ąĚąšąˇĄ╚ĄĚĄĂíóąÎąŕąˇą╚ă█└■┤łĹÍĄ╦DRAM8Ş─Ą╚GPU1Ş─Ą╬ąÁąÍąĚą╣ąĂąÓĄ˛1ąĐą├ą▒í╝ąŞĄ╦╝řĄßĄŰSiąĄąˇą┐í╝ąŢí╝ąÂÂ\ŻĐĄ˛─ˇ░ĂĄĚĄĂĄĄĄŰíúSiĄ╬ąĄąˇą┐í╝ąŢí╝ąÂĄ╦Ą¤ˇH┴ěă█└■Ą˛╣Ż└«ĄĚĄĂĄ¬ĄşíóGPUĄ╚DRAMĄ˛ĄŻĄ╬ĹÍĄ╦ąŇąží╝ą╣ą└ąŽąˇĄăąŮąĄą»ąÝąđąˇąÎĄ˛─╠ĄŞ└▄˘öĄ╣ĄŰí╩┐Ů3í╦íúŞ▄ÁĎç@Ą¤ŞýĄÚĄ╩ĄĄĄČíóą╗ą▀ą│ąˇąŢí╝ą┐ąŰĄăżĎ▓ĄĚĄ┐ąÂąĄąŕąˇą»ą╣Ą╬Vertex-7 FPGA4Ş─Ą˛ąĄąˇą┐í╝ąŢí╝ąÂĹÍĄ╦ŻŞ└ĐĄĚĄ┐Â\ŻĐĄ╚ô˘ĄĂĄĄĄŰí╩╗▓╣═ź@╬┴2í╦íú

┐Ů3ííSiąĄąˇą┐í╝ąŢí╝ąÂĹÍĄ╦TSVĄăą┴ą├ąÎĄ╚└▄˘ö

450mmĄ╦┤ěĄĚĄĂĄ¤íóĄÔĄ├Ą╚ą░ąŕí╝ąˇĄ╩╣ężýĄ˛║ţĄŰĄ│Ą╚Ą˛Í`╗ěĄ╣íú2013í┴2014ŃQĄ╦Ą¤┐ĚâšŢxĄ╦ĄóĄŰFab12Ą╦ąĐąĄąÝą├ą╚ąÚąĄąˇĄ˛║ţĄŕíóÖ┌żĆĄ¤˝ś├ŠĄ╦ĄóĄŰFab15Ąă2015í┴2016ŃQ║óĄ╦╗¤ĄßĄŰ═Ż─ŕĄ└Ą╚ĄĚĄĂĄĄĄŰíú

╗▓╣═ź@╬┴

1. ARM and TSMC Tape Put First 20nm ARM Cortex-A15 Multicore Processor

2. 28nmĄ╬FPGAĄ¤ąĄąˇą┐í╝ąŢí╝ąÂżW├ôĄăTbps╝┬ŞŻíóąŮąŰą┴ą│ąóĂÔë┼ĄăŻŔ═říŽ▓˛└¤├ôĄ╦ (2011/10/26)