źżź¾ź┘ź¾źĄź╣Īó┐ĘÖ┌źŲź╗źķż╬╚ŠŲ│öüźčź├ź▒Ī╝źĖ┤ļČ╚ż╚żĘżŲ│ū┐ĘČ\ĮčżŪ║Ų╔nŲ»

2012ŃQżŽżĖżßż╦Ų³╦▄ź¬źšźŻź╣ż“╩─żĖż┐źŲź╗źķĪ╩TesseraĪ╦╝ęĪŻ║ŻżŽĘeż┴│¶▓±╝ęż╚żĘżŲż╬┘T║▀żŪĪóĄ£Č╚▓±╝ęż╚żĘżŲ╚ŠŲ│öüźčź├ź▒Ī╝źĖź¾ź░Č\Įč▓±╝ęż╬Invensasż╚Īóź½źßźķźŌźĖźÕĪ╝źļ▓±╝ęż╬Digital Opticsż“╗▒▓╝ż╦Ęeż─┐ĘÖ┌źŲź╗źķż╚żĘżŲÖ┌ż▐żņ╩čż’ż├ż┐ĪŻźżź¾ź┘ź¾źĄź╣Ī╩InvensasĪ╦żŽ┐ĘĘ┐źčź├ź▒Ī╝źĖż╬źĮźĻźÕĪ╝źĘźńź¾ż“─¾ČĪż╣żļĖ”ē|│½╚»▓±╝ęż╚żĘżŲ║Ų╔nŲ»żĘ╗Žżßż┐ĪŻ

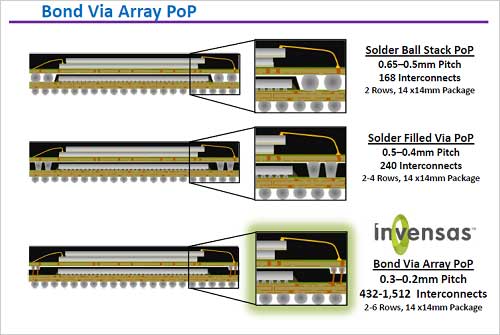

┐▐1ĪĪ╬®żŲż┐ź▄ź¾źŪźŻź¾ź░ź’źżźõż“PoPż╬└▄¶öż╦ŠW├ōĪĪĮąųZĪ¦Invensas

║Ų╔nŲ»ż╬┴└żżżŽĪóĪųźŲź╗źķż╬źżźßĪ╝źĖż“╩čż©ż┐żżĪūĪóĪųŲ³╦▄▌xŠņżŪż╬źżź¾ź┘ź¾źĄź╣ż╬Ū¦ē¶┼┘ż“╣Ōżßż┐żżĪūĪ╩źżź¾ź┘ź¾źĄź╣╝ęż╬║┤ŲŻ╣Ł═█Ģ■Ī╦ż│ż╚ż╦żóżļĪŻä▌╣±ż╦╦▄╝꥓┼└ż“Ęeż┴Īó╝ęµ^┐¶żŽĖĮ║▀50ć@äėĪŻż│ż╬ŲŌĪó1/3ż¼Ph.D(═²│žĖF╗╬ęÄ)ż“Ęeż─ĪŻźżź¾ź┘ź¾źĄź╣żŽĪó─_═ūż╩źčź├ź▒Ī╝źĖź¾ź░Č\Įčż╚żĘżŲĪó║Ó╬┴żõźßźŌźĻźŌźĖźÕĪ╝źļĪó3DźóĪ╝źŁźŲź»ź┴źŃż╦▓├ż©Īó└▀╝ŖżŌ╣įż”ĪŻ└▀╝Ŗż“äė▓Įż╣żļż┐żßĪóźßźŌźĻIPż“Mosys╝ęż½żķāAżżĪóTSVźšźĪź”ź¾ź╔źĻż╬Allvia╝ęż╬IPżŌĻPŲ■żĘż┐ĪŻż│ż╬ż│ż╚żŪźĘź▀źÕźņĪ╝źĘźńź¾ē”╬üż¼╣Ōż▐żĻĪ󟔟¦Ī╝źŽ╣®µćżŌ╗╚ż©żļżĶż”ż╦ż╩ż├ż┐ĪŻ

╝Ī└ż┬Õźčź├ź▒Ī╝źĖź¾ź░Č\Įčż╚żżż©żąż╣ż░ż╦TSVĪ╩through silicon viaĪ╦ż“╗╚ż”3D ICźčź├ź▒Ī╝źĖż“╗ūżż╔Ōż½ż┘żļż└żĒż”ż¼Īó3D ICż“║Żż╣ż░źėźĖź═ź╣ż╦ż─ż╩ż▓żļż│ż╚żŽžMżĘżżĪŻźšźĪźżź¾źįź├ź┴ż╬źčź├ź▒Ī╝źĖż“─Ńź│ź╣ź╚żŪż▐ż└║Ņżņż╩żżż½żķż└ĪŻ

żĮż│żŪĪóźżź¾ź┘ź¾źĄź╣żŽ║Żż╣ż░╗╚ż©żļŲ¾ż─ż╬┐ʿʿżČ\Įčż“│½╚»żĘż┐ĪŻ▐kż─żŽĪóźčź├ź▒Ī╝źĖźĄźżź║14mmĪ▀14mmż╬║YØŹźčź├ź▒Ī╝źĖż╦PoPĪ╩package on packageĪ╦ż╦żĶż├żŲ0.20mmźįź├ź┴żŪ6ź│źķźÓż└ż╚Īó║ŪĮj1440źįź¾ż“╝┬ĖĮżŪżŁżļ¾Hźįź¾▓ĮČ\ĮčżŪżóżļ(┐▐1)ĪŻ╣Łżżźąź¾ź╔╔²ż“╗╚ż”├ō²ŗż╦Ė■ż»ĪŻ╬Ńż©żąź╣źčź│ź¾ż╬żĶż”ż╩╣Ō└Łē”ź│ź¾źįźÕĪ╝ź┐żõźėźŪź¬┼┴┴„ĄĪ▀_ż╩ż╔ĪóźūźĒź╗ź├źĄż╚źßźŌźĻ┤ųż╬żõżĻŲDżĻż“╣ŌÅ]żŪ╣įż”źĘź╣źŲźÓż╬├ō²ŗżŪżóżļĪŻ12.8Gbps░╩æųż╬╣ŌÅ]┼┴┴„ż╦╗╚ż©żļż╚Ė½żŲż¬żĻĪóTSVż▐żŪż╬ż─ż╩ż«Č\Įčż╚żĘżŲżŌ└Łē”┼¬ż╦żŽČ╦żßżŲ╣ŌżżĪŻżŌż”▐kż─żŽĪóDRAMźŌźĖźÕĪ╝źļż“─Ńź│ź╣ź╚żŪżĘż½żŌŠ«żĄż╩ĀC└čżŪź”źļź╚źķźųź├ź»ż╩ż╔ź▐źČĪ╝ź▄Ī╝ź╔ż╦─Š¤²ż▒żĘż╩ż▒żņżąż╩żķż╩żż├ō²ŗĖ■ż▒ż╬Č\ĮčżŪżóżļĪŻ

║ŪĮķż╬¾Hźįź¾▓ĮČ\Į迎BVAĪ╩bond via arrayĪ╦ż╚Ō}żążņżŲż¬żĻĪó▐kż─ż╬źčź├ź▒Ī╝źĖż╚żŌż”▐kż─ż╬źčź├ź▒Ī╝źĖż“Ė■ż½żż╣ńż’ż╗ż╦└▄ŠÆżĄż╗żļPoPČ\Įčż╦Ė■ż»ĪŻ“£═Ķż╬PoPČ\Įčż└ż╚╚Š┼─ź▄Ī╝źļŲ▒╗╬ż“└▄╣ńż╣żļż╚ź▄Ī╝źļż¼ż─żųżņżŲµu└▄├╝╗ęż¼ż»ż├ż─żŁżĮż”ż╦ż╩żļż┐żßĪóźįź├ź┴ż╬╔²ż“Ø▓╩¼╣Łż»ż╚ż├żŲż¬ż»ØŁ═ūż¼żóżļĪŻ14mmĪ▀14mmźčź├ź▒Ī╝źĖż└ż╚0.65Ī┴0.50mmźįź├ź┴ż¼║ŪŠ«żŪżóż├ż┐ĪŻż│ż╬ż┐żßźįź¾┐¶ż“╗\żõżĘż┐ż»żŲżŌ║ŪĮj168źįź¾żĘż½╝┬ĖĮżŪżŁż╩żżĪŻ║ŪŖZżŪżŽĪóźóźÓź│źóĪ╩AmkorĪ╦╝ęż╬Ęeż─TMVĪ╩through mold viaĪ╦ż╚Ō}żążņżļĪóźŌĪ╝źļź╔ż╦ĘĻ │½ż▒żĘżŲ╚Š┼─ż“└▄¶öż╣żļČ\Įčż¼┼ąŠņżĘĪóżĶżĻ╚∙║┘ż╩źįź├ź┴ż“╝┬ĖĮżĘżĶż”ż╚żĘżŲżŁż┐ĪŻźóźÓź│źóżŽż│ż╬Č\Įčż“┐ĘĖ„┼┼Ąż╣®Č╚ż╦źķźżź╗ź¾ź╣ČĪ═┐żĘż┐ĪŻżĘż½żĘĪóż│ż╬Č\ĮčżŪżŌ0.5Ī┴0.4mmż»żķżżż╬źįź├ź┴ż▐żŪż¼Ė┬─cżŪĪó240źįź¾µć┼┘ż▐żŪż└ż╚źżź¾ź┘ź¾źĄź╣ż╬║┤ŲŻ╣Ł═█Ģ■żŽĖ½żļĪŻ

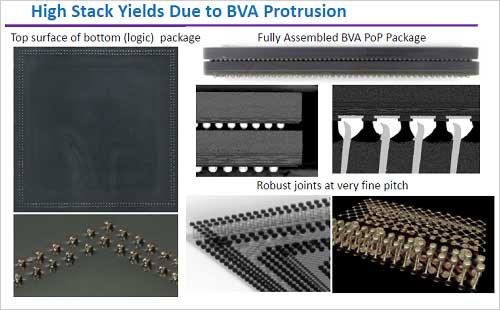

BVAżŽ0.3Ī┴0.2mmźįź├ź┴ż╚Č╣źįź├ź┴ż¼▓─ē”ż╩ż┐żßĪó1000źįź¾░╩æųż¼▓─ē”żŪżóżļż╚ż╣żļĪŻż│ż╬BVAČ\ĮčżŪżŽĪóź▄ź¾źŪźŻź¾ź░ź’źżźõż“╬®żŲżŲŪ█ÅøżĘĪóźŌĪ╝źļź╔Ī╩ź’źżźõ┤ųż╬źóź¾ź└Ī╝źšźŻźļż╬╠“│õĪ╦żŪź’źżźõż“╔w─ĻżĘż┐ĖÕĪó└▄¶ö├╝╗ęż╚żĘżŲ╗╚ż”ĪŻ─ŠĘ┬50”╠mµć┼┘ż╬Cuź’źżźõż“╗╚żżĪóż│ż╬æųż╦╚Š┼─ź▄Ī╝źļż╬├╝╗ęż“Ęeż─żŌż”▐kż─ż╬źčź├ź▒Ī╝źĖż“║▄ż╗żļĪŻ╚Š┼─żŽCuź’źżźõ─║┼└żŪżõżõ╦─żķżÓżŌż╬ż╬ĪóżĮż╬╬╠ż“žōżķż╣ż│ż╚żŪČ╣źįź├ź┴ż╦×┤▒■ż╣żļĪŻ

┐▐2ĪĪCuź’źżźõż“└▄¶öźčź├ź╔ż╦╗╚ż”ĪĪĮąųZĪ¦Invensas

Cu ź▄ź¾źŪźŻź¾ź░żŽż╣żŪż╦╝┬└ėż╬żóżļČ\Įčż╦ż╩ż├żŲż¬żĻĪó┘J┘Tż╬ź▄ź¾ź└ż“╗╚ż©żļż┐żß┐Ęż┐ż╩└▀×ó┼Ļ½@żŽ═ūżķż╩żżĪŻ└▄¶öż╣żļ╚Š┼─ź▄Ī╝źļż╦×┤żĘżŲĪóCuź’źżźõż¼źŌĪ╝źļź╔█`╗ķż½żķ┤ķż“ĮążĘżŲżżżļŗ╩¼ż╬╣ŌżĄżŽż’ż║ż½0.1mm(┐▐2)ĪŻż│żņż“╝┬ĖĮż╣żļż┐żßż╦ĪóźšźŻźļźÓźóźĘź╣ź╚ż╬źŌĪ╝źļźŪźŻź¾ź░Č\Įčż“╗╚ż├żŲżżżļ(╗▓╣═½@╬┴1)ĪŻż│żņżŽ█`╗ķżŪźŌĪ╝źļźŪźŻź¾ź░ż╣żļ╗■ż╦▀`Ę┐└Łż“╬╔ż»ż╣żļż┐żßż╦źšźŻźļźÓż“ČŌĘ┐Ŗõż╦─źż├ż┐ĖÕż╦█`╗ķżŪź┴ź├źūż╬╝■żĻż“╦■ż┐żĮż”ż╚żżż”żŌż╬ĪŻźŌĪ╝źļźŪźŻź¾ź░╗■ż╦żŽCuź’źżźõż¼źšźŻźļźÓż“Ų═żŁ╗╔ż╣Ę┴ż╦ż╩żĻĪóźšźŻźļźÓż“Į³ĄŅżĘż┐ĖÕĪó┐▐2ż╬żĶż”ż╦▐kŗż¼¤²żŁĮążļżĶż”ż╦ż╩żļĪŻ

ż│ż╬źčź├ź▒Ī╝źĖż“╗╚ż├ż┐╣ŌÅ]źßźŌźĻż╚źĒźĖź├ź»ż╬PoPźčź├ź▒Ī╝źĖżŽ2014ŃQż┤żĒż½żķ┼ąŠņżĘĪóTSVż╦żĶżļź’źżź╔IOźčź├ź▒Ī╝źĖżŽ2016ŃQ░╩æTż╦ż╩żļż╚źżź¾ź┘ź¾źĄź╣żŽż▀żŲżżżļĪŻ

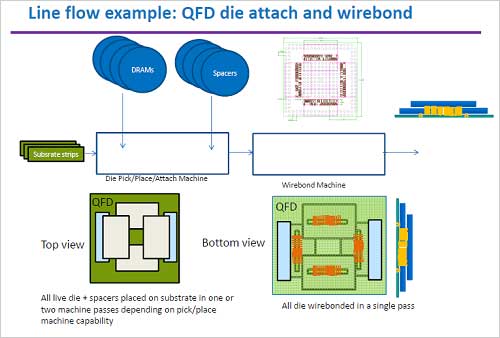

żŌż”▐kż─ż╬Č\ĮčżŪżóżļDRAMźŌźĖźÕĪ╝źļż╬─Ńź│ź╣ź╚Ī”Š«╝┬äóĀC└čż╬Č\ĮčżŪżŽĪóQFDĪ╩Quad Face DownĪ╦ż╚Ō}żążņĪó17mmĪ▀17mmĪ▀1mm(Ė³)ż╬źčź├ź▒Ī╝źĖż╦4Ė─ż╬DRAMż“╔§┘Vż╣żļĪŻ“£═Ķż╬ź╣ź┐ź├ź»Č\ĮčżŪ4ĮŚż╬DRAMź┴ź├źūż“─_ż═żļŠņ╣ńż╦żŽĪóDRAMź┴ź├źūĪ▄ź╣ź┌Ī╝źĄż╦ź’źżźõź▄ź¾źŪźŻź¾ź░żĘżŲ┤łż╚└▄¶öżĘż┐ĖÕĪó2ĮŚų`░╩æTżŌDRAMź┴ź├źū+ź╣ź┌Ī╝źĄż“╝ĪĪ╣ż╦─_ż═Īóź’źżźõĪ╝ź▄ź¾ź╔Īóż╚żżż”Š}Įńż“źĘĪ╝ź▒ź¾źĘźŃźļż╦╣įż’ż╩ż▒żņżąż╩żķż╩ż½ż├ż┐ĪŻ╣®µćżŽ─╣ż»ż╩żķżČżļż“įuż╩żżĪŻź’źżźõź▄ź¾źŪźŻź¾ź░ż└ż▒żŪżŌ4öv╣įż”ĪŻ

┐▐3ĪĪDRAMź┴ź├źū4ĮŚż“ź’źżźõź▄ź¾źŪźŻź¾ź░1övżŪż╣ż▐ż╗żļĪĪĮąųZĪ¦Invensas

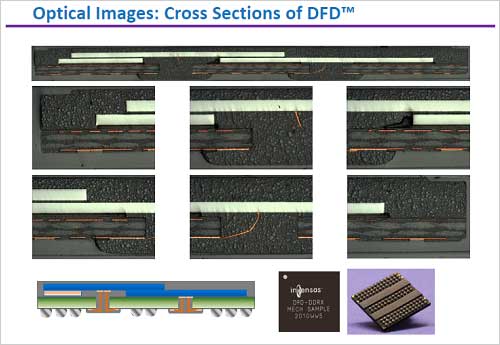

║Żövż╬QFDżŪżŽĪóDRAMź┴ź├źūż“źšź¦Ī╝ź╣ź└ź”ź¾ż╦żĘżŲ┤łæųż╦2ĮŚ▀`żĘżŲÅøżŁĪóź┴ź├źūż╚Ų▒żĖ╣ŌżĄż╦┬Ęż©żļż┐żßż╬ź╣ź┌Ī╝źĄżŌ2ĮŚÅøż»ĪŻżĮż╬æųż╦╩╠ż╬DRAMź┴ź├źūż“żõżŽżĻźšź¦Ī╝ź╣ź└ź”ź¾żŪ2ĮŚĪó┐▐3ż╬żĶż”ż╦Ū█Åøż╣żļĪŻź’źżźõź▄ź¾źŪźŻź¾ź░żŽżĮż╬ĖÕż╦ż▐ż╚żßżŲ╣įżżĪó▐k┼┘żŪ║čżÓĪŻ┤łż╬ĘĻż“─╠żĘżŲ╚┐×┤ĀCż╬źčź├ź╔ż╦ź’źżźõż“└▄¶öż╣żļĪŻéāĀCżŽ┐▐4ż╬żĶż”ż╦ż╩żļĪŻ╣®µćż¼ø]ż»├▒ĮŃż╩ż┐żßź│ź╣ź╚żŽŖWżżĪŻż▐ż┐Īóź┴ź├źūż╬─_ż╩żĻżŽ2ĮŚż└ż▒żŪżóżļż┐żßĪóźčź├ź▒Ī╝źĖµ£öüż“Ū÷ż»żŪżŁĪóÕX╩³Ügż¼╬╔żżĪŻżĄżķż╦ź▄ź¾źŪźŻź¾ź░ź’źżźõżŽø]ż»żŲ║čżÓż┐żßĪó╣ŌÅ]└Łē”żŽ═Ņż┴ż╩żżĪŻ

┐▐4ĪĪQFDČ\Įčż╬éāĀC┐▐ĪĪĮąųZĪ¦Invensas

źčź├ź▒Ī╝źĖź│ź╣ź╚żŽ“£═Ķż╬4ĮŚDRAMź╣ź┐ź├ź»ż╬Šņ╣ńż└ż╚1.56Ī┴1.67ź╔źļżŪżóżļż╬ż╦×┤żĘżŲĪóQFDżŽ0.66ź╔źļżŪ║čżÓĪóż╚źżź¾ź┘ź¾źĄź╣żŽĖ½└čż├żŲżżżļĪŻż┴ż╩ż▀ż╦1ĮŚż╬źĘź¾ź░źļź└źżźčź├ź▒Ī╝źĖżŽ0.2ź╔źļż└ż╚żżż”ĪŻ4ĮŚ╩¼żĶżĻżŌŖWżżĪŻ

ź”źļź╚źķźųź├ź»ż╬żĶż”ż╦źßźŌźĻźŌźĖźÕĪ╝źļż“ź▐źČĪ╝ź▄Ī╝ź╔ż╦─Š¤²ż▒żĘż╩ż▒żņżąż╩żķż╩żż├ō²ŗżŪżŽ╝┬äóæųż╬źßźĻź├ź╚żŌĮjżŁżżĪŻ┤łŪ█└■ż╬░·żŁövżĘż“┤▐żßż┐╝┬äóĀC└čż¼“£═ĶżĶżĻżŌ27%µć┼┘Š«żĄż»ż╩żļż┐żßĪó┼┼├ė═Ų╬╠ż“ĮjżŁż»żŪżŁPCż╬┼┼├ėŲ░║Ņ╗■┤ųż“äPżąż╣ż│ż╚ż¼żŪżŁżļĪŻ║┤ŲŻĢ■ż╦żĶżļż╚Īóż│ż╬QFDźčź├ź▒Ī╝źĖż└ż╚12┴žż╬źėźļź╔źóź├źū┤łżŪżŽż╩ż»ĪóŖW▓┴ż╩“£═Ķż╬12┴ž┤łż“╗╚ż©żļż╚żżż”ĪŻ

╗▓╣═½@╬┴

1. ╝ÕżżLow-k║Ó╬┴żõ║┘żżČŌź’źżźõż“╝ķżļ─Ń▒■╬üż╬┐ʿʿżźŌĪ╝źļź╔Č\Įč2008/07/14)