GlobalFoundriesĪó10ŃQ┤ųż╬finFET│½╚»ż“ĘążŲ14nmźūźĒź╗ź╣żŪ╝┬ĖĮżž

Īųż│żņż▐żŪźūźĒź╗ź╣└ż┬ÕżŽ2ŃQ┤ųż╬│½╚»┤³┤ųż“ĘążŲżŁż┐ż¼Īó20nmż½żķ14nmżžżŽ1ŃQżŪ┼■├ŻżŪżŁżĮż”ż└ĪūĪŻż│ż”Ėņżļż╬żŽĪóź░źĒĪ╝źąźļźšźĪź”ź¾ź╔źĻĪ╝ź║(GlobalFoundries)ż╬ź░źĒĪ╝źąźļź╗Ī╝źļź╣Ę¾ź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷æųĄķźąźżź╣źūźņźĖźŪź¾ź╚żŪżóżļMike NoonenĢ■ĪŻźóźĖźóĘQ├ŽżŪźßźŪźŻźóż╚ż╬źĒĪ╝ź╔źĘźńĪ╝ż“╣įżżĪó║ŪĮ¬├Žż╬±śĒ׿╚┼ņ»Bż╚ż╬┤ųżŪ┼┼ÅB▓±Ė½ż“╣įż├ż┐ĪŻ

┐▐1ĪĪGlobalFoundriesż╬ź░źĒĪ╝źąźļź╗Ī╝źļź╣Ę¾ź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷æųĄķźąźżź╣źūźņźĖźŪź¾ź╚żŪżóżļMike NoonenĢ■

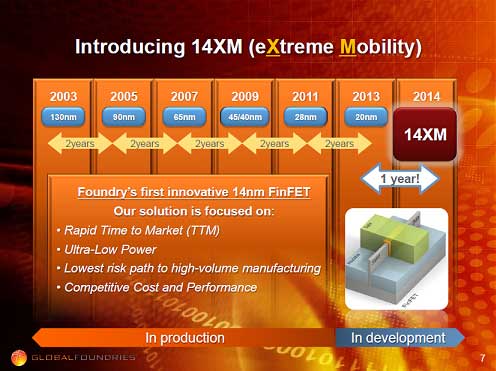

ż│żņż▐żŪĪóź░źĒĪ╝źąźļźšźĪź”ź¾ź╔źĻĪ╝ź║żŽ130nmż½żķ90nmĪ󿥿ķż╦65nmĪó45/40nmĪó28nmĪó20nmżžż╚ĘQ└ż┬ÕżžöĪ╣įż╣żļż╬ż╦2ŃQż“═ūżĘż┐(┐▐2)ĪŻ14nmźūźĒź╗ź╣ż╦żŽĮķżßżŲfinFETź╚źķź¾źĖź╣ź┐ż“Ų│Ų■ż╣żļż¼Īóź░źĒĪ╝źąźļźšźĪź”ź¾ź╔źĻĪ╝ź║żŽżĮżņż“10ŃQØiż½żķ│½╚»żĘżŲżŁż┐ż┐żßĪóŲ│Ų■żŽż½ż©ż├żŲ┴ßż▐żļż╚Ė½żŲżżżļĪŻØŖż╦ĪóIBMż╚ż╬ź│źķź▄źņĪ╝źĘźńź¾ż╦żĶżĻĪófinFET├▒öüż╬│½╚»ż╚źĘź╣źŲźÓźņź┘źļż╬SoC└▀╝Ŗż“īÖ├ōżŪżŁż┐ż│ż╚ż¼ĮjżŁżżż╚żĘżŲżżżļĪŻ

┐▐2ĪĪ14nmźūźĒź╗ź╣ż╬Ų│Ų■żŽ┴ßż▐żļĪĪĮąųZĪ¦GlobalFoundries

14nmźūźĒź╗ź╣żŪżŽĪófinFETź╚źķź¾źĖź╣ź┐ŗ╩¼ż╬║ŪŠ«Øó╦ĪżŽ14nmż└ż¼Īóź╚źķź¾źĖź╣ź┐░╩│░ż╬ŗ╩¼żŽ20nmż╬LPMźūźĒź╗ź╣ż“┴╚ż▀╣ńż’ż╗żļĪŻżĄżķż╦Īóż│żņż▐żŪż╬źūźņĪ╝ź╩ź╚źķź¾źĖź╣ź┐ż½żķfinFETź╚źķź¾źĖź╣ź┐żžż╬öĪ╣įż╦żŽFFMĪ╩Fin-Friendly MigrationĪ╦ż╚Ō}żųŲ╚śOż╬źļĪ╝źļż“║ŅżĻĪóź╣źÓĪ╝ź║ż╩öĪ╣įż“▓─ē”ż╦żĘżŲżżżļĪŻ

ż│ż╬Ų╚śOż╬źļĪ╝źļżŽĪó20nmźūźĒź╗ź╣ż“│½╚»ż╣żļ╗■ż╦Īó14nmż╬finFETźūźĒź╗ź╣ż“┴T╝▒żĘżŲźŌźĖźÕźķĪ╝▓Įż“┐▐ż├ż┐żŌż╬ż└ż╚żĘżŲżżżļĪŻöĪ╣įż╣żļż┐żßż╦ØŁ═ūż╩źļĪ╝źļżŽ┼÷Įķ7000żŌżóż├ż┐ż¼Īó20nmźūźĒź╗ź╣│½╚»ż╚Č”ż╦ż│ż╬źļĪ╝źļż╬┐¶ż“70ż╦žōżķżĘż┐ż╚żżż”ĪŻŲ▒╝ęż¼Ęeż─żĄż▐żČż▐ż╩ź╗źļźķźżźųźķźĻż╦FFMźļĪ╝źļż“┼÷żŲżŽżßĪóØŖ└Łäh▓┴żŌ╣įż├ż┐ĪŻżĄżķż╦ĪóŪ█ÅøĪ”Ū█└■ż╬źļĪ╝źļżŽ20nmźūźĒź╗ź╣ż“ź┘Ī╝ź╣ż╦żĘżŲż¬żĻĪóźķźżźųźķźĻż╬ź╗źļŲŌżŽź│ź¾źčź»ź╚ż╩Ū█└■ż╦żĘĪóź╗źļ-ź╗źļ┤ųż╬Ū█└■ĘąŽ®żŌ║ŪŠ«ż╦ż╩żļżĶż”ż╦żĘż┐ĪŻż│ż╬żĶż”ż╦żĘżŲĪó20nmż½żķ14nmźūźĒź╗ź╣żžż╬öĪ╣įż“═Ų░ūż╦żĘż┐ĪŻż│ż╬±T▓╠ĪóRTLżõź═ź├ź╚źĻź╣ź╚ż╬źņź┘źļżŪżŌ═Ų░ūż╦źūźĒź╗ź╣ż“öĪ╣įżŪżŁżļżĶż”ż╦ż╩ż├ż┐ĪŻ

Ų▒╝꿎28nmźūźĒź╗ź╣żŪHKMGĪ╩High-k Metal GateĪ╦ź▓Ī╝ź╚źšźĪĪ╝ź╣ź╚╣Įļ]ż“╗╚żżĪó20nmźūźĒź╗ź╣żŪżŽź▓Ī╝ź╚źķź╣ź╚╣Įļ]ż╦öĪ╣įż“ż╣żļż╚żĘżŲżżż┐ĪŻHKMGźūźĒź╗ź╣ż╬ź▓Ī╝ź╚źšźĪĪ╝ź╣ź╚żŽźßź┐źļ║Ó╬┴ż╦öU╠¾ż¼żóżļżŌż╬ż╬Īó“£═Ķż╬ź▌źĻźĘźĻź│ź¾źūźĒź╗ź╣ż╬ūā─╣└■ż╦żóżļż┐żß28nmźūźĒź╗ź╣żŽ╚µ│ė┼¬żõżĻżõż╣ż½ż├ż┐ĪŻź░źĒĪ╝źąźļźšźĪź”ź¾ź╔źĻĪ╝ź║żŽĪųż│żņż▐żŪż╦40╦³Ė─Ö┌ŠÅżĘżŲżŁż┐╝┬└ėż¼żóżļĪūż╚NoonenĢ■żŽĖ└ż”ĪŻź▓Ī╝ź╚źķź╣ź╚żŪ28nmźūźĒź╗ź╣ż“żõż├żŲżżż┐╚ŠŲ│öüźßĪ╝ź½Ī╝żŽż║żżżųż¾∙ZŽ½żĘżŲżżż┐ż╚Ė└ż’żņżŲżżżļĪŻżŪżŽĪóź░źĒĪ╝źąźļźšźĪź”ź¾ź╔źĻĪ╝ź║ż╦ż╚ż├żŲ20nmżŪĮķżßżŲź▓Ī╝ź╚źķź╣ź╚ż“Ęą┘xż╣żļż│ż╚ż╦ż╩żļŚlż└ż¼Īó║“ŃQżŽż╣żŪż╦ż│ż╬ź▓Ī╝ź╚źķź╣ź╚źūźĒź╗ź╣ż╬│½╚»żŪ┐’╩¼∙ZŽ½żĘżŲżŁż┐żķżĘżżĪŻżĘż½żĘĪóHKMGż╬ź╬ź”źŽź”ż“°QżßżŲżŁż┐ż┐żß20nmźūźĒź╗ź╣ż╬’L┤┘żŽ║ŪŖZŠ»ż╩ż»ż╩ż├żŲżŁż┐ż╚żĘżŲżżżļĪŻ

14nmźūźĒź╗ź╣żŪż╬źĻźĮź░źķźšźŻż╦żŽź└źųźļźčź┐Ī╝ź╦ź¾ź░Č\Įčż“╗╚ż”ż¼ĪóĪų─_═ūż╩ż│ż╚żŽź└źųźļźčź┐Ī╝ź╦ź¾ź░ż“╗╚ż”╣®µćż“żŪżŁżļż└ż▒Š»ż╩ż»żĘż┐ż│ż╚ż└Īūż╚NoonenĢ■żŽĮęż┘żļĪŻĪųż└ż½żķĪó20nmźūźĒź╗ź╣ż╚┴╚ż▀╣ńż’ż╗żļĪūż╬żŪżóżļĪŻź▐ź╣ź»┐¶żŽżŪżŁżļĖ┬żĻžōżķżĘż┐żżż┐żßĪó28nmźūźĒź╗ź╣ż╬╗■ż╚Ų▒══Īóż▐ż║Ū█└■┴Ē┐¶ż“„[─ĻżĘĪóżĮż╬ĖÕż╔ż”żõż├żŲź▐ź╣ź»┐¶ż“žōżķż╣ż½ż“╣═ż©ż╩ż¼żķźūźĒź╗ź╣└▀╝Ŗż“╣įż├żŲżżżļż╚żżż”ĪŻ

20nmż½żķ14nmżžż╬öĪ╣įżŽż’ż║ż½1ŃQż└ż¼Īó20nmż“ź╣źŁź├źūż╣żļŚlżŪżŽż╩żżĪŻĖ▄Ąęż╦żĶż├żŲ20nmźūźĒź╗ź╣ż“¶öż▒żļż│ż╚ż“╦ŠżÓĮĻżŌżóżĻĪó▓├ż©żŲ14nmż╬ĄężŌżóżĻĪóżĘżążķż»Ö┌ŠÅźķźżź¾ż“╩┬š`ż╦┴÷żķż╗żļż│ż╚ż╦ż╩żĻżĮż”ż└ĪŻ

14nmźūźĒź╗ź╣ż“╗╚ż├ż┐║ŪĮķż╬źŲĪ╝źūźóź”ź╚żŽ2013ŃQ¼Źż╦ż╩żļĖ½╣■ż▀żŪĪóżĮż╬╬╠ŠÅ╗■┤³ż¼14ŃQż╦ż╩żļż│ż╚ż½żķĪó2014ŃQż╦14nmż╚żżż”źĒĪ╝ź╔ź▐ź├źūż“ķWżżżŲżżżļĪŻ║ŪĮķż╬Ė▄Ąęż╦Ė■ż▒ż┐×æē俎źżź¾źŲźļż╚Ēö╣ńż╣żļ×æēäż╚ż╩żĒż”ż╚żżż”ĪŻ