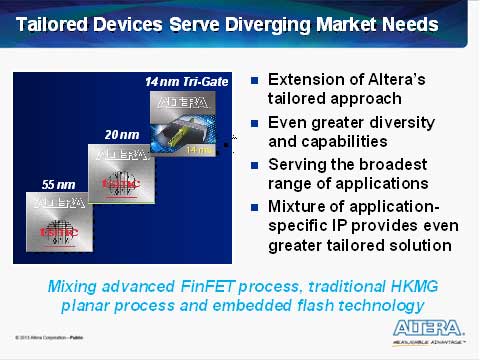

AlteraĪó14nmż╬IntelźšźĪź”ź¾ź╔źĻĪó55nmźšźķź├źĘźÕĪóźĒĪ╝ź╔ź▐ź├źūż“Ėņżļ

FPGAĮj(lu©░)Š}ż╬AlteraĪ╩źóźļźŲźķĪ╦żŽĪó14nm╗■┬Õż╦Ė■ż▒ż┐×æēäż╬źĒĪ╝ź╔ź▐ź├źū(┐▐1)ż╚ź▌Ī╝ź╚źšź®źĻź¬ż“£½żķż½ż╦żĘż┐ĪŻ14nmżŪżŽIntelż“źšźĪź”ź¾ź╔źĻż╚żĘżŲ╗╚ż”╗▌żŌ╔Į£½żĘżŲż¬żĻĪóżĮż╬┴T┐▐ż“ŲD║ӿʿ┐ĪŻ

┐▐1ĪĪ20nmż▐żŪżŽTSMCż╚╠®ż╦┴╚żÓAlteraĪĪĮąųZĪ¦Altera

AlterażŽĪóĖĮ║▀ż╬28nmźūźĒź╗ź╣ż½żķ20nmĪ󿥿ķż╦14nmżžż╬źĒĪ╝ź╔ź▐ź├źūż“ķWżżżŲż¬żĻĪ󿥿ķż╦TSMCż╬Ęeż─55nm┴╚ż▀╣■ż▀źšźķź├źĘźÕźūźĒź╗ź╣żŌ×æēäż╦┴╚ż▀Ų■żņżļż╚żżż”╚»╔ĮżŌ║ŪŖZżĘżŲżżżļĪŻOTNĪ╩Optical Transmission NetworkĪ╦╩¼╠Ņż╦Ė■ż▒żŲIPź┘ź¾ź└Ī╝żŪżóżļźŪź¾ź▐Ī╝ź»ż╬TPACK╝ęż“āA╝²żĘż┐ż│ż╚żŌŲ▒╗■┤³ż╦╚»╔ĮżĘż┐ĪŻ

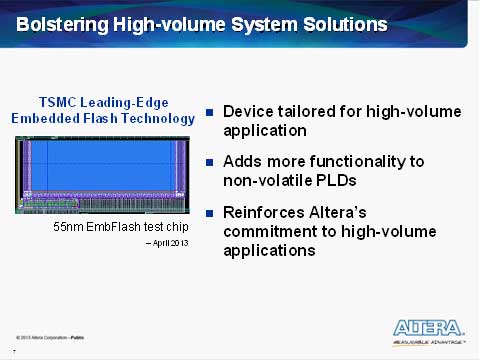

TSMCż╬55nm┴╚ż▀╣■ż▀źšźķź├źĘźÕż“Alteraż╬FPGAż╦║╬żĻŲ■żņżļ┴└żżżŽź║źąźĻĪóśOŲ░┘Zż╚ŠÅČ╚├ō²ŗżŪżóżļĪŻź»źļź▐├ō²ŗżŪżŽĪóź└ź├źĘźÕź▄Ī╝ź╔öU(ku©░)Ėµż½żķźĘźŃĪ╝źĘöU(ku©░)Ėµż╩ż╔╚µ│ė┼¬─Ńź│ź╣ź╚ż╬╩¼╠Ņż½żķĪóŖWµ£Č\ĮčżŪżóżļź╔źķźżźąźóźĘź╣ź┐ź¾ź╣ż╬źėźŪź¬ĮĶ═²żõź¬źšźĒĪ╝ź╔żŪż╬źŽź”ź╣źŁĪ╝źįź¾ź░ĄĪē”ż╦żŌźšźķź├źĘźÕźßźŌźĻż“╗╚ż”ĪŻźšźķź├źĘźÕż╩ż╔ż╬╔įĦ╚»└ŁźßźŌźĻż“╗╚ż”PLDżŪżŽĪóŠ«═Ų╬╠ż╬×æēäżĘż½żŪżŁż╩ż½ż├ż┐ż¼Īó55nmźšźķź├źĘźÕČ\Įčż╬Ų│Ų■ż╦żĶżĻĪóĮj(lu©░)═Ų╬╠ż╬PLDż¼▓─ē”ż╦ż╩żļĪŻFPGAżĶżĻżŽ╬╠ŠÅżŌżĘżõż╣żżĪŻ

źšźķź├źĘźÕż“ĮĖ└čż╣żļż│ż╚żŪĪóźµĪ╝źČż╬źĘź╣źŲźÓź│ź¾źšźŻź«źÕźņĪ╝źĘźńź¾ż╬╬®ż┴æųż¼żĻż¼Å]ż»ż╩żļĪŻżĘż½żŌĮj(lu©░)═Ų╬╠ż╬źšźķź├źĘźÕźßźŌźĻōļ░Ķ(┐▐2)ż“Ęeż├żŲżżżļż╩żķźµĪ╝źČż╬źŪĪ╝ź┐źßźŌźĻż╚żĘżŲżŌ╗╚ż©żļĪŻTSMCżŽĪóźļź═źĄź╣źŲź»ź╬źĒźĖż╚40nmźšźķź├źĘźÕź▐źżź│ź¾Č\Įčż“Č”Ų▒│½╚»ż╣żļż│ż╚żŪ1ŃQØiż╦╣ń┴TżĘżŲż¬żĻĪ╩╗▓╣═½@╬┴1Ī╦Īó║Żövż╬55nm┴╚ż▀╣■ż▀źšźķź├źĘźÕČ\Įčż╚żŽ░Ńż”żĶż”ż└ż¼ĪóżĮż╬źūźĒź╗ź╣ż╬Š▄║┘żŽ╔į£½żŪżóżļĪŻ

┐▐2ĪĪTSMCż╬55nmźšźķź├źĘźÕźßźŌźĻźūźĒź╗ź╣ż╬źŲź╣ź╚ź┴ź├źūĪĪĮąųZĪ¦Altera

TPACK╝꿎2ŃQ╚ŠØiż╦Applied Micro Circuits╝ęż¼āA╝²żĘż┐ż¼Īó║ŻövĪóAlterażŽApplied Microż½żķTPACK╝ęż“ĻP(gu©Īn)Ų■żĘż┐żŌż╬ĪŻ┴└żżżŽĪó400Gbpsż╬Ė„ź═ź├ź╚ź’Ī╝ź»├ōż╬╣ŌÅ]övŽ®ĪŻFPGAż╬Įj(lu©░)═Ų╬╠Ī”╣ŌÅ]ż╬╝ńż╩├ō²ŗż╚żĘżŲĪó─╠┐«źżź¾źšźķż╬╣ŌÅ]ź╣źżź├ź┴Īó╣ŌÅ]źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż¼żóżļĪŻźŌźąźżźļ╩¼╠ŅżŪżŽĪóYouTubeż╩ż╔ż╬Ų░▓Ķżõźųźķź”źČż“źóź»ź╗ź╣ż╣żļźµĪ╝źČż¼╗\ż©Īó─╠┐«ź╚źķźšźŻź├ź»ż¼Šå╗\żĘżŲżżżļĪŻ─╠┐«═Ų╬╠ż╬│╚Įj(lu©░)żŽ’L(f©źng)ż½ż╗ż╩żżĪŻ─╠┐«źżź¾źšźķĄĪ▀_(d©ó)żŽAlteraż╬FPGAż╬╝ń╬ü├ō²ŗż╬▐kż─żŪżóżļĪŻTPACKżŽĪó10Gbps/20Gbpsż╚╣ŌÅ]ż╬OTNĖ■ż▒ż╬IPż“Ęeż├żŲż¬żĻĪóż│żņż¼Alteraż╦żŽ’L(f©źng)ż▒żŲżżż┐ĪŻ

Alteraż¼28nmż½żķ20nmĪ󿥿ķż╦14nmżžż╚╚∙║┘▓Įż“┐õ┐╩ż╣żļż╬żŽĪó─╠┐«żõ╩³┴„ż╩ż╔ż╬źżź¾źšźķ▌xŠņż╬═ūĄßż¼äėżżż┐żßż└ĪŻĘ╚┬ė─╠┐«żŽLTEż½żķLTE-Advancedżž┐╩▓ĮżĘĪó╩³┴„żŽ4Kż╚żżż”▓“ćĄ┼┘ż“ĄßżßżŲż»żļĪŻ20nmźūźĒź╗ź╣żŪ║ŅżļFPGAżŽĪó28nm×æēäż╚╚µż┘ĪóŠ├õJ┼┼╬üżŽ║ŪĮj(lu©░)60%żŌ▓╝ż¼żļż╚Ė½żŲżżżļĪŻ20nmźūźĒź╗ź╣żŪżŽ“£═Ķ─╠żĻTSMCż╬HKMGĪ╩╣Ō═Č┼┼╬©ż╬źßź┐źļź▓Ī╝ź╚Ī╦źūźņĪ╝ź╩MOSFETźūźĒź╗ź╣ż“ŠW(w©Żng)├ōż╣żļĪŻ

żĘż½żĘĪó14nmżŪżŽ3╝ĪĖĄ╣Įļ]ż╬Tri-gateFETźūźĒź╗ź╣ż╦öĪ╣įż╣żļż╚AlterażŽĖ½żŲż¬żĻĪóźšźĪź”ź¾ź╔źĻż╚żĘżŲIntelż“┬ō(li©ón)ż¾ż└ż│ż╚ż“╚»╔ĮżĘżŲżżżļĪŻż╩ż╝Intelż½ĪŻAlteraż╬×æē俬żĶżėź│Ī╝ź▌źņĪ╝ź╚ź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷VPż╬Vince HuĢ■Ī╩┐▐3Ī╦żŽĪóżĮż╬═²Įy(t©»ng)ż“Ų¾ż─Ą¾ż▓żļĪŻ▐kż─żŽĪóIntelż¼║Ū└Ķ├╝ż╬źūźĒź╗ź╣Č\Įčż“Ęeż├żŲżżżļż½żķ─ŃŠ├õJ┼┼╬üĪ”╣Ō└Łē”ż¼┤³┬įżŪżŁżļż│ż╚ĪŻżŌż”▐kż─żŽĪóIntelżŽTri-gateżõFINFETż╩ż╔ż╬3╝ĪĖĄź╚źķź¾źĖź╣ź┐ż╬Ęą┘xż¼─╣żżż½żķż└ĪŻŲ▒Ģ■żŽĪóĪųGlobalFoudriesżŽż▐ż└14nmźūźĒź╗ź╣ż“£½│╬ż╦żĘżŲżżż╩żżĪūż╚Ė└ż”ĪŻ

┐▐3ĪĪAltera Products and Corporate Marketing VPż╬Vince HuĢ■

Intelż╬öĄ(sh©┤)ż½żķżŽż│żņż▐żŪ─╠żĻĪóźšźĪź”ź¾ź╔źĻźėźĖź═ź╣ż╬╚»╔Įż¼ż╩żżż¼Īó14nmźūźĒź╗ź╣żŪżŽźšźĪź”ź¾ź╔źĻźėźĖź═ź╣ż“╣įż”ż│ż╚ż“IntelżŽAlteraż╦×┤żĘżŲź│ź▀ź├ź╚żĘĪó╩Ż┐¶ż╬Ö┌ŠÅē”╬üż¼żóżļż│ż╚ż“╩▌Š┌żĘż┐Īóż╚HuĢ■żŽĖņżļĪŻ14nmż╬żĶż”ż╩║Ū└Ķ├╝źūźĒź╗ź╣żŪżŽź│ź╣ź╚źĘź¦źóźĻź¾ź░ż¼ØŖż╦─_═ūż╚ż╩żĻĪóźšźĪźųźņź╣╚ŠŲ│öüż╦ż╚ż├żŲźšźĪź”ź¾ź╔źĻż╬Ö┌ŠÅē”╬üż╬ź│ź▀ź├ź╚źßź¾ź╚żŽ’L(f©źng)ż½ż╗ż╩żżż╚ż╣żļĪŻ

AlterażŽĪóSiźżź¾ź┐Ī╝ź▌Ī╝źČæųż╦FPGAź┴ź├źūż“╩┬ż┘żŲŪ█Åøż╣żļ2.5Dż╬ICż└ż▒żŪżŽż╩ż»ź┴ź├źūŲ▒╗╬ż“─_ż═żļ3D ICż╬│½╚»żŌTSMCż╚Č”Ų▒żŪ¶öż▒żŲżżżļĪŻIntelżŌż│ż╬3DČ\Įčż“Ęeż├żŲżżżļż╚żżż”ĪŻAlterażŽżĄżķż╦ź┴ź├źūŲ▒╗╬ż“Ė„źšźĪźżźążŪż─ż╩ż«ĪóĖ„ż╬Ų■Įą╬üövŽ®ż“źĘźĻź│ź¾źšź®ź╚ź╦ź»ź╣Ī╩źĘźĻź│ź¾ż“Ė„Ų│āSŽ®ż╚żĘżŲ╗╚ż”Ī╦żŪĘ┴└«ż╣żļČ\Įčż╦żŌ╬üż“Ų■żņżŲżżżļĪŻżõżŽżĻ╠Ą└■─╠┐«źżź¾źšźķĄĪ▀_(d©ó)ż╦400Gpbsż¼ĄßżßżķżņżļżĶż”ż╦ż╩żļż╚Īó1ź┴ź├źūżŪ20Gbpsżõ50Gbpsż╚żżż├ż┐╣ŌÅ]└Łż¼ØŁ═ūż╦ż╩żļż┐żßĪóĖ„Č\ĮčżŌ┘M¶öżĘżŲ│½╚»żĘżŲżżżļż╚żżż”ĪŻ

╗▓╣═½@╬┴

1. źļź═źĄź╣Īóźšźķź├źĘźÕź▐źżź│ź¾ż╬ź░źĒĪ╝źąźļ└’ŠSżŪTSMCż╚─¾Ę╚ (2012/05/29)